1

Изобретение относится к вычислительной технике, в частности, к технике передачи быстродействующих сигналов по длинным линиям связи.

В современных вычислительных системах отдельные устройства объединяются в единый комплекс с помощью унифицированных систем связи - сопряжений (интерфейсов), включающих в себя унифицированные шины и унифицированные электронные схемы, управляющие прохождением сигналов по шинам сопряжения. При этом к одной линии связи, возбуждаемой задаюшим устройством, подключается большое число приемных устройств, распределенных вдоль линии.

Приемные устройства, распределенные вдоль линии, должны иметь высокий входной импеданс, чтобы не оказывать влияния на характеристический импеданс линии. Приемные устройства должны также иметь четкую пороговую точку срабатывания и обеспечивать примерно равный запас от помех для уровня «Лог. О и «Лог. 1 передаваемых сигналов. Кроме того, часто требуется подключать устройства к линии связи и отключать от нее Б соответствии с определенной последовательностью управляющих сигналов.

Известны приемные интегральные логические устройства для приема сигналов из линий связи, возбуждаемых от стандартных интегральных схем с транзисторно-транзисторной логикой (ТТЛ), содержащие входной эмиттерный повторитель и транзисторно-транзисторный логический элемент и позволяющие подключать до 20 приемных устройств к одной линии связи.

Однако известные интегральные приемные устройства имеют сравнительно невысокий входной импеданс, так как входной повторитель возбуждает непосредственно мощный выходной каскад. При этом входной ток, определяемый резистором в эмиттере входного повторителя, увеличивается при /увелцч тт входного напряжения.

Кроме того, известные схемы имеют малую температурную стабильность и большой разброс входных пороговых напряжений.

Целью изобретения является увеличение входного сопротивления и обеспечение стабильного порогового уровня.

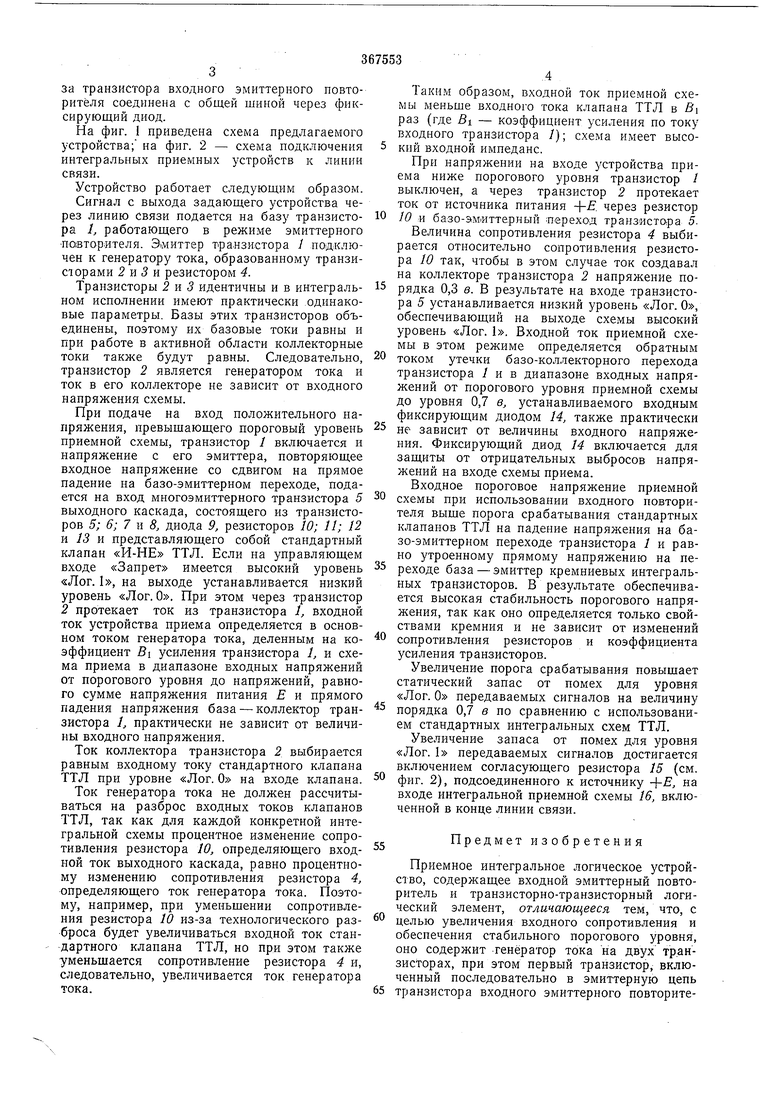

Это достигается тем, что в предлагаемое устройство введен генератор тока на двух транзисторах, первый из которых, включенный последовательно в эмиттерную цепь транзистора входного эмиттерного повторителя, соединен своим коллектором со входом транзисторно-транзисторного логического элемента, базой - с базой и коллектором второго транзистора генератора тока и через резистор - с шиной коллекторного питания, а база транзистора входного эмнттерного повторителя соединена с общей шиной через фиксирующий диод.

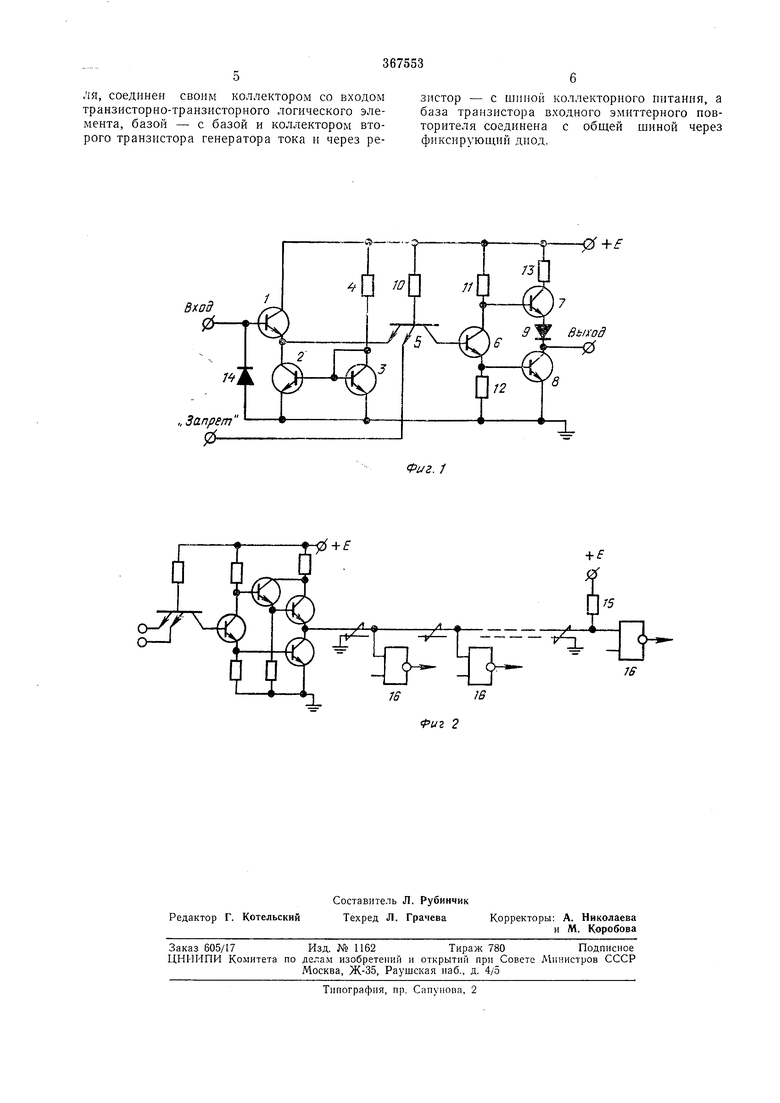

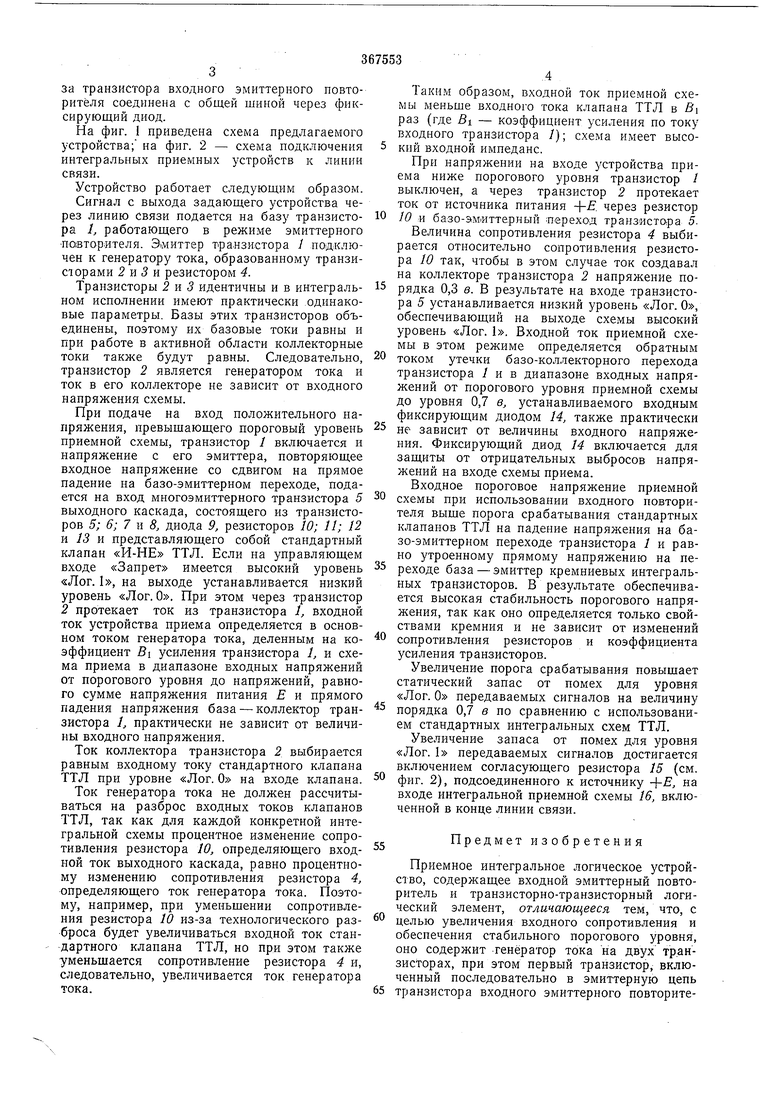

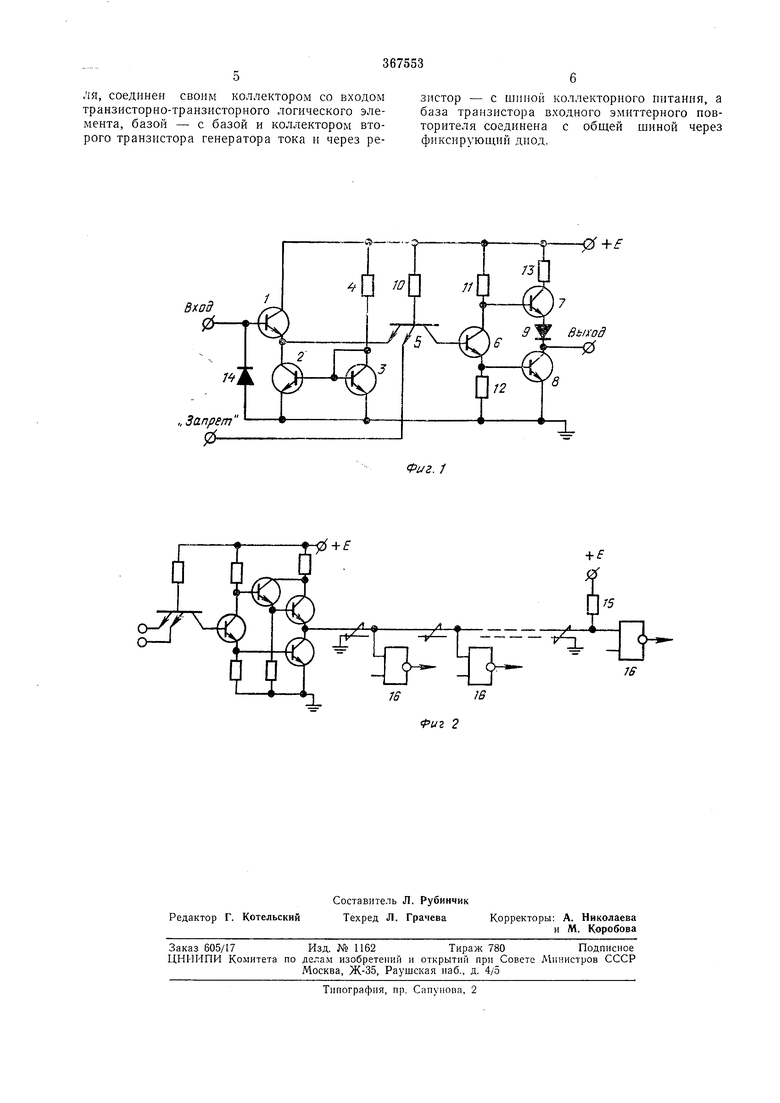

На фиг. 1 приведена схема предлагаемого устройства; на фиг. 2 - схема подключения интегральных приемных устройств к линии связи.

Устройство работает следующим образом.

Сигнал с выхода задающего устройства через линию связи подается на базу транзистора 1, работающего в режиме эмиттерного Повторителя. Э|миттер транзистора / подключен к генератору тока, образованному транзисторами 2 и 5 и резистором 4.

Транзисторы 2 и 5 идентичны и в интегральном исполнении имеют практически одинаковые параметры. Базы этих транзисторов объединены, поэтому их базовые токи равны и при работе в активной области коллекторные токи также будут равны. Следовательно, транзистор 2 является генератором тока и ток в его коллекторе не зависит от входного напряжения схемы.

При подаче на вход положительного папряжения, превышающего пороговый уровень приемной схемы, транзистор / включается и напряжение с его эмиттера, повторяющее входное напряжение со сдвигом на прямое падение на базо-эмиттерном переходе, подается на вход многоэмиттерного транзистора 5 выходного каскада, состоящего из транзисторов 5; 6; 7 и 8, диода 9, резисторов 10; 11; 12 н 13 и представляющего собой стапдартный клапан «И-НЕ ТТЛ. Если на управляющем входе «Запрет имеется высокий уровень «Лог. 1, на выходе устанавливается низкий уровень «Лог. О. При этом через транзистор 2 протекает ток из транзистора 1, входной ток устройства приема определяется в основном током генератора тока, деленным на коэффициент BI усиления транзистора 1, и схема приема в диапазоне входных напряжений от порогового уровня до напряжений, равного сумме напряжения питания Е и прямого падения напряжения база - коллектор транзистора Л практически не зависит от величины входного напряжения.

Ток коллектора транзистора 2, выбирается равным входному току стандартного клапана ТТЛ при уровне «Лог. О на входе клапана.

Ток генератора тока не должен рассчитываться на разброс входных токов клапанов ТТЛ, так как для каждой конкретной интегральной схемы процентное изменение сопротивления резистора 10, определяющего входной ток выходного каскада, равно процентному изменению сопротивления резистора 4, определяющего ток геператора тока. Поэтому, например, при уменьшении сопротивления резистора 10 из-за технологического разброса будет увеличиваться входной ток стандартного клапана ТТЛ, но при этом также уменьшается сопротивление резистора 4 и, следовательно, увеличивается ток генератора тока.

Таким образом, входной ток приемной схемы меньше входного тока клапана ТТЛ в В раз (где BI - коэффициент усиления по току входного транзистора /); схема имеет высокий входной импеданс.

При напряжении на входе устройства приема ниже порогового уровня транзистор / выключен, а через транзистор 2 протекает ток от источника питания +Я через резистор

10 и базо-эмитте.рный переход транзистора 5. Величина сопротивления резистора 4 выбирается относительно сопротивления резистора 10 так, чтобы в этом случае ток создавал на коллекторе транзистора 2 напряжение порядка 0,3 в. В результате на входе транзистора 5 устанавливается низкий уровень «Лог. О, обеспечивающий на выходе схемы высокий уровень «Лог. 1. Входной ток приемной схемы в этом режиме определяется обратным

током утечки базо-коллекторного перехода транзистора /ив диапазоне входных напряжений от порогового уровня приемной схемы до уровня 0,7 в, устанавливаемого входным фиксирующим диодом 14, также практически не зависит от величины входного напряжения. Фиксирующий диод 14 включается для защиты от отрицательных выбросов напряжений на входе схемы приема.

Входное пороговое напряжение приемной схемы при использовании входного повторителя выше порога срабатывания стандартных клапанов ТТЛ на падение напряжения на базо-эмиттерном переходе транзистора 1 и равно утроенному прямому напряжению на переходе база - эмиттер кремниевых интегральных транзисторов. В результате обеспечивается высокая стабильность порогового напряжения, так как оно определяется только свойствами кремния и не зависит от изменений

сопротивления резисторов и коэффициента усиления транзисторов.

Увеличение порога срабатывания повышает статический запас от помех для уровня «Лог. О передаваемых сигналов на величину

порядка 0,7 в по сравнению с использованием стандартных интегральных схем ТТЛ.

Увеличение запаса от помех для уровня «Лог. I передаваемых сигналов достигается включением согласующего резистора 15 (см.

фиг. 2), подсоединенного к источнику -{-Е, на входе интегральной приемной схемы 16, включенной в конце линии связи.

Предмет изобретения

Приемное интегральное логическое устройС1ВО, содержащее входной эмиттерный повторитель и транзисторно-транзисторный логический элемент, отличающееся тем, что, с целью увеличения входного сопротивления и обеспечения стабильного порогового уровня, оно содержит -генератор тока на двух транзисторах, при этом первый транзистор, включенный последовательно в эмиттерную цепь транзистора входного эмиттерного повторитеЛЯ, соединен своим коллектором со входом транзисторно-транзисторного логического элемента, базой - с базой и коллектором второго транзистора генератора тока и через резнстор - с шиной коллекторного питания, а база транзистора входного эмиттерного повторителя соединена с общей шиной через фиксирующий диод.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ДЛЯ ВОЗБУЖДЕНИЯ ДЛИННЫХ ЛИНИЙ | 1973 |

|

SU364106A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| Элемент для согласования насыщенных и ненасыщенных логических схем | 1972 |

|

SU438119A1 |

| Формирователь импульсов | 1979 |

|

SU788360A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| МИКРОМОЩНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ С ВЫСОКОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1999 |

|

RU2172064C2 |

| Элемент транзисторно-транзисторной ложки (его варианты) | 1985 |

|

SU1274149A1 |

| Мультиплексор | 1986 |

|

SU1378048A1 |

| ТТЛ-инвертор | 1984 |

|

SU1269252A1 |

| Интегральный преобразователь импульсов | 1987 |

|

SU1499449A1 |

-0 + f

+Е

3 W Выкод

Авторы

Даты

1973-01-01—Публикация