1

Изобретение относится к области запоминающих устройств (ЗУ).

Известно запоминающее устройство с произвольной одновременной выборкой переменного массива слов, содержащее модули памяти, связанные с первым шифратором, подключенным к регистру номера модуля, с блоком добавления единицы, подсоединенным к регистру номера ячейки, и с входным коммутатором, второй шифратор, подключенный к регистру формата записи, выходной коммутатор.

Однако в известном устройстве при росте количества потребителей или отсутствии кратности их форматов увеличивается необходимое количество модулей памяти при сохранении общего объема прочитываемой или записываемой информации; кроме того, в этом ЗУ нельзя использовать модули с технически предельной длиной слова.

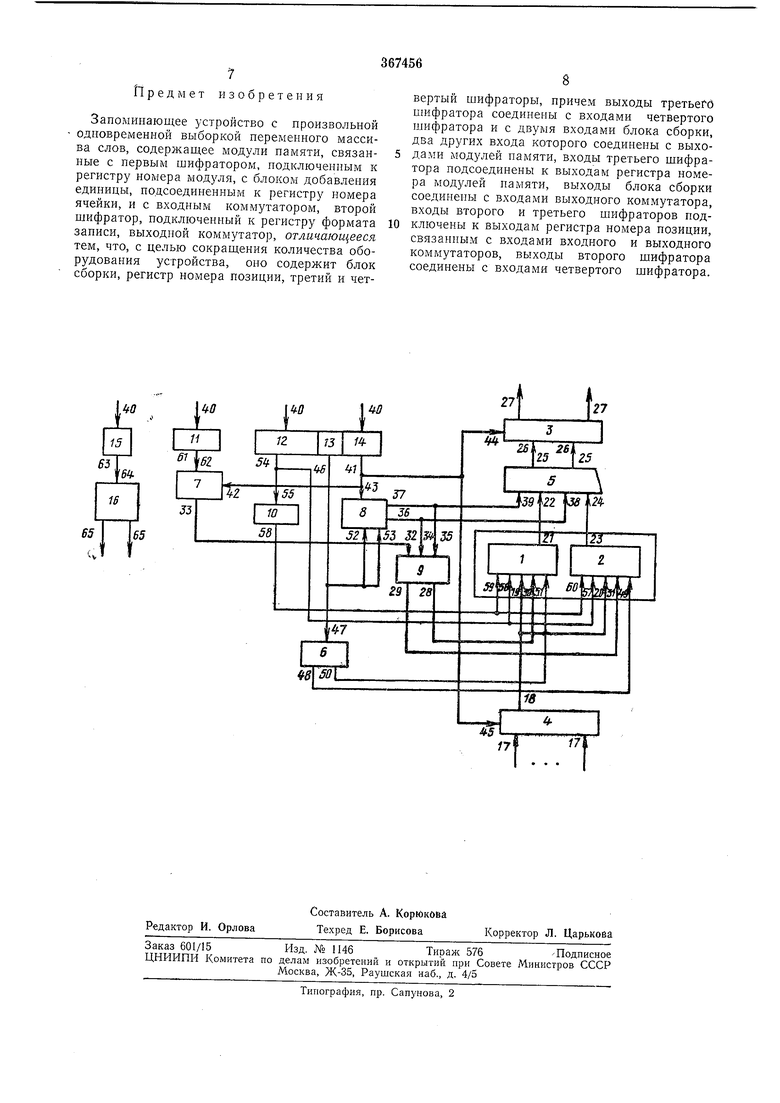

Предлагаемое ЗУ отличается от известного тем, что оно содержит блок сборки, регистр номера позиции, третий и четвертый шифраторы, причем выходы третьего шифратора соединены с выходами четвертого шифратора и с первыми входами блока сборки, вторые входы которого соединены с выходами модулей памяти, входы третьего шифратора подсоединены к выходам регистра номера модулей памяти, выходы блока сборки соединены с входами выходного коммутатора, входы второго и третьего шифраторов подключены к выходам регистра номера позиции, связанным с входами входного и выходного коммутаторов, выходы второго шифратора соединены с входами четвертого шифратора.

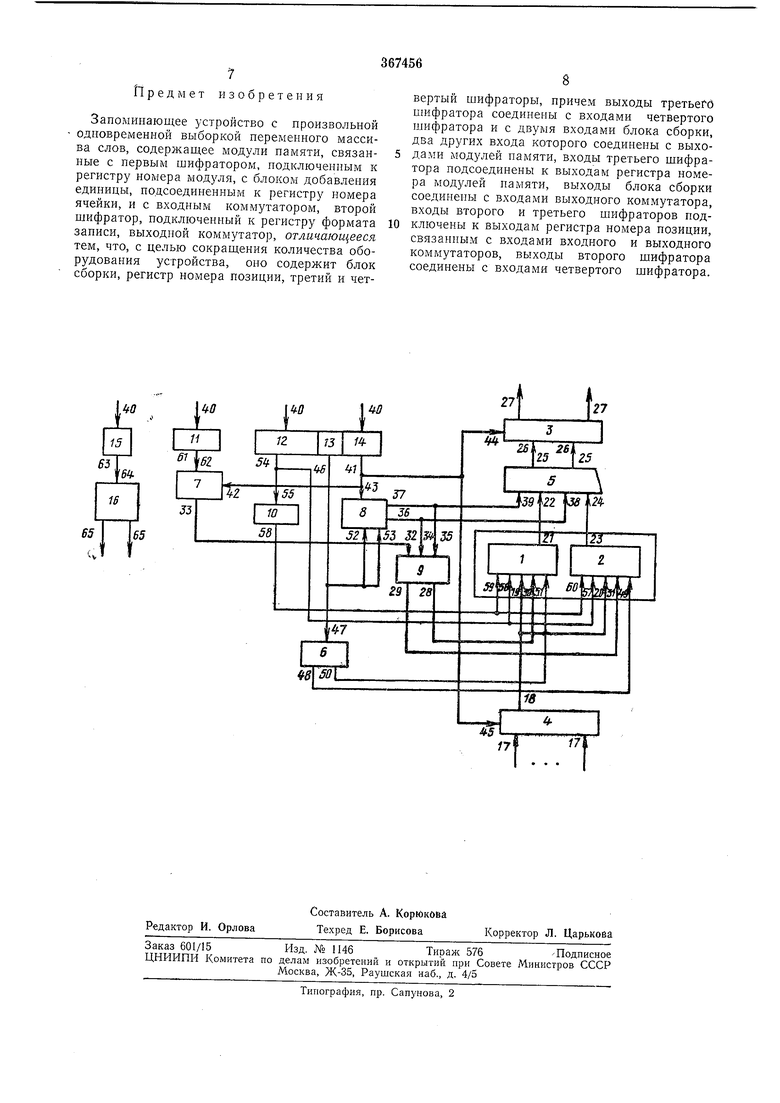

Это позволяет сократить требуемое количество оборудования устройства. На чертеже изображена блок-схема запоминающего устройства с произвольной одновременной выборкой переменного массива слов.

Устройство содержит модули 1 и 2 памяти, выходной коммутатор 3, входной коммутатор

4, блок 5 сборки, первый шифратор 6, второй шифратор 7, третий шифратор 8, четвертый шифратор 9, блок 10 добавления единицы, регистр // формата записи, регистр 12 номера ячейки, регистр 13 номера модуля, регистр

14 номера позиции, блок 15 запроса, генератор 16 задающих импульсов. На входы 17 входного коммутатора 4 подается информация, выход 18 его подключен к в.чоду 19 модуля / памяти и к входу 20 модуля 2. Выход 21

модуля 1 соединен с входом 22 блока сборки, а выход 23 модуля 2 памяти - с входом 24 блока сборки.

Выходы 25 блока 5 сборки поданы на входы 26 выходного коммутатора 3, выходы 27 которого являются выходами ЗУ.

Выходы 28 и 29 четвертого шифратора 9 соединены с входами 30, 31 модулей памяти 1 и 2 соответственно, входы 32 соединены с выходами 33 второго шифратора 7, а входы 34, 35 соединены соответственно с выходами 36, 37 третьего шифратора 8, которые, кроме того, соединены с входами 38 и 39 блока сборки.

Выходы 40 блока /5 занроса являются входами устройства и соединены с соответствуюшими выходами централизованного управления цифровой вычислительной системы или машины.

Выходы 41 регистра М номера позиции присоединены к входам 42 второго шифратора 7, входам 43 третьего шифратора 8, унравляюшим входам 44 выходного коммутатора 3 и управляюшим входам 45 входного коммутатора 4.

Выходы 46 регистра 13 номера модуля поданы на входы 47 первого шифратора 6, один выход 48 которого соединен с входом 49 модуля 2, а другой выход 50 - с входом 51 модуля /, и на входы 52, 53 третьего шифратора 8.

Выходы 54 регистра 12 номера ячейки поданы на входы 55 блока 10 добавления единицы, а также соответственно па входы 56, 57 модулей памяти 1 и 2.

Выходы 58 блока добавления единицы соединены с входами 59, 60 модулей 1, 2 соответственно.

Выходы 61 регистра 11 формата записи соединены с входами 62 второго шифратора 7.

Выходы 63 блока запроса и входы 64 генератора задаюших имнульсов соединены между собой, а выходы 65 генератора задающих импульсов служат для подачи синхроимпульсов на специальные входы ряда описанных блоков (не показаны).

В предлагаемом ЗУ осуш,ествляются чтение и запись переменного массива слов от одной до 2 нозиций; -максимальное число позиций, которое может быть затребовано за одпо обраш,ение к ЗУ. Это число должно быть целой степенью двух (i), поскольку адресация памяти при этом должна производиться с точностью до позиции.

Запрос обращения к устройству, формат затиси, номер ячейки, HOLvep модуля « номер позиции поступают па входы 40 блока запроса, регистра формата записи, регистра номера ячейки, регистра номера модуля и регистра номера позиции. Вместе с этой информацией на входы 17 входного коммутатора 4 поступает информация, предназначенная для записи в устройство, причем начальная (левая крайняя) позиция массива должна подаваться па левую крайпюю позицию входного коммутатора 4. Входпой коммутатор 4 производит кольцевой сдвиг информации, поданный на ее входы 17, вправо на величину номера позиции, который поступает на управляющие входы 45 входного коммутатора 4 с выходов

41 регистра 14 номера позиции, так, что па выходах 18 входного коммутатора 4 левая крайняя позиция входпой информации занимает позицию, номер которой совпадает с номером, указанным в регистре 14 номера позиции. Другие позиции входного массива информации занимают соответствующие следующие позиции, н в таком виде информация с выходов 18 входного коммутатора 4 подается па входы 19, 20 модулей памяти / и 2.

Формат входного коммутатора 4 (количество его входов или выходов) равен 2 позиций.

Входы 19, 20 модулей /, 2 памяти являются входами регистров заниси, на другие входы каждой позиции которых подается информация для регенерации с выходов регистров чтения; на входы 30, 31 модулей /, 2 памяти поступает с выходов 28, 29 четвертого шифратора 9 по сигналов (по одному на кажД)Ю позицию информации), наличие которых разрешает прием в соответствующие позиции регистра записи информации с выходов 18 входного коммутатора 4, а отсутствие - с выходов регистра чтения соответствующих позпций модуля памяти.

Выходы 54 регистра 12 помера ячейки подведепы к входам 56, 57 модулей памяти 1, 2, которые являются входами регистра адреса

соответствующего модуля. Другие входы 59 регистра адреса в модзле 1 и 60 ъ модуле 2 памяти соединены с входами 58 блока добавления единицы (регистр адреса, регистры чтения и записи и связи между ними на чертеже

не показаны).

Первый шифратор 6 вырабатывает на своих выходах 48, 50 два сигнала «меньше (), при наличии которых разрешается принять на выход блока сборки регистра адреса дополпительный адрес, а при отсутствии - основной адрес.

С выходами 21, 22 модулей памяти 1, 2 связаны позиции регистров чтения, в которые принимается информация, прочитанная из соответствующих ячеек модулей памяти. Эта информация с выходов 21, 22 подается па входы 23, 24 блока сборки. На его входы 39 и 38 поступает но сигналов. Сигнал с входа 39 разрешает пройти на выходы 25 блока сборки информации с соответствующей позиции входов 23, в то время как сигнал с входа 38 разрешает пройти па выходы 25 блока сборки информации с соответствующей позиции входов 24; при этом сигналы с входов 39, 38, управляющие одной позицией выходов 25 блока сборки, инверсны м.ежду собой. Сигналы на входы 38, 39 блока сборки подаются с выходов третьего шифратора 8.

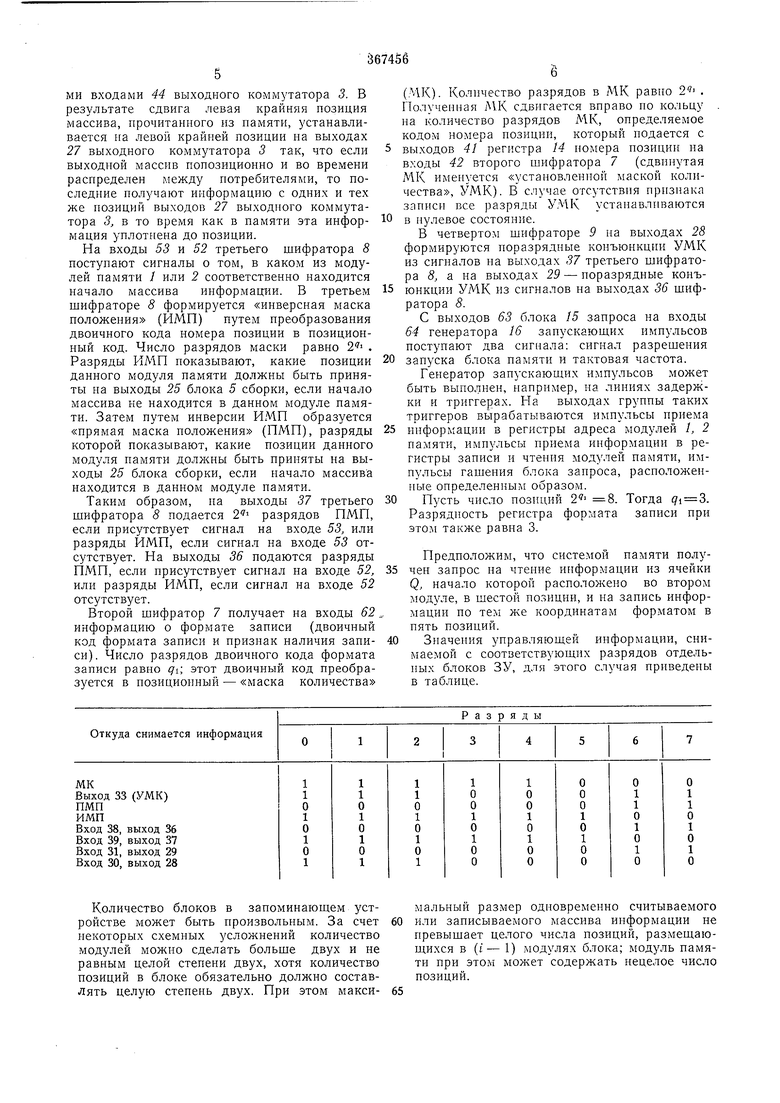

Все позиции выходов 25 подаются на соответствующие входы 26 позиций выходного коммутатора 3, осуществляющего кольцевой сдвиг информации, поступающей па входы 25, влево с точностью до одной позиции на величину, указанную в регистре номера позиции, выход 41 которого связан с управляющими входами 44 выходного коммутатора 3. В результате сдвига левая крайняя позиция массива, прочитанного из памяти, устанавливается на левой крайней позиции иа выходах 27 выходного коммутатора 5 так, что если выходной массив попозиционно и во времени распределен между потребителями, то последние получают информацию с одних и тех же позиций выходов 27 выходного коммутатора 3, в то время как в памяти эта информация уплотнена до позиции. На входы 53 и 52 третьего шифратора 8 поступают сигналы о том, в каком из модулей памяти / или 2 соответственно находится начало массива информации. В третьем шифраторе 8 формируется «инверсная маска положения (ИМП) путем преобразования двоичного кода номера позиции в позиционный код. Число разрядов маски равно . Разряды Р1МП показывают, какие позиции данного модуля памяти должны быть приняты на выходы 25 блока 5 сборки, если начало массива не находится в данном модуле памяти. Затем путем инверсии ИМП образуется «прямая маска положения (ПМП), разряды которой показывают, какие позиции данного модуля памяти должны быть приняты на выходы 25 блока сборки, если начало массива находится в данном модуле памяти. Таким образом, на выходы 37 третьего шифратора 8 подается разрядов ПМП, если присутствует сигнал на входе 53, или разряды ИМП, если сигнал на входе 53 отсутствует. На выходы 36 подаются разряды ПМП, если присутствует сигнал на входе 52, или разряды ИМП, если сигнал на входе 52 отсутствует. Второй шифратор 7 получает на входы 62 информацию о формате записи (двоичный код формата записи и признак наличия записи). Число разрядов двоичного кода формата записи равно ь этот двоичный код преобразуется в позиционный - «маска количества (МК). Количество разрядов в МК равно . Получепная МК сдвигается вправо но кольцу на количество разрядов МК, определяемое кодом номера позиции, который подается с выходов 41 регистра 14 номера позиции на входы 42 второго шифратора 7 (сдвинутая МК именуется «установленной маской количества, УМК). В случае отсутствия признака записи все разряды УМК устанавливаются в нулевое состояние. В четвертом шифраторе 9 на выходах 28 формируются поразрядные конъюнкции УМК из сигналов на выходах 37 третьего шифратора 8, а на выходах 29 - поразрядные конъюнкции УМК из сигналов на выходах 36 шифратора 8. С выходов 63 блока /5 запроса на входы 64 генератора 16 запускаюших импульсов поступают два сигнала: сигнал разрешения запуска блока памяти и тактовая частота, Генератор занускаюших импульсов может быть выполнен, например, на линиях задержки и триггерах. На выходах группы таких триггеров вырабатываются импульсы приема информации в регистры адреса модулей /, 2 памяти, имнульсы приема информации в регистры записи и чтения модулей памяти, импульсы гашения олока запроса, расположениые определенным образом. Пусть число позиций 8. Тогда . Разрядность регистра формата записи при этом также равна 3. Предположим, что системой памяти получей запрос на чтение информации из ячейки Q, начало которой расположено во втором модуле, в шестой позиции, и на запись информации но тем же координатам форматом в пять позиций. Значения управляюшей информации, снимаемой с соответствуюших разрядов отдельных блоков ЗУ, для этого случая приведеиы в таблице.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1985 |

|

SU1298762A2 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

| КОММУТАТОР LINK-ПОРТОВ | 2009 |

|

RU2405196C1 |

| Устройство для отображения информации на газоразрядной индикаторной панели | 1983 |

|

SU1119065A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037215C1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Запоминающее устройство | 1984 |

|

SU1185394A1 |

| Устройство для параллельной передачи информации | 1990 |

|

SU1795465A1 |

Количество блоков в запоминаюшем устройстве может быть произвольным. За счет иекоторых схемиых усложнений количество модулей можно сделать больше двух и не равным целой степени двух, хотя количество позиций в блоке обязательно должно составлять целую стенень двух. При этом максимальный размер одновременно считываемого или записываемого массива информации не превышает целого числа позиций, размешающихся в (i- 1) модулях блока; модуль памяти при этом может содержать нецелое число позиций.

П

редмет изооретения

Запоминающее устройство с произвольной одновремеиной выборкой переменного массива слов, содержащее модули памяти, связанные с первым шифратором, подключенным к регистру номера модуля, с блоком добавления единицы, подсоединенным к регистру номера ячейки, и с входным коммутатором, второй щифратор, подключенный к регистру формата записи, выходной коммутатор, отличающееся тем, что, с целью сокращения количества оборудования устройства, оно содержит блок сборки, регистр номера позиции, третий и четвертый шифраторы, причем выходы третьего шифратора соединены с входами четвертого шифратора и с двумя входами блока сборки, два других входа которого соединены с выходами модулей памяти, входы третьего шифратора подсоединены к выходам регистра номера модзлей памяти, выходы блока сборки соединены с входами выходного коммутатора, входы второго и третьего шифраторов подключены к выходам регистра номера позиции, связанным с входами входного и выходного коммутаторов, выходы второго шифратора соединены с входами четвертого шифратора.

Авторы

Даты

1973-01-01—Публикация