соединен с входом первого элемента НЕ, второй вход третьего элемента И подключен к выходу второго элемента ИЛИ, второй вход четвертого элемента И соединен с выходом третьего элемента ИЛИ, первый вход первого элемента ИЛИ соединен с вторыми входами элементов И первой группы, первый вход первого элемента И и второй вход первого элемента ИЛИ подключены к вторым входам элементов И второй группы, (Первый вход второго элемента И является третьим управляющим входом устройства, четвертым управляющим входом которого являются управляющие входы регистров адреса, первый вход второго элемента ИЛИ и управляющий вход регистра числа являются пятым управляющим входом устройства, шестым управляющим входом которого являются второй вход второго и первый вход третьего элементов ИЛИ, а седьмым управляющим входом - третий вход второго элемента И, второй вход третьего элемента ИЛИ и вторые входы первого и второго элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1984 |

|

SU1251175A1 |

| Запоминающее устройство | 1987 |

|

SU1443029A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

| Запоминающее устройство | 1978 |

|

SU769622A1 |

| Логическое запоминающее устройство | 1977 |

|

SU674101A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

| Устройство для назначения подканалов | 1984 |

|

SU1264189A1 |

| Запоминающее устройство | 1978 |

|

SU926712A1 |

ЗAПO MHAЮl EE УСТРОЙСТВО, содержащее регистры адреса, регистр числа, коммутатор, дешифраторы, шифратор, группы элементов И, группу элементов ИЛИ и накопитель, состоящий из основных ячеек памяти, адресные входы которых соединены с выходами первого регистра адреса, а разрядные входы и выходы подключены соответственно к одним из выходов регистра числа и к первым входам элементов И первой группы, выходы которых соединены с первыми входами элементов ИЛИ группы, вторые входы которых подключены к выходам элементов И второй группы, а выходы к входам коммутатора, выходы которого соединены с первыми входами элементов И третьей группы и одним из входов регистра числа, причем выходы второго регистра адреса соединены с входами первого дешифратора, выходы которого подключены к управляющим входам коммутатора, выходы второго дешифратора соединены с входами шифратора, первые входы элементов И второй группы и выходы элементов И третьей группы являются соответственно одним из информационных входов и выходов устройства, вторые входы элементов И первой и третьей групп объединены и являются первым управляющим входом устройства, вторым управляющим входом которого являются вторые входы элементов И второй группы, отличающееся тем, что, с целью повышения информационной емкости устройства, в него введены элементы И, элементы ИЛИ, элементы НЕ i и дополнительные ячейки памяти, адресные входы которых подключены (Л к выходам первого регистра адреса, с а разрядные входы и выходы - соответственно к другим выходам регистра числа и к одним из входов второго дешифратора, другие входы которого соединены с выходами второго регистра адреса, а вход синхронизаэо :л ции соединен с выходом первого элемента НЕ, причем Выход первого эле мента И соединен с входом второго :о л элемента НЕ, выход которого подключен к первым управляющим входам основных ячеек памяти, вторые управляющие входы которых соединены с выходами шифратора, выход второго элемента И соединен с входом третьего элемента НЕ, выход которого подключен к первым управляющим входам дополнительных ячеек памяти, вторые управляющие входы которых соединены с выходом третьего элемента И, первый вход которого подключен к выходу первого элемента ИЛИ и первому входу четвертого элемента И, выход которого

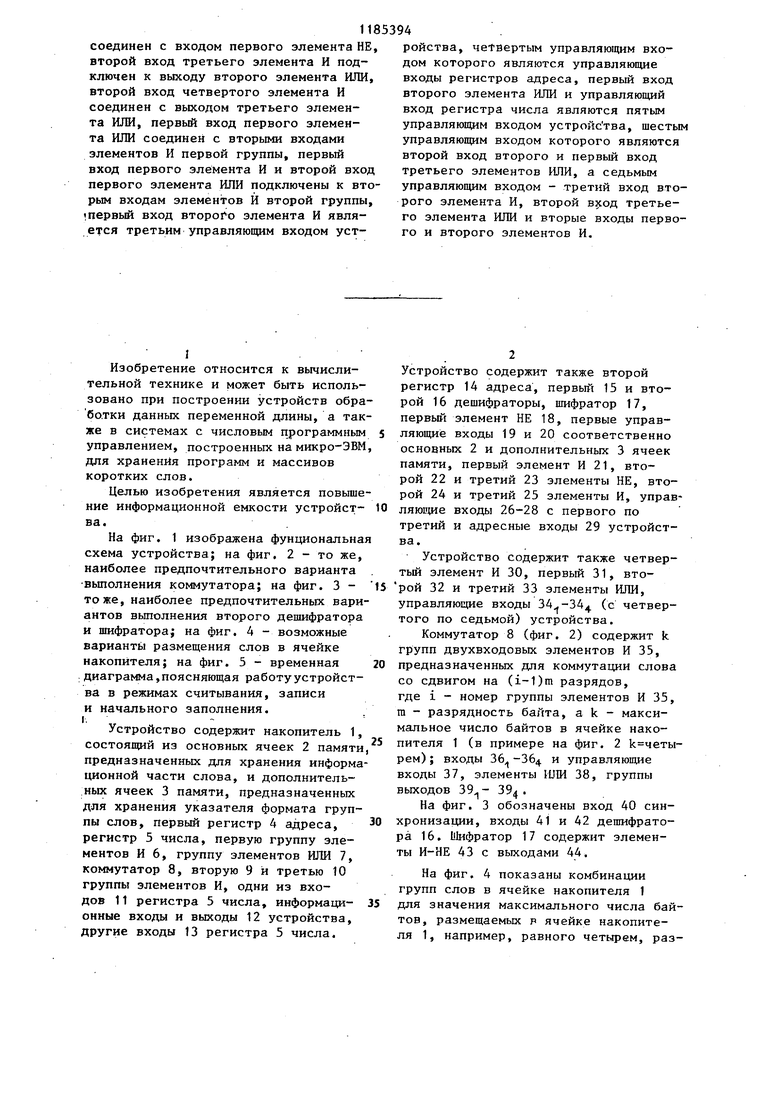

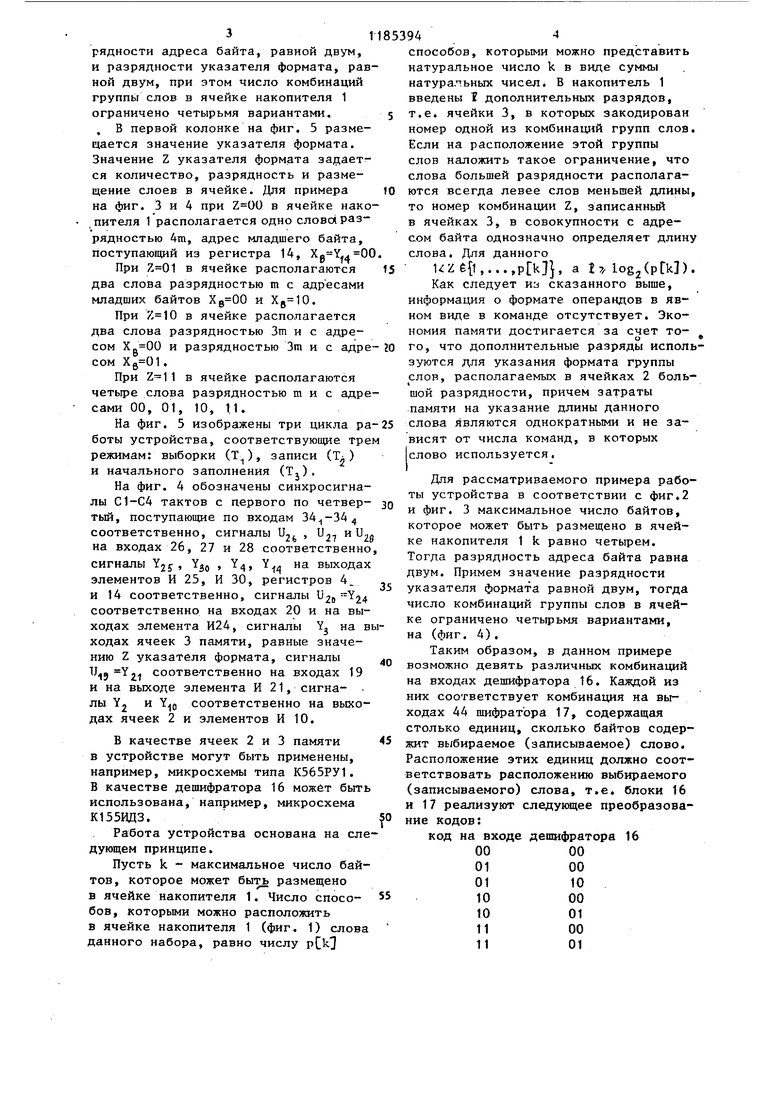

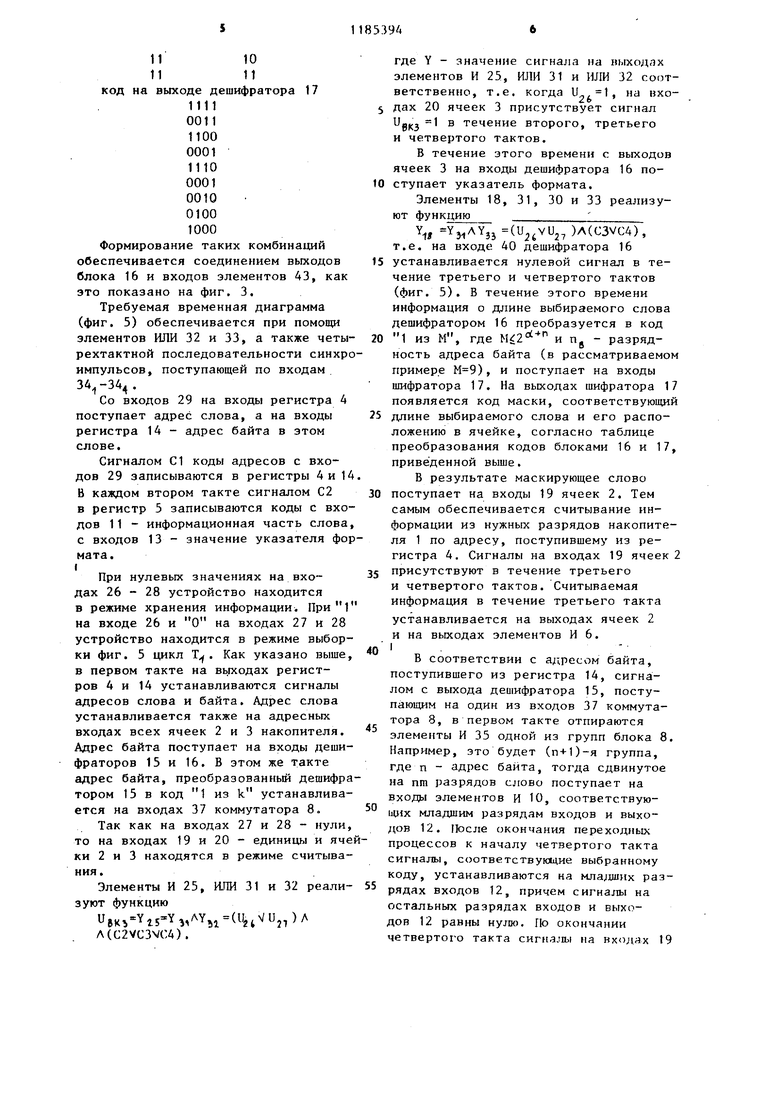

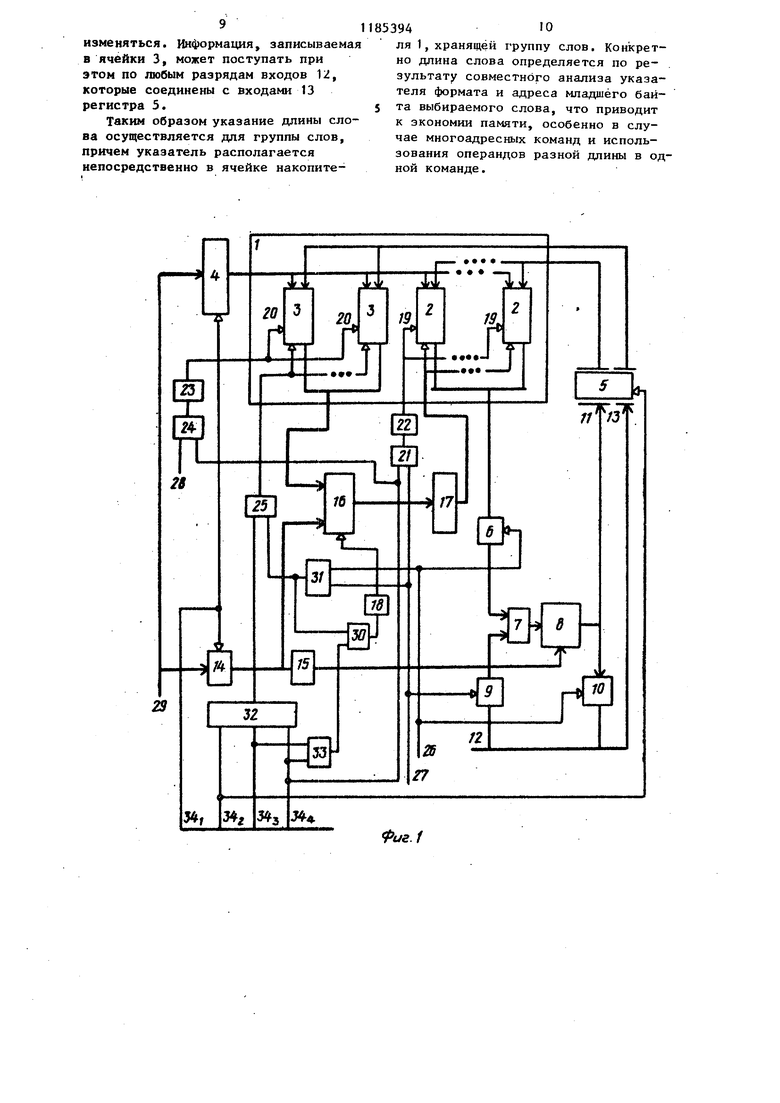

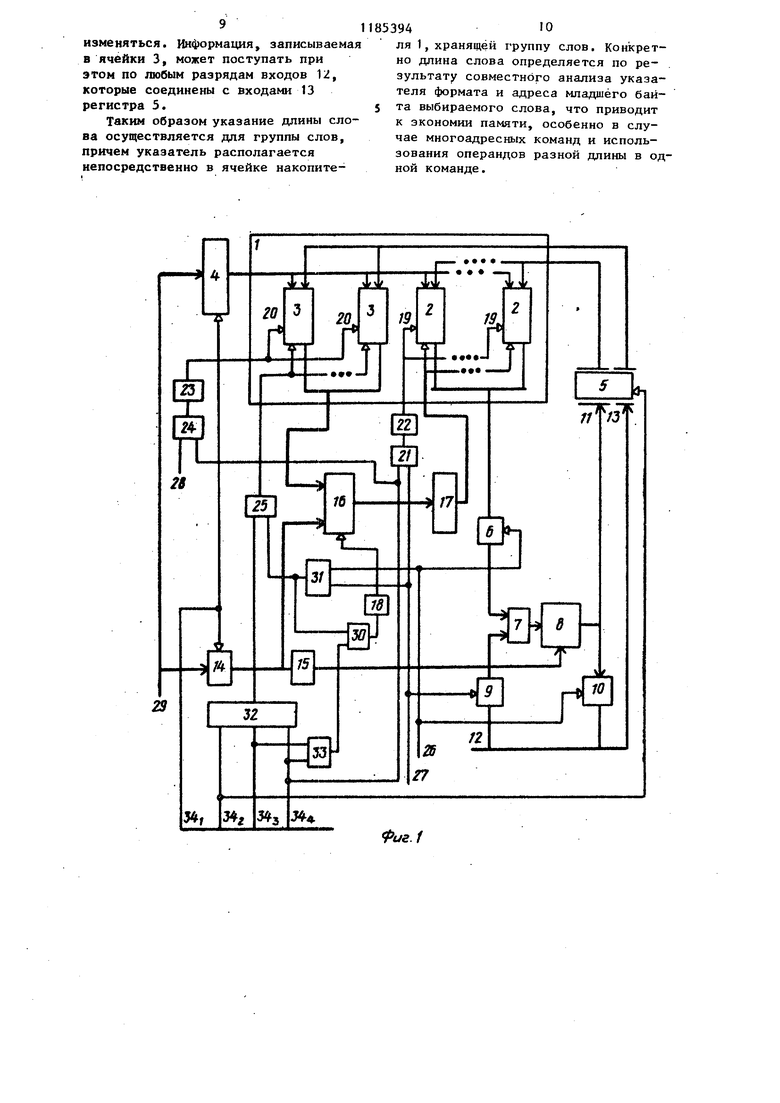

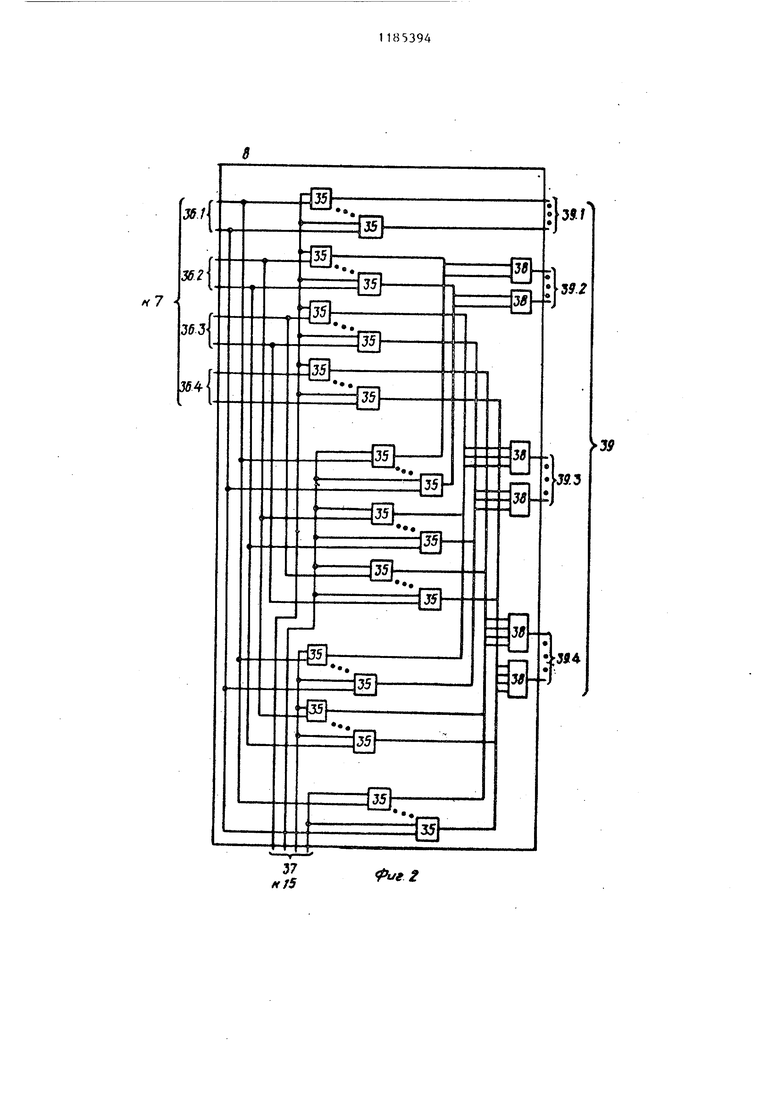

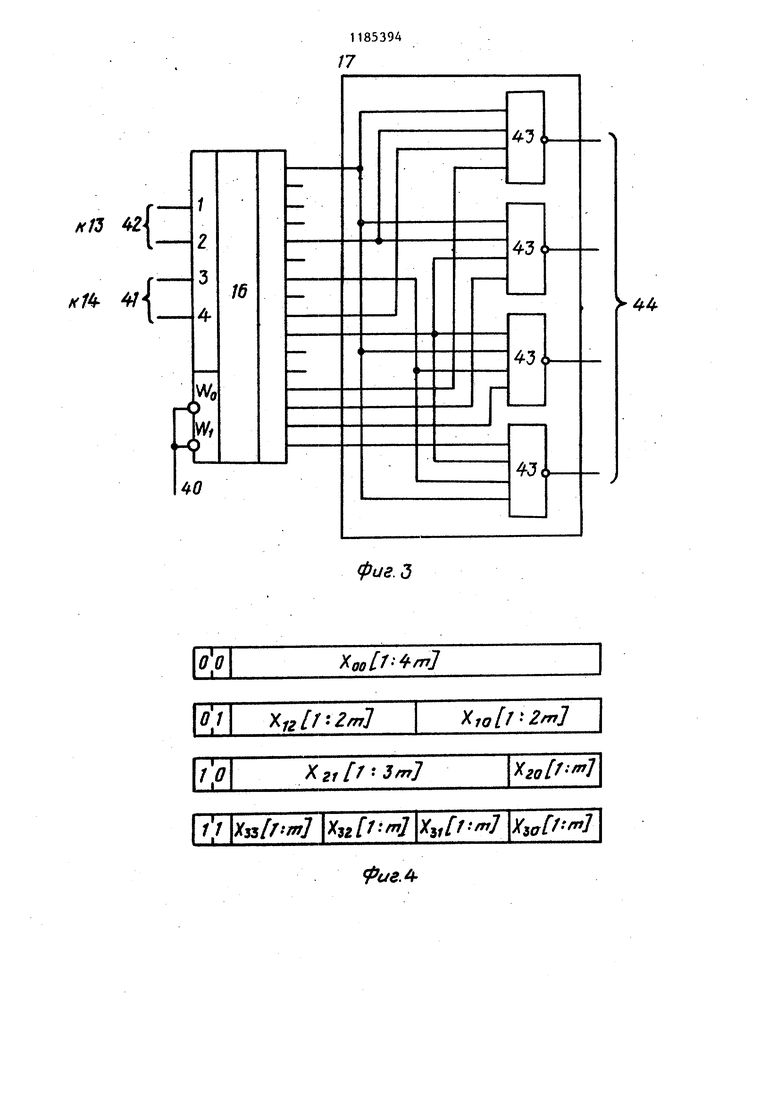

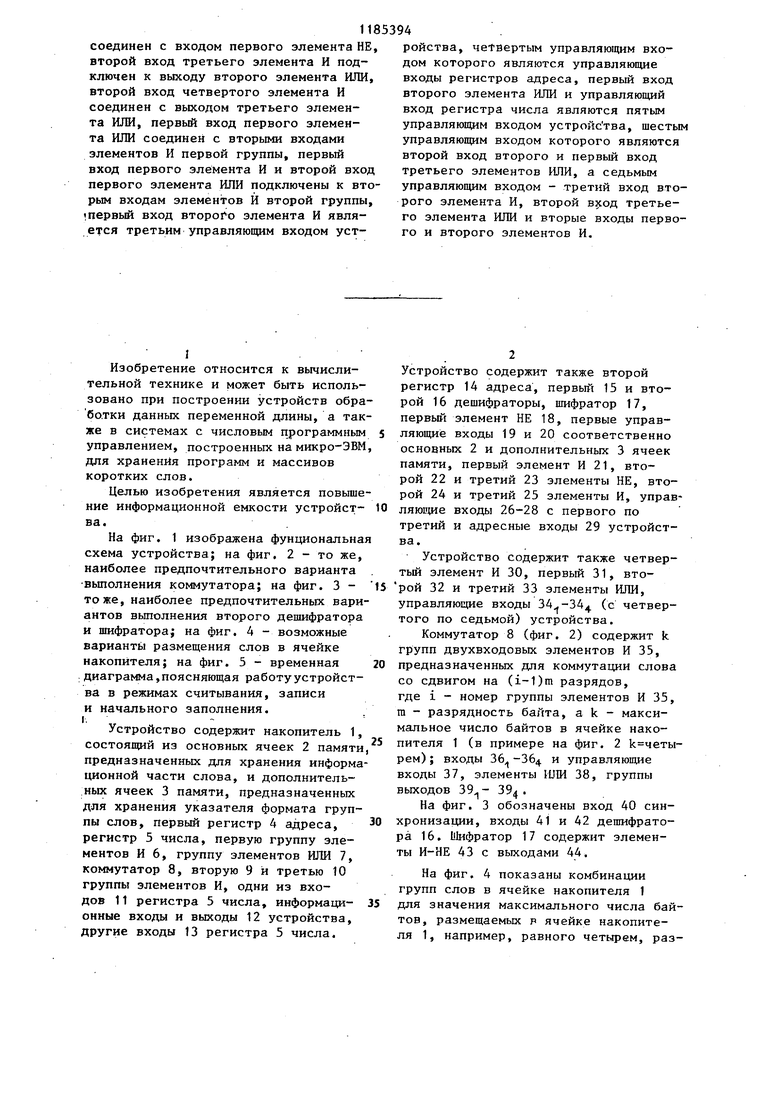

Изобретение относится к вычислительной технике и может быть использовано при построении устройств обра бо.тки данных переменной длины, а так же в системах с числовым программным управлением, построенных на микро-ЭВМ для хранения программ и массивов коротких слов. Целью изобретения является повьше ние информационной емкости устройства.. На фиг. 1 изображена фунционапьна схема устройства; на фиг. 2 - то же, наиболее предпочтительного варианта вьшолнения коммутатора; на фиг. 3 тоже, наиболее предпочтительных вари антов выполнения второго дешифратора и шифратора; на фиг. 4 - возможные варианть размещения слов в ячейке накопителя; на фиг. 5 - временная диаграмма,поясняющая работу устройства в режимах считывания, записи и начального заполнения. Устройство содержит накопитель 1, состоящий из основных ячеек 2 памяти предназначенных для хранения информа ционной части слова, и дополнительных ячеек 3 памяти, предназначенных для хранения указателя формата группы слов, первый регистр 4 адреса, регистр 5 числа, первую группу элементов И 6, группу элементов ИЛИ 7, коммутатор 8, вторую 9 и третью 10 группы элементов И, одни иэ входов 11 регистра 5 числа, информационные входы и выходы 12 устройства, другие входы 13 регистра 5 числа. Устройство содержит также второй регистр 14 адреса, первый 15 и второй 16 дешифраторы, шифратор 17, первый элемент НЕ 18, первые управляющие входы 19 и 20 соответственно основных 2 и дополнительных 3 ячеек памяти, первый элемент И 21, второй 22 и третий 23 элементы НЕ, второй 24 и третий 25 элементы И, управляюпдае входы 26-28 с первого по третий и адресные входы 29 устройства. Устройство содержит также четвертый элемент И 30, первый 31, второй 32 и третий 33 элементы ИЛИ, управляющие входы (с четвертого по седьмой) устройства. Коммутатор 8 (фиг. 2) содержит k групп двухвходовых элементов И 35, предназначенных для коммутации слова со сдвигом на (i-1)ra разрядов, где i - номер группы элементов И 35, га - разрядность байта, а k - максимальное число байтов в ячейке накопителя 1 (в примере на фиг. 2 и четырем); входы и управляющие входы 37, элементы ШШ 38, группы выходов 39. На фиг. 3 обозначены вход 40 синхронизации, входы 41 и 42 дешифратора 16. Шфратор 17 содержит элементы И-НЕ 43 с выходами 44. На фиг. 4 показаны комбинации групп слов в ячейке накопителя 1 для значения максимального числа байтов, размещаемых р ячейке накопителя 1, например, равного четырем, разрядности адреса байта, равной двум, и разрядности указателя формата, равной двум, при этом число комбинаций группы слов в ячейке накопителя 1 ограничено четырьмя вариантами.

В первой колонке на фиг. 5 размещается значение указателя формата. Значение Z указателя формата задается количество, разрядность и размещение слоев в ячейке. Для примера на фиг. 3 и 4 при в ячейке нако пителя 1 располагается одно слово разрядностью 4т, адрес младшего байта, поступающий из регистра 14, ,00

При в ячейке располагаются два слова разрядностью m с адресами младших байтов и .

При в ячейке располагается два слова разрядностью 3т и с адресом и разрядностью Зш и с адре сом .

При в ячейке располагаются четьфе слова разрядностью тис адресами 00, 01, 10, 1.1.

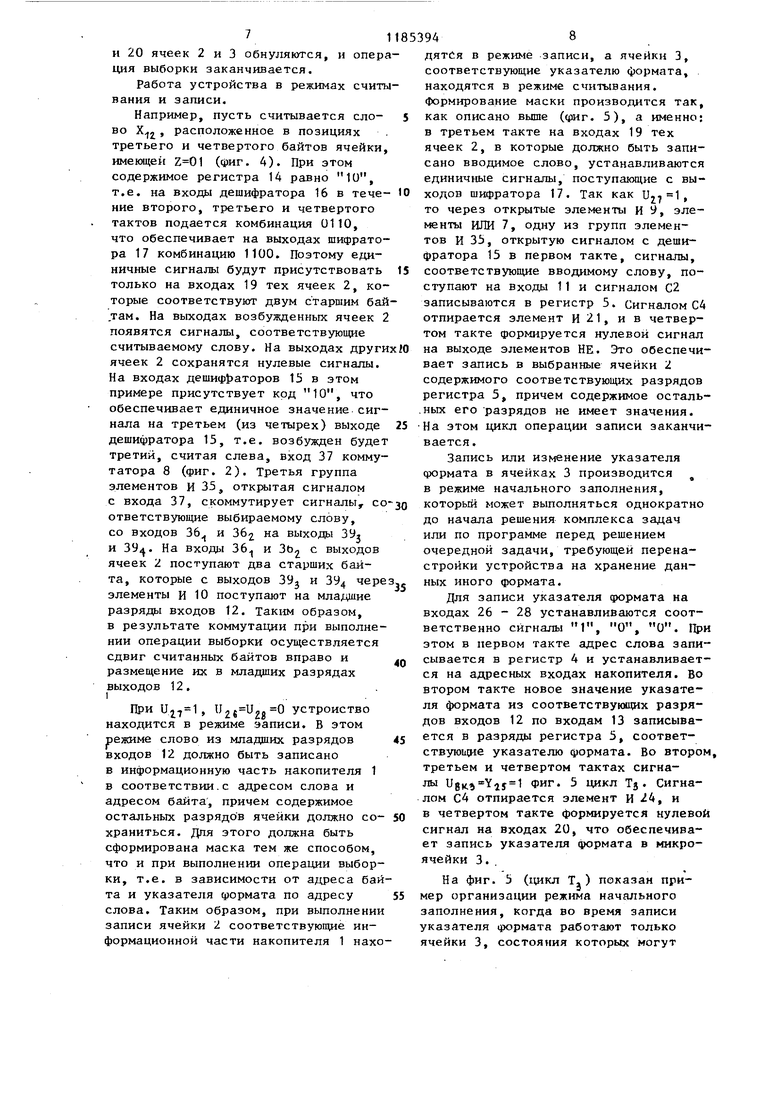

На фиг. 5 изображены три цикла ра боты устройства, соответствующие тре режимам: выборки (Tvj), записи (Ъ ) и начального заполнения (Т,).

На фиг. 4 обозначены синхросигналы С1-С4 тактов с первого по четвертый, поступающие по входам соответственно, сигналы Uj , 1)27 на входах 26, 27 и 28 соответственно сигналы Y25, , Y, Y. на выходах элементов И 25, И 30, регистров 4 и 14 соответственно, сигналы i4 соответственно на входах 20 и на выходах элемента И24, сигналы Y на входах ячеек 3 памяти, равные значению Z указателя формата, сигналы 2.1 соответственно на входах 19 и на выходе элемента И 21, сигна- лы Yj и соответственно на выходах ячеек 2 и элементов И 10.

В качестве ячеек 2 и 3 памяти в устройстве могут быть применены, например, микросхемы типа К565РУ1. В качестве дешифратора 16 может быть использована, например, микросхема К155ВДЗ.

Работа устройства основана на следующем принципе.

Пусть k - максимальное число байтов, которое может быть размещено в ячейке накопителя 1. Число способов, которыми можно расположить в ячейке накопителя 1 (фиг. 1) слова данного набора, равно числу

способов, которыми можно представить натуральное число k в виде суммы натуральных чисел. В накопитель 1 введены I дополнительных разрядов, т.е. ячейки 3, в которых закодирован номер одной из комбинашки групп слов Если на расположение зтой группы слов наложить такое ограничение, что слова большей разрядности располагаются всегда левее слов меньшей длины то номер комбинации Z, записанный в ячейках 3, в совокупности с адресом байта однозначно определяет длин слова. Для данного

UZ6{l,...,, а |7, logjCptk)

Как следует иа сказанного выще, информация о формате операндов в явном виде в команде отсутствует. Экономия памяти достигается за счет того, что дополнительные разряды исползуются для указания формата группы слов, располагаемых в ячейках 2 большой разрядности, причем затраты памяти на указание длины данного слова являются однократными и не зависят от числа команд, в которых слово используется.

Для рассматриваемого примера работы устройства в соответствии с фиг.2 и фиг. 3 максимальное число байтов, которое может быть размещено в ячейке накопителя 1 k равно четырем. Тогда разрядность адреса байта равна двум. Примем значение разрядности указателя формата равной двум, тогда число комбинаций группы слов в ячейке ограничено четырьмя вариантами, на (фиг. 4).

Таким образом, в данном примере возможно девять различных комбинаций на входах дешифратора 16. Каждой из них соответствует комбинация на выходах 44 шифратора 17, содержащая столько единиц, сколько байтов содержит выбираемое (записываемое) слово. Расположение этих единиц должно соответствовать расположению выбираемого (записываемого) слова, т.е. блоки 16 и 17 реализуют следующее преобразование кодов:

код на входе дешифратора 16

0000

0100 01 10 10 00

1001

1100 11 01

11 10 11 11

код на выходе дешифратора 17 1111 0011 1100 0001 1110 0001 0010 0100 1000

Формирование таких комбинаций обеспечивается соединением выходов блока 16 и входов элементов 43, как это показано на фиг. 3.

Требуемая временная диаграмма (фиг. 5) обеспечивается при помощи элементов ИЛИ 32 и 33, а также четырехтактной последовательности синхроимпульсов, поступающей по входам 34,-34.

Со входов 29 на входы регистра 4 поступает адрес слова, а на входы регистра 14 - адрес байта в этом слове.

Сигналом С1 коды адресов с входов 29 записываются в регистры 4 и 14 В каждом втором такте сигналом С2 в регистр 5 записываются коды с входов 11 - информационная часть слова, с входов 13 - значение указателя формата. I

При нулевых значениях на входах 26 - 28 устройство находится в режиме хранения информации. на входе 26 и О на входах 27 и 28 устройство находится в режиме выборки фиг. 5 цикл Т. Как указано выше, в первом такте на вьпсодах регистров 4 и 14 устанавливаются сигналы адресов слова и байта. Адрес слова устанавливается также на адресных входах всех ячеек 2 и 3 накопителя. Адрес байта поступает на входы дешифраторов 15 и 16. В этом же такте адрес байта, преобразованный дешифратором 15 в код 1 из k устанавливается на входах 37 коммутатора 8.

Так как на входах 27 и 28 - нули, то на входах 19 и 20 - единицы и ячеки 2 и 3 находятся в режиме считывания .

Элементы И 25, ИЛИ 31 и 32 реализуют функцию

,,AY,,(U,VU,,)A

A(C2VC3VC4).

где Y - значение сигнала на ныходах элементов И 25, ИЛИ 31 и Ш1И 32 соответственно, т.е. когда U 1, на входах 20 ячеек 3 присутствует сигнал Ug 1 в течение второго, третьего и четвертого тактов.

В течение этого времени с выходов ячеек 3 на входы дешифратора 16 поtO ступает указатель формата.

Элементы 18, 31, 30 и 33 реализуют функцию

1 (, )A(C3VC4), т.е. на входе 40 дешифратора 16 15 устанавливается нулевой сигнал в течение третьего и четвертого тактов (фиг. 5). В течение этого времени информация о длине выбираемого слова дешифратором 16 преобразуется в код 0 1 из М, где - разрядность адреса байта (в рассматриваемом примере ), и поступает на входы шифратора 17. На выходах шифратора 17 появляется код маски, соответствующий 5 длине выбираемого слова и его расположению в ячейке, согласно таблице преобразования кодов блоками 16 и 17, приведенной выше.

В результате маскирующее слово 0 поступает на входы 19 ячеек 2. Тем самым обеспечивается считывание информации из нужных разрядов накопителя 1 по адресу, поступившему из регистра 4. Сигналы на входах 19 ячеек 2 5 присутствуют в течение третьего И четвертого тактов. Считываемая информация в течение третьего такта

устанавливается на выходах ячеек 2 и на выходах элементов И 6.

0 „

В соответствии с адресом байта,

поступившего из регистра 14, сигналом с выхода дешифратора 15, поступающим на один из входов 37 коммутатора 8, в первом такте отпираются элементы И 35 одной из групп блока 8. Например, это будет (п+1)-я группа, где п - адрес байта, тогда сдвинутое на nm разрядов слово поступает на входы элементов И 10, соответстную11ЩХ младшим разрядам входов и выходов 12. После окончания переходньк процессов к началу четвертого такта сигналы, соответствующие выбранному коду, устанавливаются на младших разрядах входов 12, причем сигналы на остальных разрядах входов и выходов 12 равны нулю, Г1о окончании четвертого такта сигналы на входах 19 и 20 ячеек 2 и 3 обнуляются, и опер ция выборки заканчивается. Работа устройства в режимах считы вания и записи. Например, пусть считывается елово , расположенное в позициях третьего и четвертого байтов ячейки имеющей (фиг. 4). При этом содержимое регистра 14 равно 10, т.е. на входы дешифратора 16 в течение второго, третьего и четвертого тактов подается комбинация 0110, что обеспечивает на выходах шифратора 17 комбинацию 1100. Поэтому единичные сигналы будут присутствовать только на входах 19 тех ячеек 2, которые соответствуют двум старшим бай .там. На выходах возбужденных ячеек 2 появятся сигналы, соответствующие считываемому слову. На выходах други ячеек 2 сохранятся нулевые сигналы. На входах дешиф1 аторов 15 в этом примере присутствует код 10, что обеспечивает единичное значение сигнала на третьем (из четырех) выходе дешифратора 15, т.е. возбужден будет третий, считая слева, вход 37 коммутатора 8 (фиг. 2). Третья группа элементов И 35, открытая сигналом с входа 37, скоммутирует сигналы, co ответствующие выбираемому слову, со входов 36 и 36 на выходы ЗУа и ЗУ,. На входы 36 и 3b2 с выходов ячеек 2 поступают два старших байта, которые с выходов 39 и ЗУ4 чере элементы И 10 поступают на младшие разряды входов 12. TaKiiM образом, в результате коммутации при выполнении операции выборки осуществляется сдвиг считанных байтов вправо и размещение их в младших разрядах выходов 12. При 1 , устройство находится в режиме записи. В этом режиме слово из младших разрядов входов 12 должно быть записано в информационную часть накопителя 1 в соответствии.с адресом слова и адресом байта, причем содержимое остальных разрядов ячейки должно сохраниться. Для этого должна быть сформирована маска тем же способом, что и при выполнении операции выборки, т.е. в зависимости от адреса бай та и указателя формата по адресу слова. Таким образом, при выполнении записи ячейки 2 соответствующие информационной части накопителя 1 нахо дятся в режиме записи, а ячейки 3, соответствующие указателю формата, находятся в режиме считывания, формирование маски производится так, как описано выше (фиг. 5), а именно; в третьем такте на входах 19 тех ячеек 2, в которые должно быть записано вводимое слово, устанавливаются единичные сигналы, поступающие с выходов шифратора 17. Так как 1 , то через открытые элементы И У, элементы ИЛИ 7, одну из групп элементов И 35, открытую сигналом с дешифратора 15 в первом такте, сигналы, соответствующие вводимому слову, поступают на входы 11 и сигналом С2 записываются в регистр 5. Сигналом С4 отпирается элемент И 21, и в четвертом такте формируется нулевой сигнал на выходе элементов НЕ. Это обеспечивает запись в выбранные ячейки 2 содержимого соответствующих разрядов регистра 5, причем содержимое остальных его разрядов не имеет значения. На этом цикл операции записи заканчивается. Запись или изменение указателя формата в ячейках 3 производится , в режиме начального заполнения, который может выполняться однократно до начала решения комплекса задач или по программе перед решением очередной задачи, требующей перенастройки устройства на хранение данных иного формата. Для записи указателя формата на входах 26 - 28 устанавливаются соответственно сигналы 1, О, О. При этом в первом такте адрес слова записывается в регистр 4 и устанавливается на адресных входах накопителя. Во втором такте новое значение указателя формата из соответствующих разрядов входов 12 по входам 13 записывается в разряды регистра 5, соответствуюи1ие указателю формата. Во втором, третьем и четвертом тактах сигналы UgK, 1 фиг. 5 цикл Tj . Сигналом С4 отпирается элемент И 24, и в четвертом такте формируется нулевой сигнал на входах 20, что обеспечивает запись указателя формата в микроячейки 3. На фиг. 5 (lyiKn Т,) показан пример организации режима начального заполнения, когда во время записи указателя формата работают только ячейки 3, состояния которых могут

9

изменяться. Информация, записываема в ячейки 3, может поступать при этом по любым разрядам входов 12, которые соединены с входами 13 регистра 5.

Таким образом указание длины слова осуществляется для группы слов, причем указатель располагается непосредственно в ячейке накопите39410

ля 1, хранящей группу слов. Конкретно длина слова определяется по результату совместного анализа указателя формата и адреса младшего байта выбираемого слова, что приводит к экономии памяти, особенно в случае многоадресных команд и использования операндов разной длины в одной команде.

Фиг.1

ЗбА

.

jejj

3541

)

Р)

I

Ъ9.2 Ш

39

37 н}5

I-,,

A/j 4г

. «{;

А/4

Хда//- /Г77

ОО

Xr2// W

OJ

|y337/W Xy2 rf J Xsffr 7 |/3fy//W

1185394

У 44

фиг.д

игЛ

С1 С2 CJ С4

U26 U27

Уг$

Xr4

Z-Y,

УГ7

Uis-y i

У г УГО

иг. 5

| Запоминающее устройство | 1975 |

|

SU583475A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство | 1978 |

|

SU769622A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-10-15—Публикация

1984-05-21—Подача