гистра соединены с входами первого сдвигагеля и входами второго сдвигателя, выход которого

соединен с входами второго буферного ре гистра, выходы первого и второго буферных регистров соединены соответственно с входами второго и первого входных регистров, регистра результата и узлов управления сое динены через коммутатор с входами сумматора, регистры суммы и переносов соединены соответственно с входами первого и второго буферных регистров и первой и второй схем анализа нуля, выходы которых соеди нены с входами узла управления делением, выходы первого буферного регистра соединены также с входами третьего сдвигателя, выходы которого подключены к входам первого входного регистра, и с первыми входами узла логических операций, другие входы которого соединены с входами второго бу ферного регистра, а выходы подключены к входам первого входного регистра, при этом входы дешифраторов нулевых тетрад соеди. нены с выходами второго входного регистра, а выходы - с входами узла управления умножением,

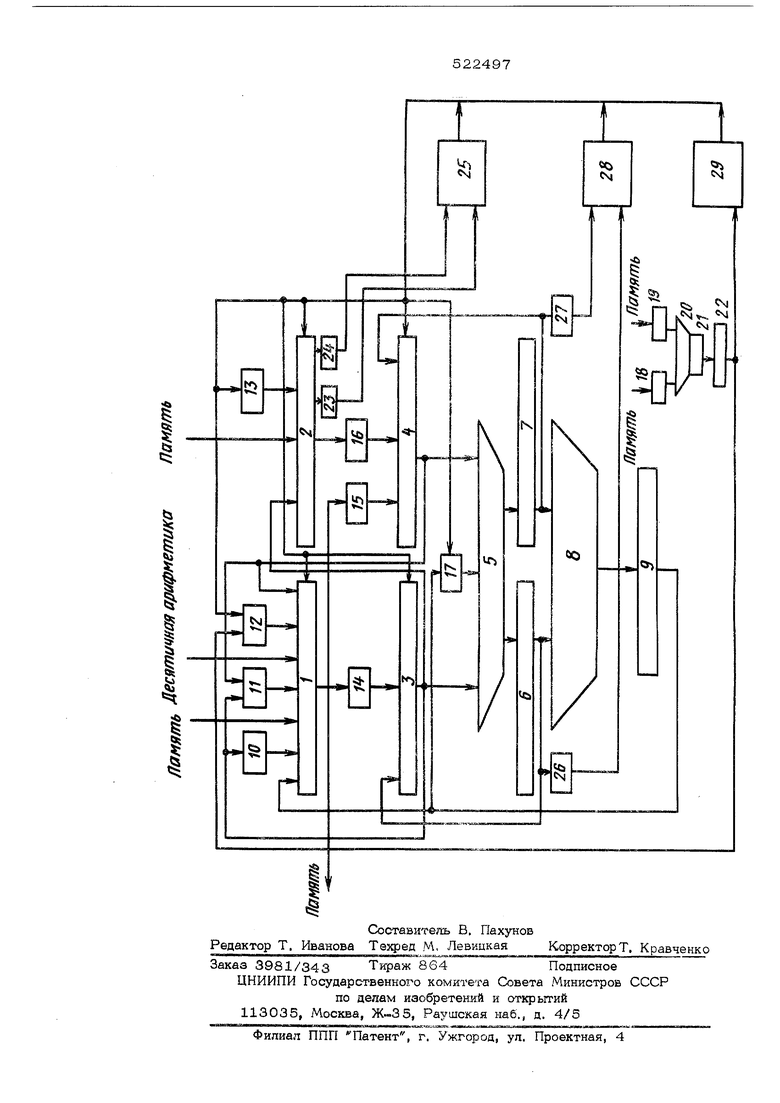

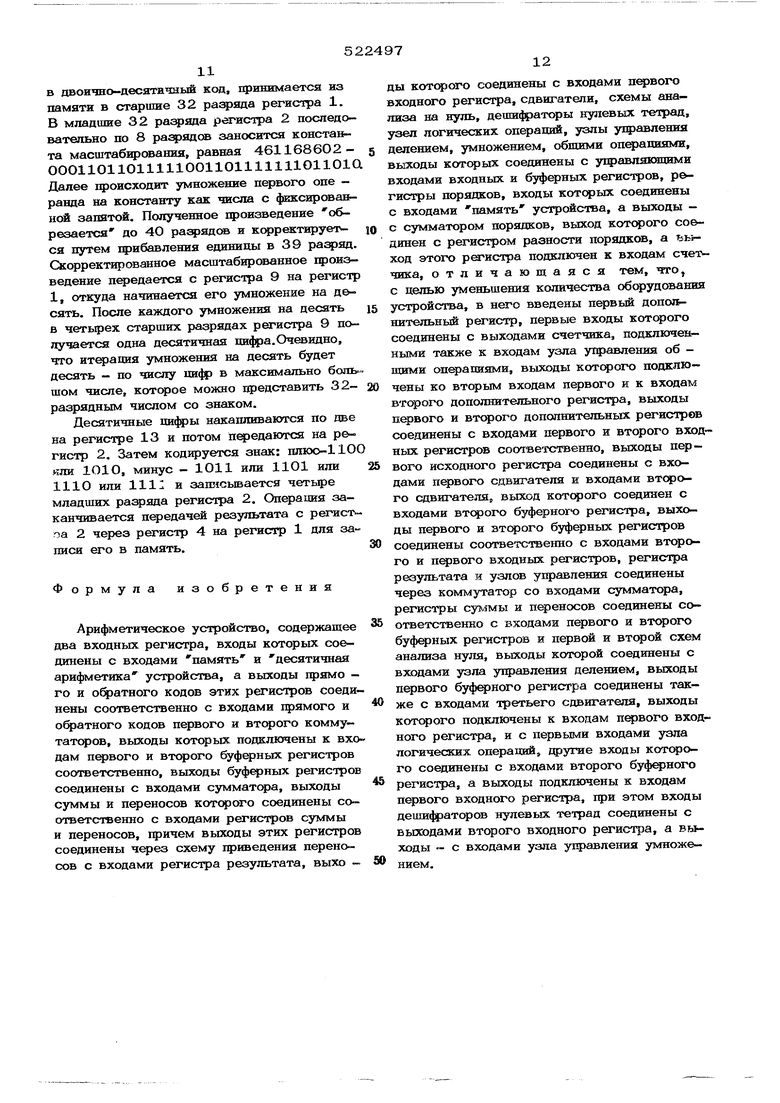

На чертеже изображена блок-схема пред лагаемого устройства.

Арифметическое устройство состоит из двух входных регистров 1 и 2, слузкащих для приема операнДб двух буферных регис ров 3 и 4, на которые подаются операнды, подготовленные для сложения (сдвинутые влево или вправо, инвертированные, обнулен ные целиком или частично и т. д.), cyMMaTO pa 5, которьй складывает три слагаемых, а затем полученные полусуммы и переносы складьшает второй раз и вторичные полусуммы и переносы запоминает на регистре 6 сумм и регистре 7 переносов; схемы 8 приведения переносов и регистра 9 результата.

К регистру 1 подключены выходы сдвигателя 10 (влево 4, влево 8 и прямой код без сдвига), связанных с регистром 3; вьь ходы схем 11 И и ИСКЛЮЧАЮЩЕЕ ИЛИ, связанных с регистрами 3 и 4| выход восьмиразрядного дополнительного регистра 12 с выходов которого имеется возможность записать информацию в любую часть регистра 1. Кроме того, регистр 1 связан по входу с регистром 9 результата и с входами память и десятичная арифметика арифметического устройства.

Таким образом, регистр 1 служит не только для приема первого операнда, но и для записи в память результата операций двоичного и десятичного арифметического и логического устройств.

Регистр 2 также связан с входами память устройства для приема второго one ранда; с восьмиразрядными дополнительным регистром 13, информацию с которого записать в любую часть регистра 2.

К регистру 3 подключены выходы сдвигателя 14 (вправо 1, вправо 4, вправо 8, прямой и обратный код без сдвига, влево 1) связанных с регистром 1, а также цепь сдвига влево 1, связанная с регистром 6.

К регистру 4 подключены выходы сдви гателя IS (влево 2, влево 2 обратным кодом и влево 3), связанных с регистром 1; вькоды сдвиговых цепей 16 (вправо 1, прямой и обратный код без сдвига), связанных с регистром 2, а также цепь сдвига влево 2, связанная с регистром 7.

Кроме того, регистр 2 связан по входу с регистром 3, а регистр 1 с регистра - ми 4 и 9.

Третий вход о гмматора S подключен к выходу схемы 17 выборки третьего слагаемого, входы которой связаны с регистром 9 цепями прямого и обратного кода и впра во 4.

При работе с плавающей запятой поряд ки операнд из блока центрального управле ния через входы память поступают на восьмиразрядные регистры порядков 18 и 19, выходы которых соединены с входами сумматора 20 порядков, сумма (разность) запоминается на регистре 21 суммы порядков. Выходы регистра 21 соединены со счетчиком 22 сдвига, где осуществляется корректировка в зависимости от нормализации результата.

Скорректированньй порядок результата поступает на регистр 12, с которого передается в восемь старших разрядов регистра 1.

К регистру 2 подключена схема 23 анализа множителя и схема 24 нулевых тетрад выходы которых связаны со схемой 25 управления выполнением операции умножения. К регистру 6 подключена первая схема 26 анализа на нуль, к регистру 7 - вторая схема 27 анализа на нуль, выходы которых связаны со схемой 28 управления выпол нением операции деления.

Выходы счетчика 22 подключены также к схеме 29 управления операциями сложения, сдвига и логическими операциями.

Выходы схем управления 25, 28 и 29 подключены к регистрам 1-4 и управляют их работой.

Устройство работает следующим образом

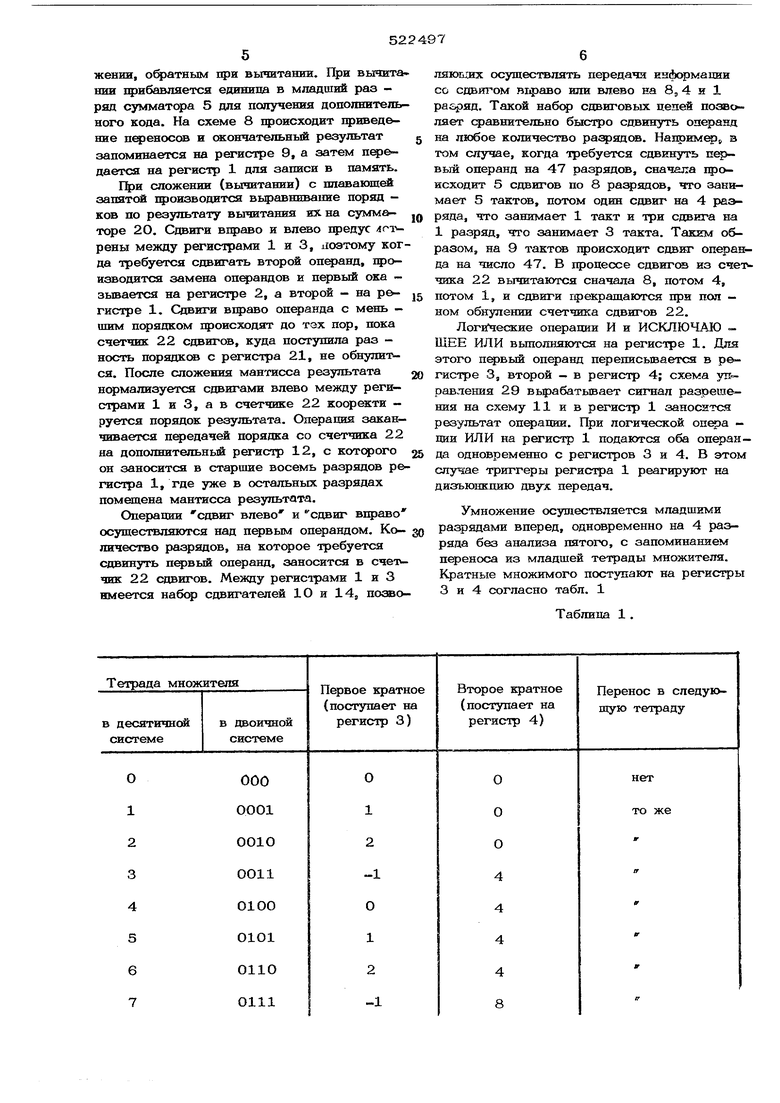

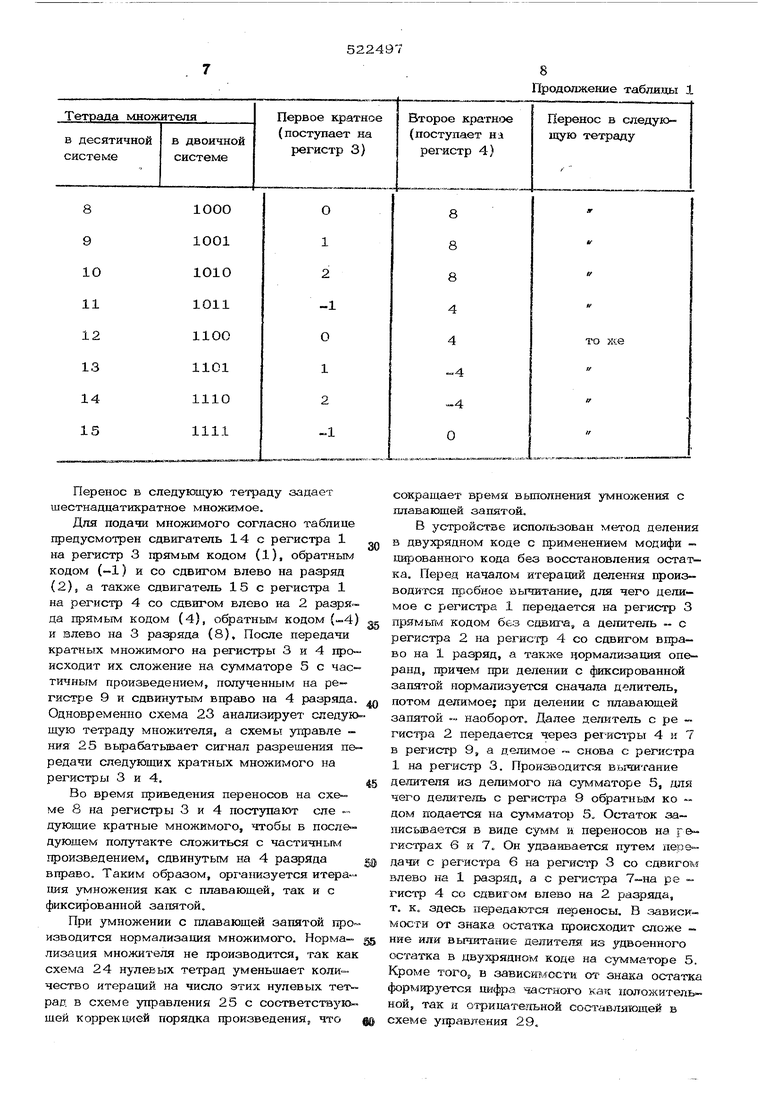

При сложении (выяитании) с фиксированной запятой операнды поступают на вход ные регистры 1 и 2, Первый операнд по дается на регистр 3 прямым кодом, вто рой - на регистр 4 прямым кодом при еложении, статным гфи вычитании. При вычита нии 1фи6авляется единица в младший раз ряд сумматора 5 для получения дополнитель ного кода. На схеме 8 щэонсходит приведение переносов и окончательный результат запоминается на регистре 9, а затем передается на регистр 1 для записи в память. Цри сложении (вычитании) с плаваюшей запятой Щ)оизводится вьфавштание поряд ков по результату вычитания ях на сумматоре 2О. Сдвиги вправо и влево хфедус рены между регистрами 1 и 3, поэтому ког да требуется сдвигать второй операнд, 1фоизводится замена оп андов и первый ока зывается на регистре 2, а второй - на регистре 1. Сдвиги операнда с мень - шим порядком происходят до тех пор, пока счетчик 22 сдвигов, куда поступила раз ность порядке с регистра 21, не обнулитчся. После сложения мантисса результата нормализуется сдвигами влево между регистрами 1 и 3, а в счетчике 22 кооректи руется результата. Операция заканчивается передачей порядка со счетчика 22 на дополнительный регистр 12, с котсрого он заносится в старшие восемь разрядов ре гистра 1, где уже в остальных разрядах помещена мантисса результата. Операции сдвиг влево и сдвиг вправо осуществляются над первым операндом. Количество разрядов, на которое требуется сдвинуть операнд, заносится в счет чик 22 сдвигов. Между регистрами 1 и 3 имеется набор сдвигателей 10 и i4, поаво ЛЯЮБ1ИХ осуществлять передачи информации со сдвигом BijpaBo или влево на 8,4 и 1 рааряд. Такой набср сдвиговых цепей позволяет яравнительно быстро сдвинуть операнд на любое количество разрядов. Напримет в том случае, когда требуется сдвинуть первый операнд на 47 разрядов, сначала щэоисходит 5 сдвигов по 8 разрзшов, что занимает 5 тактов, потом один сдвиг вга 4 раэряда, что занимает 1 такт и три сдвига на 1 разряд, что занимает 3 такта. Таким образом, на 9 такт(ж происходит сдвиг операнда на число 47. В процессе сдвигов из счетчика 22 вычитаются сначала 8, потом 4, потом 1, и сдвиги гфекращаются при пол ном обнулении счетчика сдвигов 22. Логические операции И и ИСКЛЮЧАЮ ШЕЕ ИЛИ вьшопняются на регистре 1. Для этого операнд перепнсьюается в регистре 3, второй - в регистр 4; схема ртравлеш1я 29 вьфабатывает сигнал разрешения на схему 11 и в регистр 1 заносится результат операции. При логической опета ции ИЛИ на регистр 1 подаются оба операнда одновременно с регистров 3 и 4. В этом случае триггеры регистра 1 реагируют на дизъЮ1ш;пию двух передач. Умножение осуществляется младшими разрядами вперед, одновременно на 4 разряда без анализа пятого, с запоминанием переноса из младшей тетрады множителя. Кратные множимого поступают на регистры 3 и 4 согласно табл. 1 Таблина 1.

8 Продолжение таблицы 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| Арифметическое устройство с фиксированной точкой | 1984 |

|

SU1241230A1 |

| Устройство для умножения | 1984 |

|

SU1249507A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Устройство для умножения | 1985 |

|

SU1278838A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| Устройство для обработки данных | 1987 |

|

SU1513443A1 |

Перенос в следующую тетраду задает шестнадцатихратное множимое. Для подачи множимого согласно таблице предусмотрен сдвигатель 14с регистра 1 на регистр 3 прямым кодом (1), обратны л кодом (-1) и со сдвигом влево на paspsm (2), а такхче сдвигатель 15с регистра 1 на регистр 4 со сдвигом влево на 2 разряда прямым кодом (4), обратным кодом {-4) и влево на 3 (8), После передачи кратных множимого на регистры 3 и 4 1фоисходит их сложение на сумматоре 5 с частичным произведением, полученным на регистре 9 и сдвинутым вправо на 4 разряда. Одновременно схема 23 анализирует следую щую тетраду множителя, а схемы управле ния 25 вырабатьшает сигнал разрешения пе редачи следующих кратных множимого на регистры 3 и 4. Во время приведения переносов на схеме 8 на регистры 3 и 4 поступают еле дующие кратные множимого, чтобы в после дующем полутакте сложиться с частичнык произведением, сдвинутым на 4 разряда вправо. Таким образом, организуется итерация умножения как с плавающей, так и с фиксированной запятой. При умножении с плавающей запятой про изводится нормализация множимого. Нормализация множителя не производится, так как схема 24 нулевых тетрад уменьшает количество итераций на число этих нулевых тетрад в схеме управления 25 с соответствую щей коррекцией порядка произведения, что сокращает время вьшоянения умножения с плавающей запятой. В устройстве использован метод деления в двухрядном коде с применением модифи - шфованного кода без восстановления остатка. Перед началом итераций деления производится пробное вычитание, для чего делимое с регистра 1 передается на регистр 3 прямым кодом без сдвига, а делитель - с регистра 2 на регисф 4 со сдвигом вправо на 1 разряд, а также нормализация операнд, причем при делении с фиксированной запятой нормализуется сначала делитель, потом делимое; при делении с плавающей запятой наоборот. Далее делитель с ре гистра 2 передается через регисары 4 и 7 в регистр 9, а делимое -. снова с регистра 1 на регис-тр 3. Производится вычитание делителя из делимого на сумматоре 5, для чего делитель с регистра 9 обратным ко - дом подается на сумматор 5. Остаток за- пксывается в виде сумм и переносов на р эгистрах 6 и 7. Он удваивается путем передачи с регистра 6 на регистр 3 со сдвигом влево на 1 разряд, а с регистра 7-на ре гистр 4 со сдвигом влево на 2 разряда, т. к. здесь передаются переносы. В завискмости от знака осч-атка яроисходит сложе ние или вычитание делителя из удвоенного остатка в двухрядном коде на сз мматоре 5. Кроме TorOs, в заъкскмости от знака остатка формируется цифра, частного как положительной, так и отрицатеггьной сост авляющей в схеме угфавления 29.

Цифры частного занисьтаются в допол нительные регистры 12 и 13, и после того как накопится 8 гшфр частного в каждом из них, они переписываются в регистры 1 и 2, Таким образом, в конце операции по - лучаются две составляющие частного: положительная на регистре 1 и отрицательная на регистре 2. Сложением этих составляющих на сук-гматоре 5 и схеме 8 приведения

При девятой комбинации производится только сдвиг остатка без сложения или вычитания и в регистры 12 и 13 записывают- ся нули.

Операции перевода из двоичной системы в десятичную и обратно осуществляются следующим образом. При переводе в двоичную систему второй операнд поступает на регисхр 2 в двоичгю-десятичном коде в виде десяти ЦИФР и знака, занимающего четыре младших разряда регистра 2, Старшая тдифра черев регистр 12 передается с регистра 2 на регистр 1 и умножается на десять путем передачи со сдвигом влево на 1 разряд через сдвигатель 14 на регистр 3 и со сдвигом влево на 3 разряда через сдвигатель 15 на ретистр 4 к сложения на cyTviMaTope 5 и схеме 8 приведения переносов с запо- минанием результата на регистре 9.

Полученньй результат с регистра 9 передается на сумматор 5 прямым кодом че рез схему 17 и складывается со второй десятичной цифрой, сзаблаговремеино подан -

переносов получают окончательный результат деления в однорядном коде на регистре 9.

Для ощ5еделения в каждой итерации знака остатка в схеме управления 28 осуществляется сложение четьфех старших разря дов с полным хфиведением переносов и по результату его охределяют знак остатка по табл. 2.

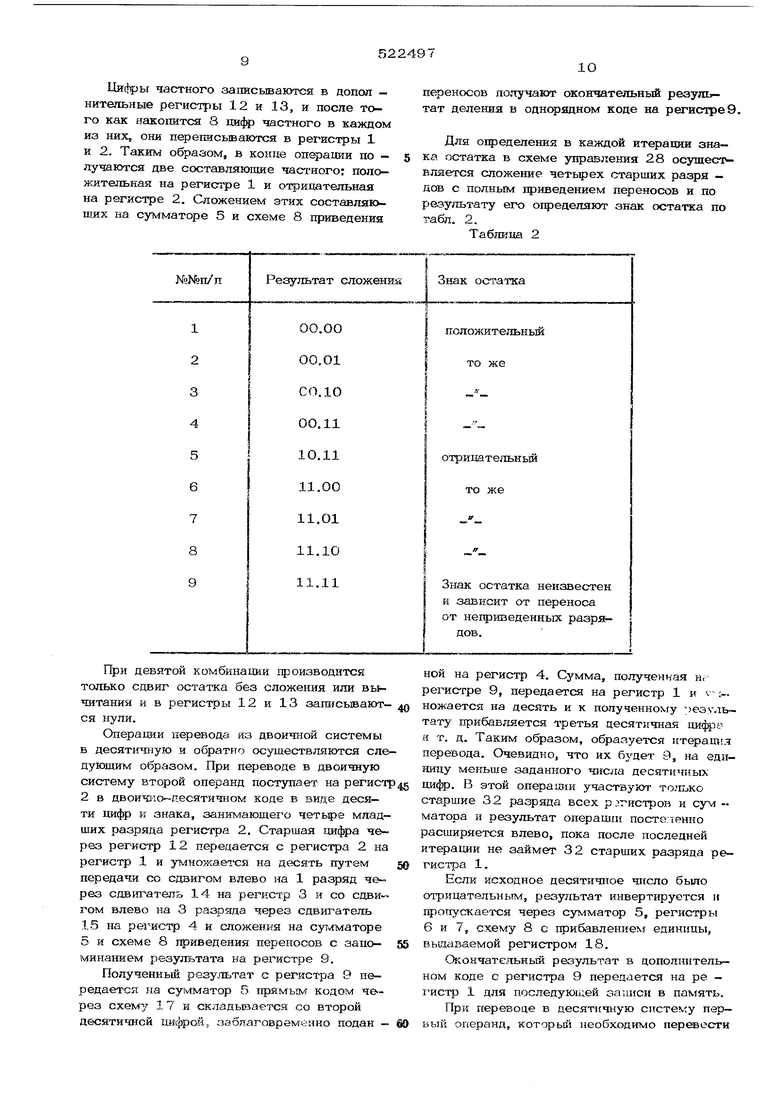

Таблица 2

ной на регистр 4. Сумма, полученная н. регистре 9, передается на регистр 1 и ножается на десять и к полученному -jeayabтату прибавгшется третья десятичная цифр. я т. д. Таким образом, образуется нтерашл перевода. Очевидно, что их будет 9, на единицу меньше заданного числа десятичных цифр. В этой операции участвуют только старшие 32 разряда всех регистров и сум матора и результат операции постепенно расширяется влево, пока после последней итерации не займет 32 старших разряда регистра 1.

Если исходное десятичное число было отрицательньт-, результат инвертируется и пропускается через сумматор 5, регистры 6 и 7, схему 8 с прибавлением единицы, выдаваемой регистром 18.

Окончательный результат в дополнительном коде с регистра 9 передается на ре 1истр 1 для последующей записи в память.

При переводе в десятичную систему первый операнд, который необходимо перевести

в двоично-десятичный код, гршшмается из памяти в старшие 32 регистра 1. В младшие 32 регистфа 2 последовательно по 8 разрядов заносится константа масштабврования, равная 461168602OOOllOllOlllllOOllOlllllllOllOlДалее хфоисходит умножение первого one - ранда на константу как числа с фиксированной запятой. Полученное щ оизведение обрезается до 4О ра ядсяз и кс ректирует ся путем прибавления единицы в 39 Осорректированное масштабированное гфоизведение предается с регистра 9 на регистр 1, откуда начинается его умножение на десять. После каждого умножения на десять в четьфех старших р азрядах регистра 9 получается одна десятичная цифра.Очевидно, что умножения на десять будет десять - но числу ии(|р в максимально боль шом числе, котсрое можно представить 32- разрядным числом со знаком.

Десятичные 1ш4ры накапливаются по две на регистре 13 и потом передаются на регистр 2. Затем кодируется знак: плюо-11О или 1О1О, минус - 1О11 или 1101 или 1110 или 1111 и запзюываетсн четыре младших разряда регистра 2. Операция заканчивается п едачей результата с регист- оа 2 через регистр 4 на регистр 1 для записи его в память.

Формула изобретения

Арифметическое устройство, содержащее два входных регистра, входы которых соединены с входами память и десятичная арифметика устройства, а выходы прямо го и офатного кодов этих регистров соединены соответственно с входами прямого и офатного кодов первого и коммутаторов, выходы которых подключены к входам нового и второго регистров соответственно, выходы буферных регистров соединены с входами сумматора, выходы суммы и переносов которого соединены соответственно с входами регистров суммы и переносов, причем выходы этих регистров соединены схему щ иведения переносов с входами регистра результата, выхо -

ды которого соединены с входами первого входного регистра, сдвигатепи, схемы анализа на нуль, деихи раторы нулевых тетрад, узел логических операций, узлы уцравления делением, умножением, общими операциями, выходы которых соединены с утфавлякицими входами входных и буферных регистров, регистры порядков, входы котсрых соединены с входами память устройства, а выходы - с сумматором порядков, выход котсчрого соединен с регистром разности порядков, а ъкход этого рет истра подключен к входам счечика, отличающаяся тем, гго, с целью уменьшения количества оборудовани устройства, в него введены первый дополнительный регистр, первые входы котсрого соединены с выходами счетчика, подключевгными также к входам узла ут равления об шими операгшями, выходы которого подключены ко вторым входам первого и к входам второго дополнительного регистра, выходы первого и второго дополнительных регистров соединены с входами первого и второго вхоных регистров соответственно, выходы первого исходного регистра соединены с входами нового сдвигателя и входами сдвигателЯа вьсюд которого соединен с входами буферног-о регистра, выходы первого и второго буферных регистров соединены соответственно с входами второго и первого входных регистров, регистра результата и узлов управления соединены через коммутатор со входами сумматора, регистры сул1мы и переносов соединены соответственно с входами первого и втсфого регистров и первой и второй схем анализа нуля, выходы которой соединены с входами узла управления делением, выходы первого регистра соединены также с входами третьего сдвигателя, выходы котсрого подключены к входам входного регистра, и с первыми входами узла логических операций, щэугие входы котсфого соединены с входами второго регистра, а выходы подключены к входам первого входного регистра, гфи этом входы деши4раторов нулевых тетрад соединены с выходами второго входного регистра, а выходы ™ с входами узла управления умножением.

Авторы

Даты

1976-07-25—Публикация

1971-06-14—Подача