оо

(X)

о

00

Изобретение относится к ан;гпого- вой вычислительной технике и может быть использовано при помехоустойчивом аналого-цифровом преобразовании информации в специализированных цифровых системах контроля регистрации и управления реальными технологическими процессами или объектами.

Цель изобретения - повышение достоверности преобразования.

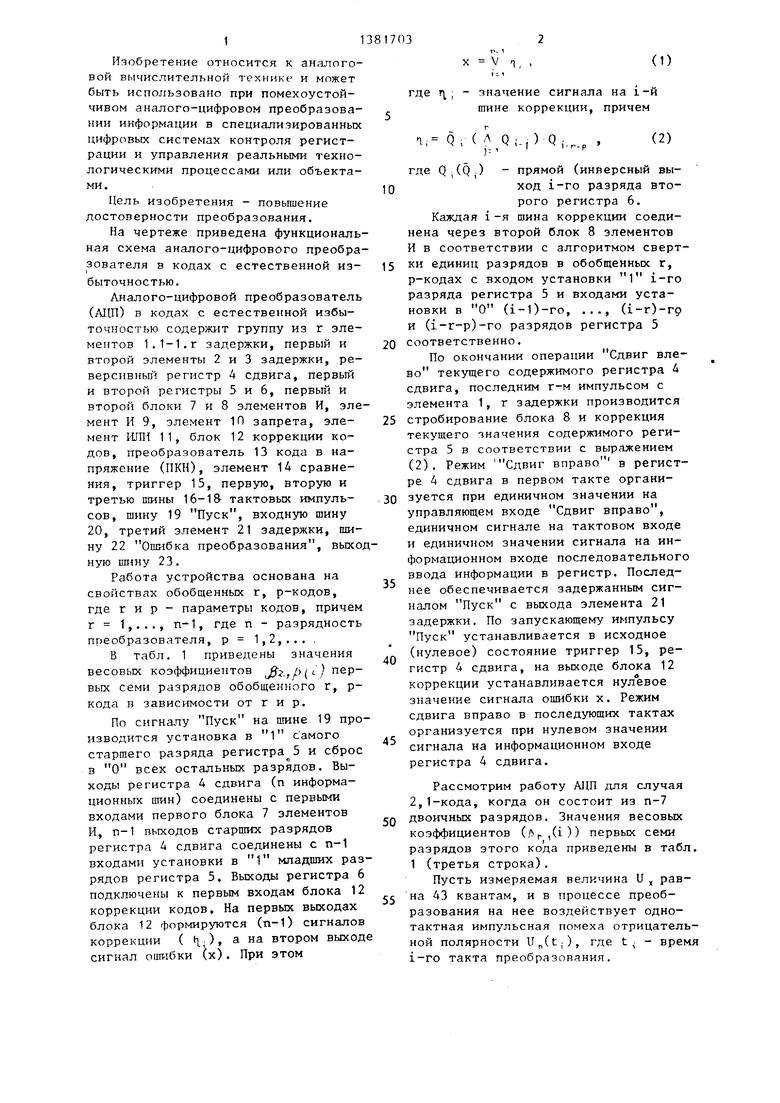

На чертеже приведена функциональная схема аналого-цифрового преобразователя в кодах с естественной избыточностью.

Аналого-цифровой преобразователь (АЦП) в кодах с естественной избыточностью содержит группу из г элементов 1.1-1.г задержки, первый и второй элементы 2 и 3 задержки, ре- версивньш регистр 4 сдвига, первый и второй регистры 5 и 6, первый и второй блоки 7 и 8 элементов И, элемент И 9, элемент 1П запрета, элемент ИЛИ 11, блок 12 коррекции кодов, преобразователь 13 кода в напряжение (ПКН), элемент 1А сравнения, триггер 15, первую, вторую и третью шины 16-1& тактовых импульсов, шину 19 Пуск, входную шину 20, третий элемент 21 задержки, шину 22 Ошибка преобразования, выхоную шину 23.

Работа устройства основана на свойствах обобщенных г, р-кодов, где г и р - параметры кодов, причем г 1,..., п-1, где п - разрядность преобразователя, р 1,2,... .

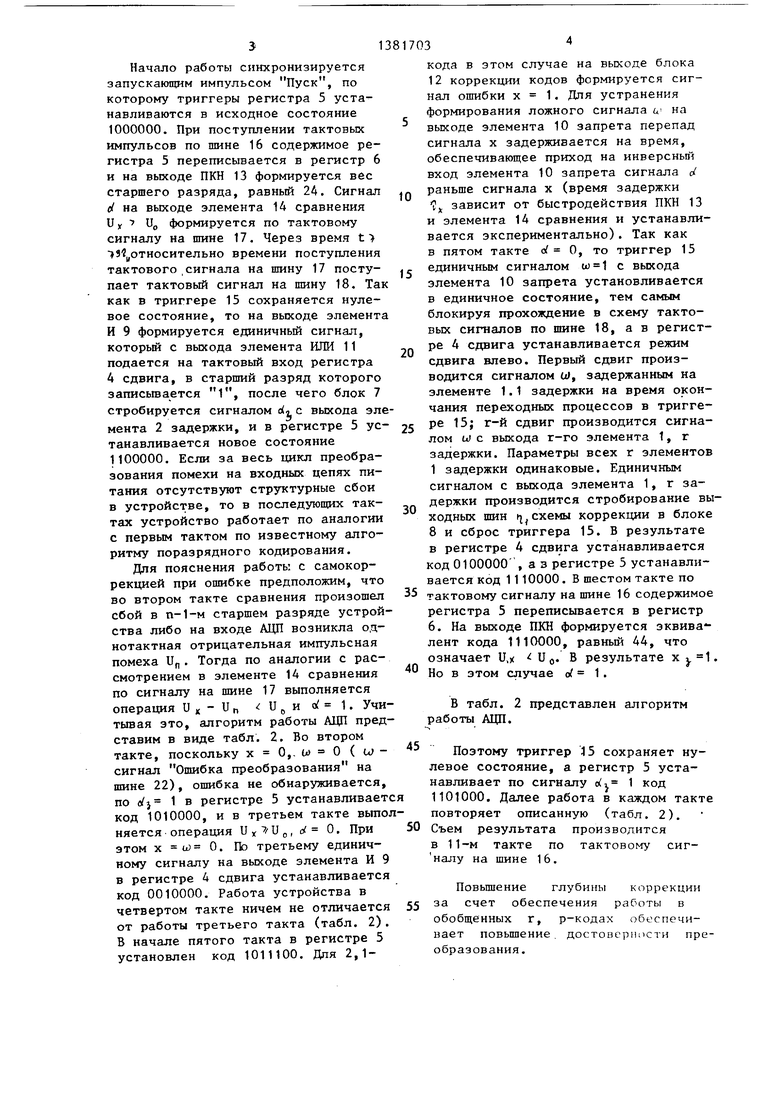

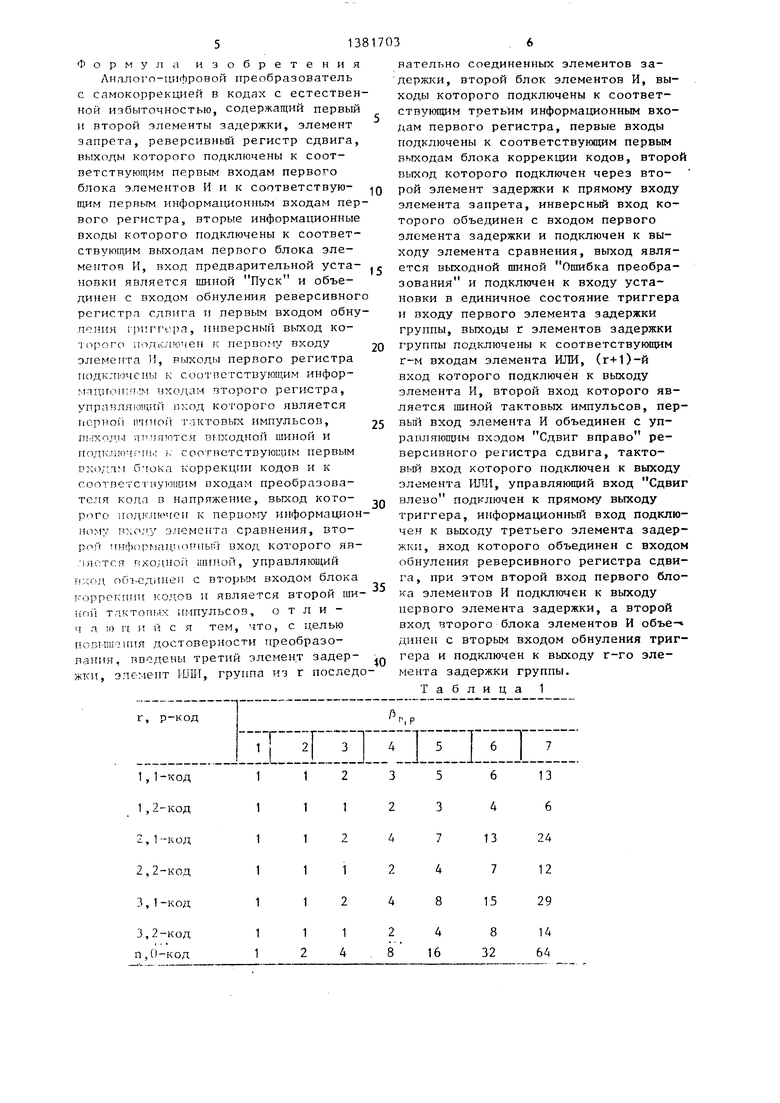

В табл. 1 приведены значения весовых коэффициентов Дг,/ ( первых семи разрядов обобщенного г, р- кода в зависимости от г и р.

По сигналу Пуск на шине 19 производится установка в 1 с амого старшего разряда регистра 5 и сброс в О всех остальных разрядов. Выходы регистра 4 сдвига (п информационных шин) соединены с первыми входами первого блока 7 элементов И, п-1 выходов старших разрядов регистра Д сдвига соединены с п-1 входами установки в 1 младших разрядов регистра 5, Выходы регистра 6 подключены к первым входам блока 12 коррекции кодов. На первых выходах блока 12 формируются (п-1) сигналов коррекции ( е ), а на втором выход сигнал ошибки (х). При этом

X V ч, ,

(1)

где 1 ; - значение сигнала на i-й шине коррекции, причем

, Q. (J,QH Qi-n.p . (2)

где Q(Q.) - прямой (инверсный вы0ход i-ro разряда второго регистра 6.

Каждая i-я шина коррекции соединена через второй блок 8 элементов И в соответствии с алгоритмом сверт5 ки единиц разрядов в обобщенных г, р-кодах с входом установки 1 i-ro разряда регистра 5 и входами установки в О (i-l)-ro(i-r)-r9

и (i-r-p)-ro разрядов регистра 5

0 соответственно.

По окончании операции Сдвиг влево текущего содержимого регистра А сдвига, последним г-м импульсом с элемента 1, г задержки производится

5 стробирование блока 8 и коррекция текущего значения содержимого регистра 5 в соответствии с выражением (2). Режим Сдвиг вправо в регистре 4 сдвига в первом такте органи0 зуется при единичном значении на управляющем входе Сдвиг вправо, единичном сигнале на тактовом входе и единичном значении сигнала на информационном входе последовательного ввода информации в регистр. Последнее обеспечивается задержанным сигналом Пуск с выхода элемента 21 задержки. По запускающему импульсу Пуск устанавливается в исходное (нулевое) состояние триггер 15, регистр 4 сдвига, на выходе блока 12 коррекции устанавливается нул евое значение сигнала ошибки х. Режим сдвига вправо в последующих тактах организуется при нулевом значении сигнала на информационном входе регистра 4 сдвига.

5

5

Рассмотрим работу АЦП для случая 2,1-кода, когда он состоит из п-7

двоичных разрядов. Значения весовых коэффициентов (/Vp,(i)) первых семи разрядов этого кода приведены в табл. 1 (третья строка).

Пусть измеряемая величина U , равна 43 квантам, и в процессе преобразования на нее воздействует одно- тактная импульсная помеха отрицательной полярности U(t;), где t - время i-ro такта преобразования.

Начало работы синхронизируется запускающим импульсом Пуск, по которому триггеры регистра 5 устанавливаются в исходное состояние 1000000. При поступлении тактовых импульсов по шине 16 содержимое регистра 5 переписывается в регистр 6 и на выходе ПКН 13 формируется вес старшего разряда, равный 24. Сигнал е/ на выходе элемента 14 сравнения и X Up формируется по тактовому сигналу на шине 17. Через время t 3 „относительно времени поступления тактового ,сигнала на шину 17 поступает тактовый сигнал на шину 18. Так как в триггере 15 сохраняется нулевое состояние, то на выходе элемента И 9 формируется единичный сигнал, который с выхода элемента ШШ 11 подается на тактовый вход регистра 4 сдвига, в старший разряд которого записьгоается 1, после чего блок 7 стробируется сигналом о(г с выхода элемента 2 задержки, и в регистре 5 устанавливается новое состояние 1100000. Если за весь цикл преобразования помехи на входных цепях питания отсутствуют стрзгктурные сбои в устройстве, то в последующих тактах устройство работает по аналогии с первым тактом по известному алгоритму поразрядного кодирования.

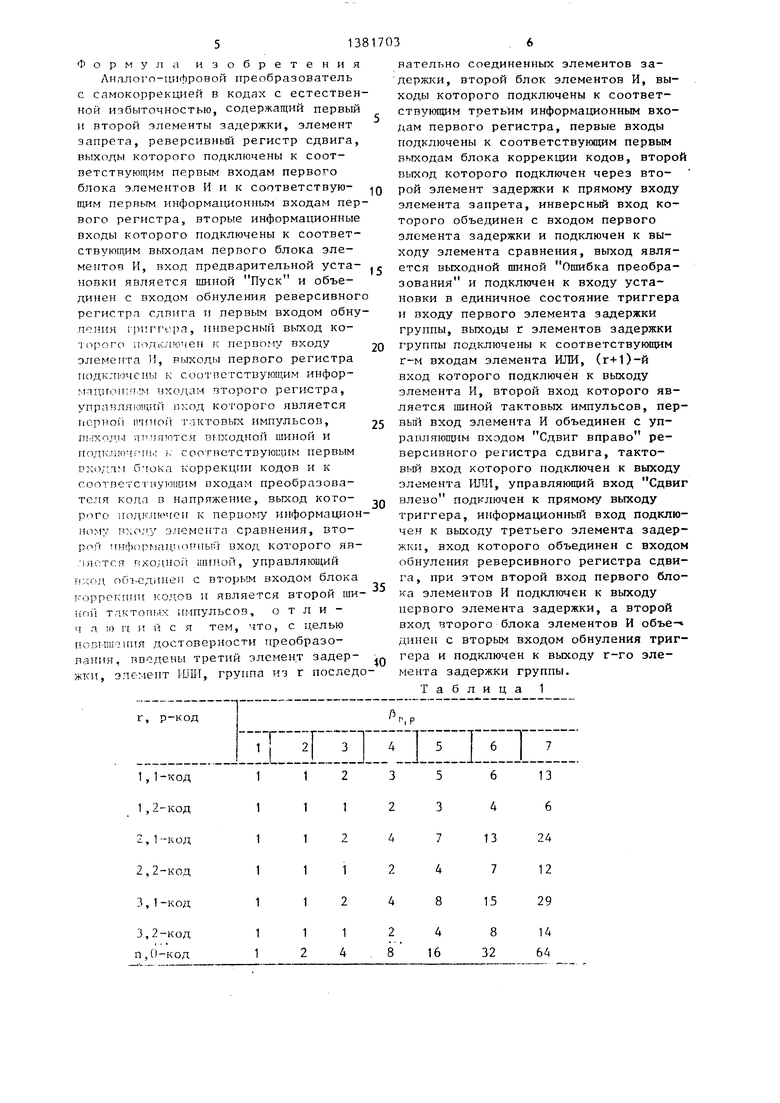

Для пояснения работы с самокоррекцией при ошибке предположим, что во втором такте сравнения произошел сбой в n-1-M старшем разряде устройства либо на входе АЦП возникла од- нотактная отрицательная импульсная помеха Un. Тогда по аналогии с рассмотрением в элементе 14 сравнения по сигналу на шине 17 выполняется операция , ;ирИО 1. Учитывая это, алгоритм работы АЦП представим в виде табл. 2. Во втором такте, поскольку х 0,-W О ( ы- сигнал Опшбка преобразования на шине 22), ошибка не обнаруживается, по 1 в регистре 5 устанавливаетс код 1010000, и в третьем такте вьшол няется операция , d 0. При этом X а) 0. По третьему единичному сигналу на выходе элемента И 9 в регистре 4 сдвига устанавливается код 0010000. Работа устройства в четвертом такте ничем не отличается от работы третьего такта (табл. 2). В начале пятого такта в регистре 5 установлен код 1011100. Для 2,110

15

я-

381703

кода в этом случае на выходе блока 12 коррекции кодов формируется сигнал ошибки X 1. Для устранения формирования ложного сигнала i, на выходе элемента 10 запрета перепад сигнала х задерживается на время, обеспечивающее приход на инверсньш вход элемента 10 запрета сигнала d раньше сигнала х (время задержки зависит от быстродействия ПКН 13 и элемента 14 сравнения и устанавливается экспериментально). Так как в пятом такте о О, то триггер 15 единичным сигналом u) 1 с выхода элемента 10 запрета установливается в единичное состояние, тем самым блокируя прохождение в схему тактовых сигналов по шине 18, а в регистре 4 сдвига устанавливается режим сдвига влево. Первый сдвиг производится сигналом W, задержанным на элементе 1.1 задержки на время окончания переходных процессов в триггере 15; г-й сдвиг производится сигналом ы с выхода г-го элемента 1, г задержки. Параметры всех г элементов 1 задержки одинаковые. Единичным сигналом с выхода элемента 1, г задержки производится стробирование выходных шин ц схемы коррекции в блоке 8 и сброс триггера 15. В результате в регистре 4 сдвига устанавливается код 0100000 , а з регистре 5 устанавливается код 1110000. В шестом такте по 35 тактовому сигналу на шине 16 содержимое регистра 5 переписывается в регистр 6. На выходе ПКН формируется эквивалент кода 1110000, равный 44, что означает U.x U ,. В результате Но в этом случае о 1 .

20

25

30

40

X J, 1 .

В табл. 2 представлен алгоритм работы АЦП.

Поэтому триггер 15 сохраняет нулевое состояние, а регистр 5 устанавливает по сигналу 1 код 1101000. Далее работа в каждом такте повторяет описанную (табл. 2). Съем результата производится в 11-м такте по тактовому сиг- налу на шине 16.

Повьш1ение глубины коррекции за счет обеспечения работы в

обобщенных г, вает повьш1ение образования.

р-кодах обеспечи- , достоверности пре51381703

Формула изобретения

Лналого-цифровой преобразователь с самокоррекциен в кодях с естественной избыточностью, содержащий первый и второй элементы задержки, элемент запрета, реверсивный регистр сдвига, выходы которого подключены к соответствующим первым входам первого блока элементов И и к соответствующим первьгм информационным входам первого регистра, вторые информационные входы которого подключены к соответствующим выходам первого блока элементов И, вход предварительной уста- ется выходной шиной Ошибка преобра10

нательно соединенных элементов за- дерлоси, второй блок элементов И, выходы которого подключены к соответ- ствуюпщм третьим информационным входам первого регистра, первые входы подключены к соответствуюпщм первым выходам блока коррекции кодов, второй выход которого подключен через второй элемент задержки к прямому входу элемента запрета, инверсньй вход которого объединен с входом первого элемента задержки и подключен к выходу элемента сравнения, выход явля20

25

новки является шиной Пуск и объединен с входом обнуления реверсивного регистра сдвига и первым входом обнуления триггера, инверсный выход ко I орого по7 ;кл10чен к первому входу элемента )i, выходы первого регистра подключены к соо гпетствующим инфор- MaipioHirT LNi входам второго регистра, управляющий пкод которого является Г1ср)ой innioi тактовых импульсов, Bbixojn.i виходной шиной и полк.итчгм.; к соо гнетствуюп(им первым пхо,гг.пм блока коррекщпг кодов и к соотпетстнующим входам преобразователя кода в напряжение, выход которого подключен к первоьгу информацион- Шчолз элемента сравнения, вто- роГг тигформацп-от пьп вход которого является пходно1 шиной, управляющий п .ал, оП ьедииеи с вторым входом блока коррекпии 1со:гоо и является второй ши ufui тлктопых импульсов, о т л и - ч п. н) Г1 и и с я тем, что, с целью 110ВМ11Г211ПЯ достоверности цреобразо- пання, введены третий элемент задер- жки, элемент ШШ, группа из г последозования и подключен к входу установки в единичное состояние триггера и входу первого элемента задержки группы, выходы г элементов задержки группы подключены к соответствующим г-м входам элемента ИЛИ, (г+1)-й вход которого подключен к выходу элемента И, второй вход которого является тиной тактовых импульсов, пер вьм вход элемента И объединен с управляющим входом Сдвиг вправо реверсивного регистра сдвига, тактовый вход которого подключен к выходу элемента ИЛИ, управляющий вход Сдвиг 2Q влево подключен к прямому выходу

триггера, информационный вход подключен к выходу третьего элемента задержки, вход которого объединен с входом обнуления реверсивного регистра сдвига, при этом второй вход первого блока элементов И подключен к выходу первого элемента задержки, а второй вход второго блока элементов И объе- динен с вторым входом обнуления триггера и подключен к выходу г-го элемента задержки группы. Таблица 1

,-35

ется выходной шиной Ошибка преобра0

нательно соединенных элементов за- дерлоси, второй блок элементов И, выходы которого подключены к соответ- ствуюпщм третьим информационным входам первого регистра, первые входы подключены к соответствуюпщм первым выходам блока коррекции кодов, второй выход которого подключен через второй элемент задержки к прямому входу элемента запрета, инверсньй вход которого объединен с входом первого элемента задержки и подключен к выходу элемента сравнения, выход явля20

25

о -зования и подключен к входу установки в единичное состояние триггера и входу первого элемента задержки группы, выходы г элементов задержки группы подключены к соответствующим г-м входам элемента ИЛИ, (г+1)-й вход которого подключен к выходу элемента И, второй вход которого является тиной тактовых импульсов, пер- вьм вход элемента И объединен с управляющим входом Сдвиг вправо реверсивного регистра сдвига, тактовый вход которого подключен к выходу элемента ИЛИ, управляющий вход Сдвиг 2Q влево подключен к прямому выходу

триггера, информационный вход подключен к выходу третьего элемента задержки, вход которого объединен с входом обнуления реверсивного регистра сдвига, при этом второй вход первого блока элементов И подключен к выходу первого элемента задержки, а второй вход второго блока элементов И объе- динен с вторым входом обнуления триггера и подключен к выходу г-го элемента задержки группы. Таблица 1

35

- -- о

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь в кодах с естественной избыточностью | 1986 |

|

SU1381698A1 |

| Аналого-цифровой преобразователь с самокоррекцией | 1986 |

|

SU1341716A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1550620A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый и дВОичНО-дЕСя-ТичНОгО B дВОичНый | 1979 |

|

SU809155A1 |

| Устройство для сравнения весов кодов | 1979 |

|

SU798810A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

| Генератор псевдослучайной последовательности импульсов | 1989 |

|

SU1735846A1 |

| Система цикловой синхронизации для многоканальных систем связи | 1988 |

|

SU1598193A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при помехоустойчивом аналого-цифровом преобразовании. Цепь - повышение достоверности преобразования. Аналого- цифровой преобразователь содержит группу 1 элементов задержки, первый и второй элементы 2 и 3 задержки, реверсивный регистр 4 сдвига, первый и второй регистры 5 и 6, первый блок 7 элементов И, второй блок 8 элементов И, элемент И 9, элемент 10 запрета, элемент ИЛИ 11, блок 12 коррекции кодов, преобразователь 13 кода в напряжение, элемент 14 сравнения, триггер 15, первую, вторую и третью шины 16-18 тактовых импульсов, шину 19 Пуск, входную шину 20, третий элемент 21 задержки. Повышение достоверности преобразования достигается за счет увеличения глубины коррекции при работе в обобщенных кодах с естественной избыточностью. 2 табл., 1 ил. с (Л

- о

о о о

о о

о о

о о о о

о о о

- о о о

о

о

о

о

о

о о о

о

о о

о о о о

о о о о

о - о о

о о о о о о

| Браткевич В.В | |||

| и др | |||

| Структура помехоустойчивого аналого-цифрового преобразователя | |||

| - Автометрия, 1975 В 1 | |||

| с | |||

| Устройство для устранения мешающего действия зажигательной электрической системы двигателей внутреннего сгорания на радиоприем | 1922 |

|

SU52A1 |

| Браткевич В.В | |||

| Помехоустойчивый: аналого-цифровой преобразователь, - Автоматика и вычислительная техни- .ка, 1978, № 1, с | |||

| Способ приготовления сернистого красителя защитного цвета | 1915 |

|

SU63A1 |

Авторы

Даты

1988-03-15—Публикация

1986-02-07—Подача