Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при построении преобразователей в системах обработки информации и в оборудовании с точным перемещением исполнительных органов.

Известен преобразователь статического кода Грея в двоичный код, содержащий регистр входного кодЭг логические блоки и распределитель импульсов 1 .

Недостаток данного устройства состоит в ограниченных функциональных возможностях, поскольку оно обеспечивает преобразование только ефлексного двоичного кода (кода Грея).

Наиболее близким к предлагаемому является преобразователь двоичного однопеременного кода в позиционный двоичный код, содержсшшй соединенные последовательно от старших разрядов к младшим элементы отрицания равнозначности по одной в каждом разряде преобразователя, кроме старшего, каждая из которых подключена к соответствующему разряду рефлексного кода 2J .

Недостаток известного преобразователя состоит в ограниченных функциональных возможностях, поскольку он

также не может быть применен для преобразования смещаемого однопеременного кода. .

5 Цель изобретения - расширение класса решаемых задач путем преобразования смещаемого однопеременного кода.

Поставленная цель достигается тем, что в преобразователе двоичного ОДНОГО переменного кода в позиционный двоичный код содержащем группу блоков управляемых полусумматоров, первый вход i-ro блока управляемых полусумматоров (i- от 1 до j), где п - число разрядов преобразуемого кода, является входом (2i-l)-ro разряда входного кода преобразователя, а второй вход 1-го блока управляемых полусумматоров соединен с первым выходом ((+1)-го блока управляемых полусумматоров и является

20 (2i-l)-M разрядом выходного кода пре- образователя, а -ый блок управляемых полусумматоров выполнен в виде элемента отрицания равнозначности, первый вход которого соединен с (п-1)-ым

25 разрядом входного кода преобразователя, а второй вход -СП -ым разрядом входного кода преобразователя и с Л ым разрядом выходного кода преобразо|вателя, третий вход -го блока управ30ляемых полусумматоров соединен с ,

ым разрядом входного кода преобразователя, четвертый вход -i -го блока управляемых полусумматоров соединен с разрядом выходного кода преобразователя И с вторым выходом (1+1)го блока управляемых полусумматоров.

Кроме того, в преобразователе блок управляемых полусумматоров содержит три элемента отрицания равнозначности, два элемента И, элемент ИЛИ и элементНЕ, вход которого является Вторым входом блока управляемых полусумматоров и соединен с первыми входами первого элемента И и первого элемента отрицания равнозначности, выход которого является первым выходом блока управляемых полусумматоров, первый вход которого соединен с вторым входом первого элемента И и первым входом второго элемента отрицания равнозначности, выход которого соединен с вторым входом первого элемента отрицания,равнозначности, .а второй вход второго элемента отрицания равнозначности является третьим входом блока управляемых полусумматоров и соединен с первым входом второго элемента И, второй вход которого соединен с выходом элемента НЕ, выходы первого и второго элементов И через элемент ИЛИ соединены с первым входом третьего элемента отрицания равнозначности, второй вход которого является четвертым входом блока управляемых полусумматоров, а выход третье.го элемента отрицания равнозначности является вторым выходом олока управляемых полусумматоров.

Смещаемый однопеременный код формируется на кодовых дорожках, имеющих рисунок кодовых площадок вида 2-3-3-2-3 парами разрядов,, что позволяет вдвое сократить число кодовых дорожек и соответственно габариты преобразователя перемещения в код.

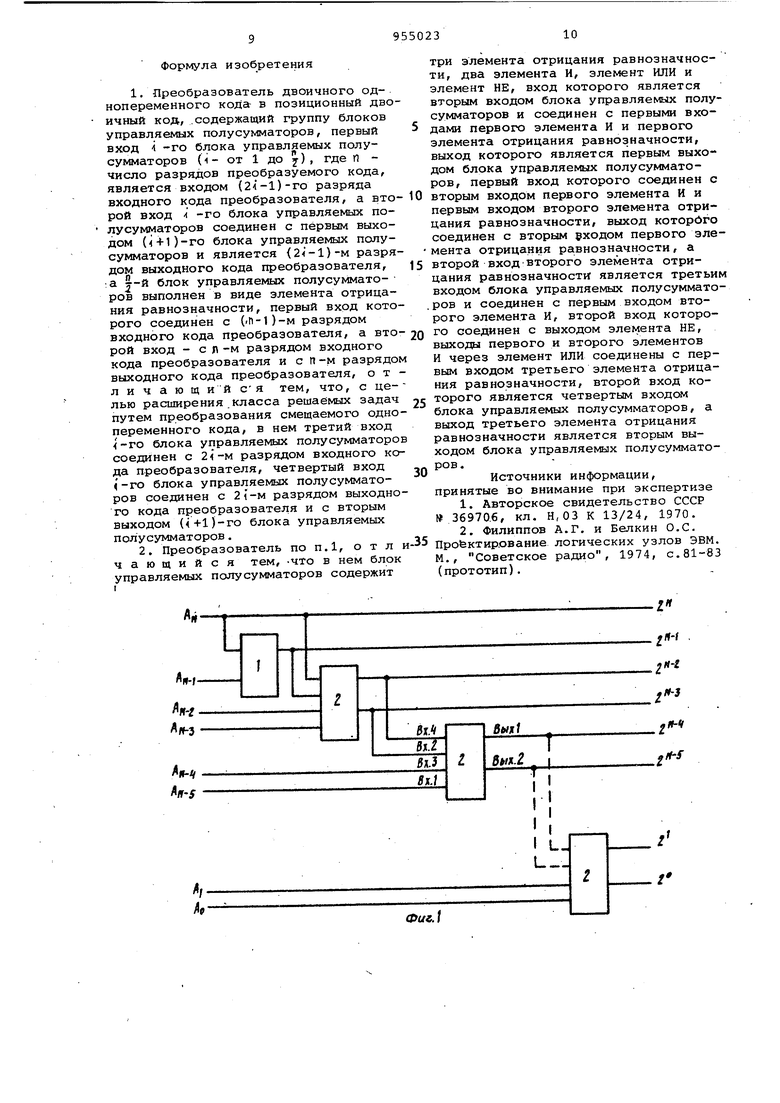

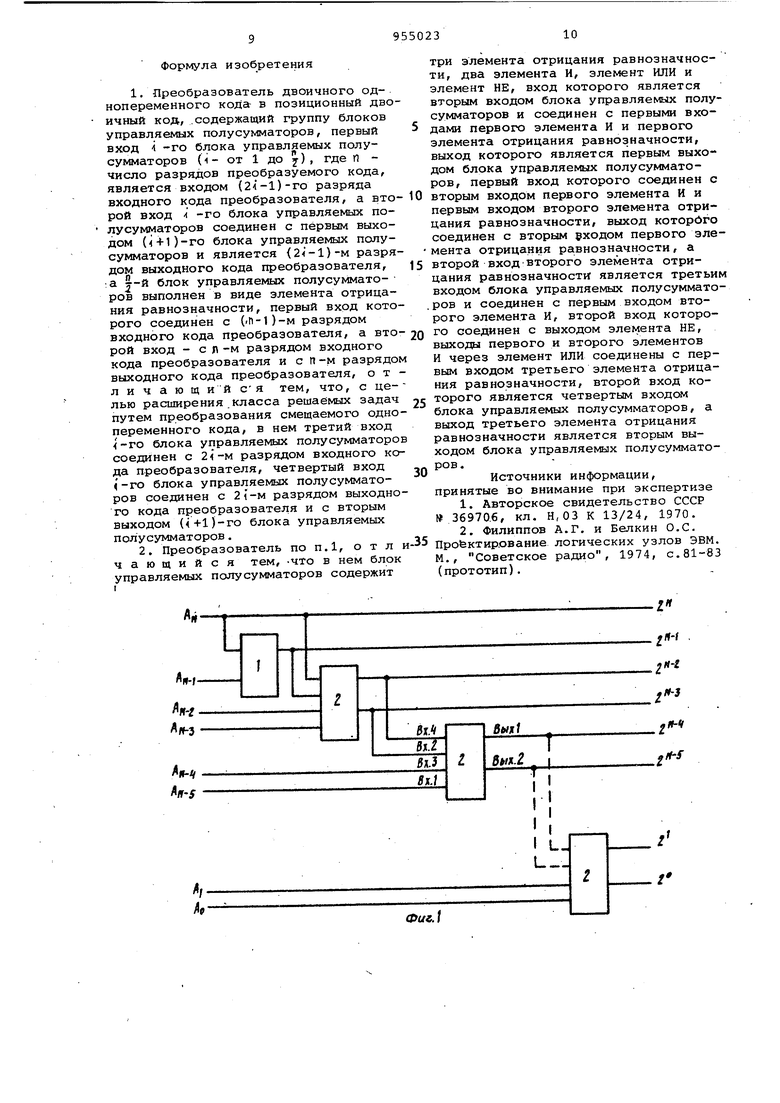

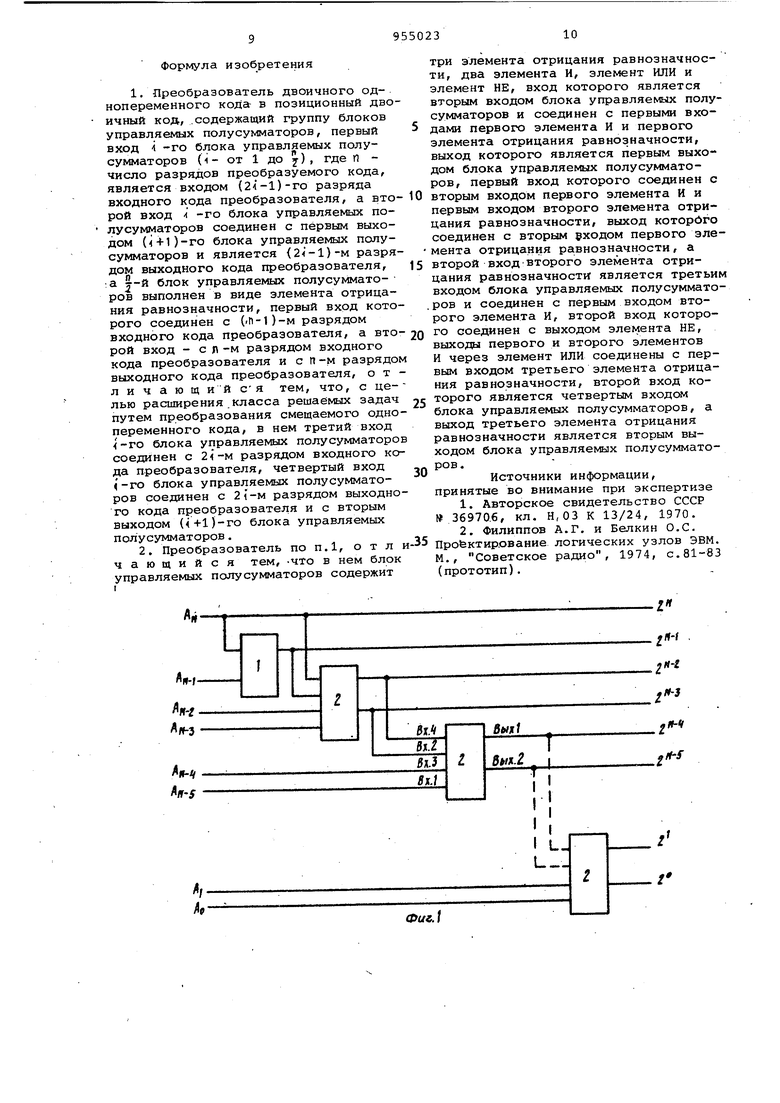

На фиг.1 дана блок-схема предлагаемого преобразователя; на фиг.2 элементная схема блока управляемых полусумматоров.

Преобразователь двоичного однопеременного кода в позиционный двоичный код содержит (фиг.1) элемент 1 отрицания равнозначности-, входы которого подключены к старшим разрядам Av(, Ац- двоичного однопеременного кода, и блоки 2 управляемых полусумматоров, каждый из которых имеет четыре входа и два выхода. Блоки 2 управляемых полусумматоров соединены последовательно от старших разрядов к младшим, причем два входа последующего блока подключены соответственно к двум выходам предыдущего блока 2,

а два других входа подключены к соответствующей паре разрядов двоичного однопеременного кода.

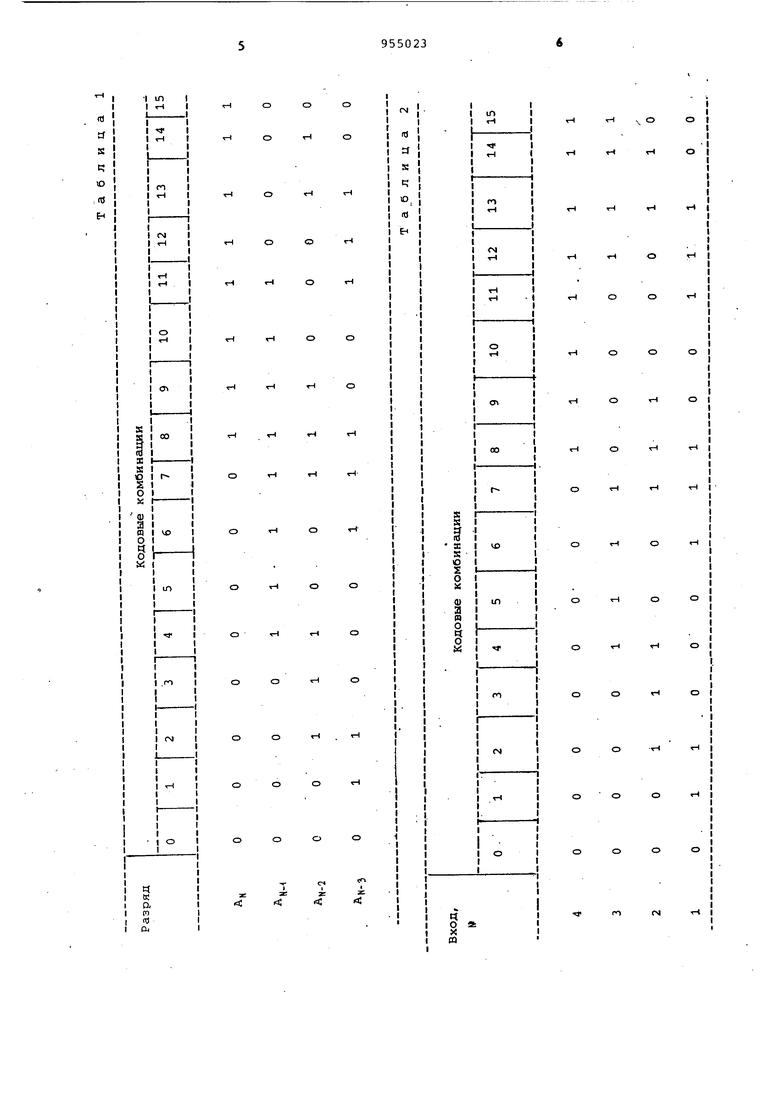

Блок 2 управляемых полусумматоров содержит (фиг.2) первую схему 3 отрицания равнозначности, к одному входу которой подключен вход блока управляемых полусумматоров 2, а к другому входу подключен выход элемента И 4, входы которого подключены соответственно к выходам И 5-6. Первый вход элемента И 6 подключен к входу блока 2 управляемых полусумматоров, к вход элемента НЕ 7 и первому входу элемента 8 отрицания равнозначности, вто.рой вход которого подключен к выходу элемента 9 отрицания равнозначности. Рассмотрим процесс преобразования двоичного однопеременного кода, начиная со старших разрядов. Для этого в исходном коде четырех старших разрядов выделим каждую кодовую комбинацию и полученный сжатый код сверем в табл.1.

В результате преобразования первых двух строк табл.1 элементом 1 отрицания равнозначности получим табл.2 кодовых комбинаций входов блока 2 управляемых полусумматоров.

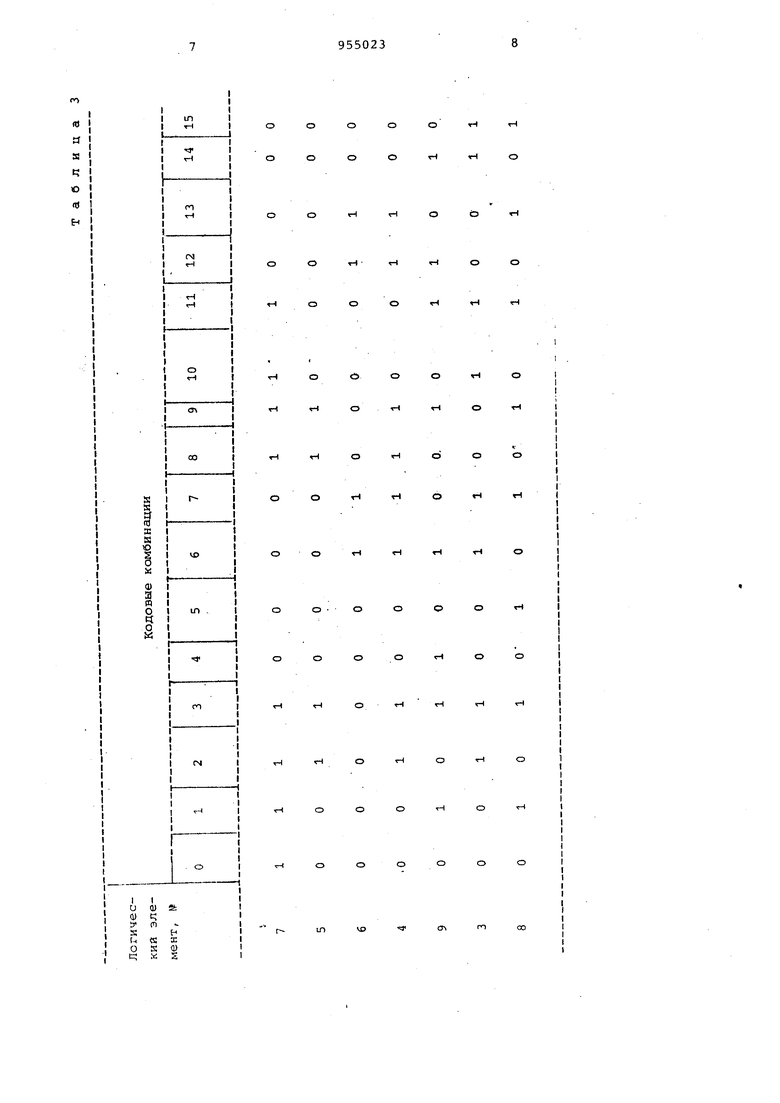

Результаты преобразования строк табл.2 логическими элементами, входящими в логический блок 2 сведены в табл.,3.

Кодовые .комбинации четырех старших разрядов результирующего кода образуются первыми двумя строками табл.2 и последними двумя строкгиии табл.3 и в совокупности формируют позиционный двоичный код.

На входы следующего блока 2 поступают выходы предыдущего блока 2 управляемых полусумматоров и N-4-й, разряды двоичного однопеременного кода.

Выделяя из исходного кода каждую -ю кодовую комбинацию, для кодовых комбинаций входов этого блока получим периодически повторяющую яабл.2, а затем табл.3.

Преобразование исходного двоичного однопеременного кода остальными блоками 2 управляемых полусумматоров ансшогично описанному и в результате на выходе преобразователя формируется двоичный позиционный (N+1)-разрядный код.

Применение предлагаемого преобразователя обуславливает возможностью сопряжения малогабаритных преобразователей перемещения в однопеременный код со стандартной аппаратурной переработки цифровой информации .

о о

тНо

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь отраженного двоичного кода в позиционный двоичный код и обратно | 1981 |

|

SU999039A1 |

| УСТРОЙСТВО для ПАРАЛЛЕЛЬНОГО ПРЕОБРАЗОВАНИЯ РЕФЛЕКСНОГО КОДА В ДВОИЧНЫЙ КОД | 1973 |

|

SU369706A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1569993A1 |

| Преобразователь двоичных кодов угла и дальности в двоично-десятичные коды | 1987 |

|

SU1432782A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1205137A1 |

| Преобразователь двоичного кода в код с весовыми коэффициентами 1 и -1 и обратно | 1981 |

|

SU1007097A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1448412A1 |

| Устройство для преобразования двоичного равновесного кода в двоичный позиционный код | 1988 |

|

SU1557684A1 |

| Преобразователь линейного позиционного кода в двоичный код | 1980 |

|

SU935944A1 |

оt-i

оо

ооо

отНо

о

огНо

о ноо

отНтЧо

оогНо

оотН

О Оо

оооо

3-П(N

о о о о о

о о о о r-t гн о

о о и н о э гч

о о t-f

о о о тН «Н тЧ

о о о о гч о

гЧ о

о о гЧ гЧ о гЧ гЧ

о о

о о о о Q о

о о о о гч о о

гН тЧ о

г-1 о о о гЧ о

-1 о о о о о о

г- 1Л VO оо

гЧ о о

о тН

О гЧ О О О

о «Н о Н о Формула изобретения 1.Преобразователь двоичного однопеременного кода в позиционный дво ичный код, .содержащий группу блоков управляемых полусумматоров, первый вход i -го блока управляемых полусумматоров (i- от 1 до j), где п число разрядов преобразуемого кода, является входом (2i-l)-ro разряда входного кода преобразователя, а вто рой вход к -го блока управляемых полусумматоров соединен с первым выходом (-И)-го блока управляемых полусумматоров и является )-м разря дом выходного кода преобразователя, ;а j-й блок управляемых полусумматоров выполнен в виде элемента отрицания равнозначности, первый вход кото рого соединен с (П-1)-м разрядом входного кода преобразователя, а вто рой вход - с п-м разрядом входного кода преобразователя и с п-м разрядо выходного кода преобразователя, от личают и и Ся тем, что, с целью расширения.класса решаемых задач путем преобразования смещаемого одно переменного кода, в нем третий вход -го блока управляемых полусумматоро соединен с разрядом входного ко да преобразователя, четвертый вход -го блока управляемых полусумматоров соединен с 2i-M разрядом выходно го кода преобразователя и с вторым выходом (+1)-го блока управляемых полусумматоров. 2.Преобразователь по п.1, о т л чающийся тем, -что в нем блок управляемых полусумматоров содержит

/ / три элемента отрицания равнозначности, два элемента И, злемент ИЛИ и элемент НЕ, вход которого является вторым входом блока управляемых полусумматоров и соединен с первыми входами первого элемента И и первого элемента отрицания равнозначности, выход которого является первым выходом блока управляемых полусумматоров, первый вход которого соединен с вторым входом первого элемента И и первым входом второго элемента отрицания равнозначности, выход которого соединен с вторым уходом первого элемента отрицания равнозначности, а второй вход второго элемента отрицания равнозначности является третьим входом блока управляемых полусумматоров и соединен с первым входом второго элемента И, второй вход которого соединен с выходом элемента НЕ, выходы первого и второго элементов И через элемент ИЛИ соединены с первым входом третьего элемента отрицания равнозначности, второй вход которого является четвертым входом блока управляемых полусумматоров, а выход третьего элемента отрицания равнозначности является вторым выходом блока управляемых полусумматоров. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР №36970.6, кл, Н,03 К 13/24, 1970. 2.Филиппов А.Г. и Белкин О,С. Проектирование логических узлов ЭВМ. М., Советское радио, 1974, с.81-83 (прототип).

SM.1

Авторы

Даты

1982-08-30—Публикация

1980-10-08—Подача