1

Устройство относится к области кодирования и преобразования информации.

Известно устройство для деления частоты повторения импульсов на коэффициенты деления, представленные неправильной двоичной дробью с точностью до заданного двончного знака после запятой.

Известное устройство содержит цифровой интегратор, вход независимой переменной которого соединен с источником делимой частоты. Масштабный множитель интегратора равен обратной величине заданного коэффициента деления и предварительно вычисляется, например, вычислительным устройством.

Однако в таком устройстве предварительное вычисление масштабного множителя цифрового интегратора усложняет процесс деления частоты на коэффициенты деления, представленные двоичной дробью.

Цель изобретения - упростить процесс деления частоты на коэффициенты деления, представленные . неправильной двоичной дробью с точностью до заданного двоичного знака после запятой.

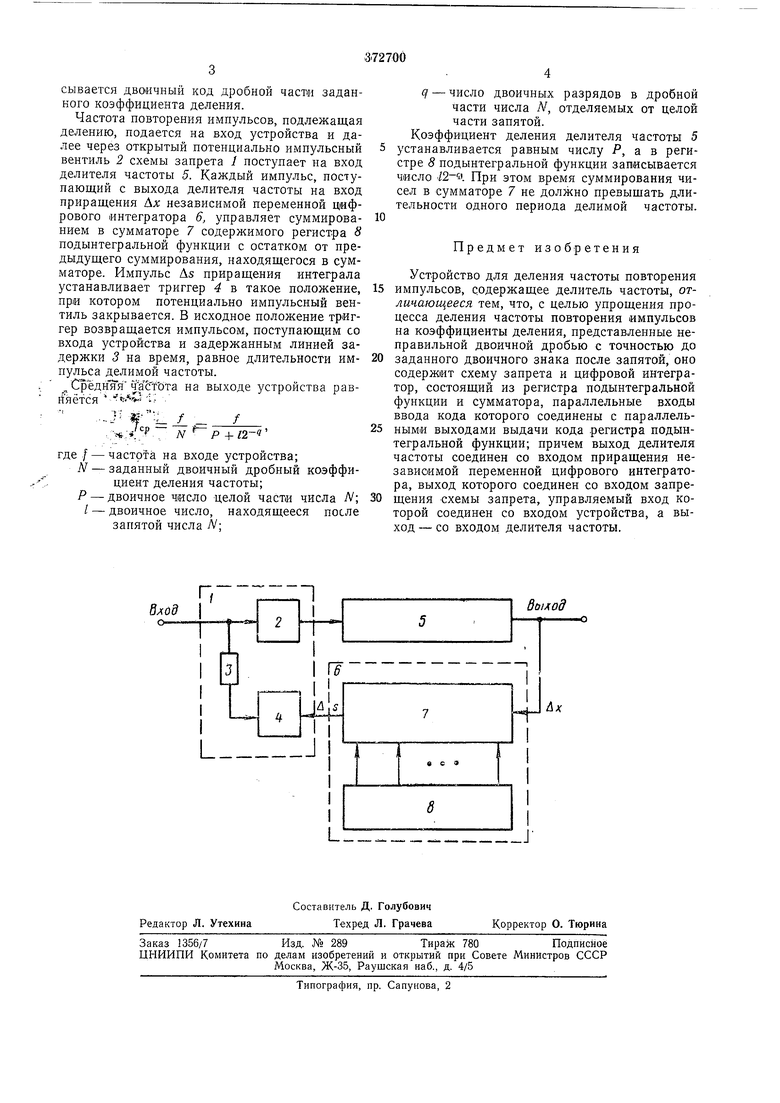

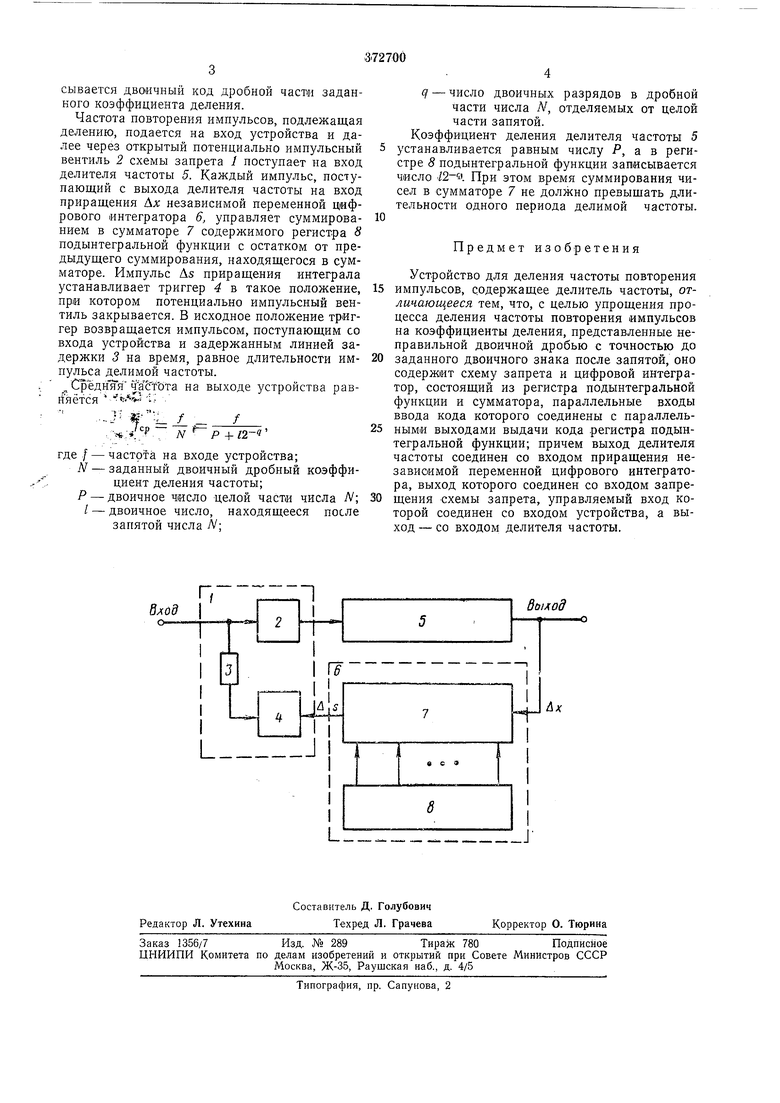

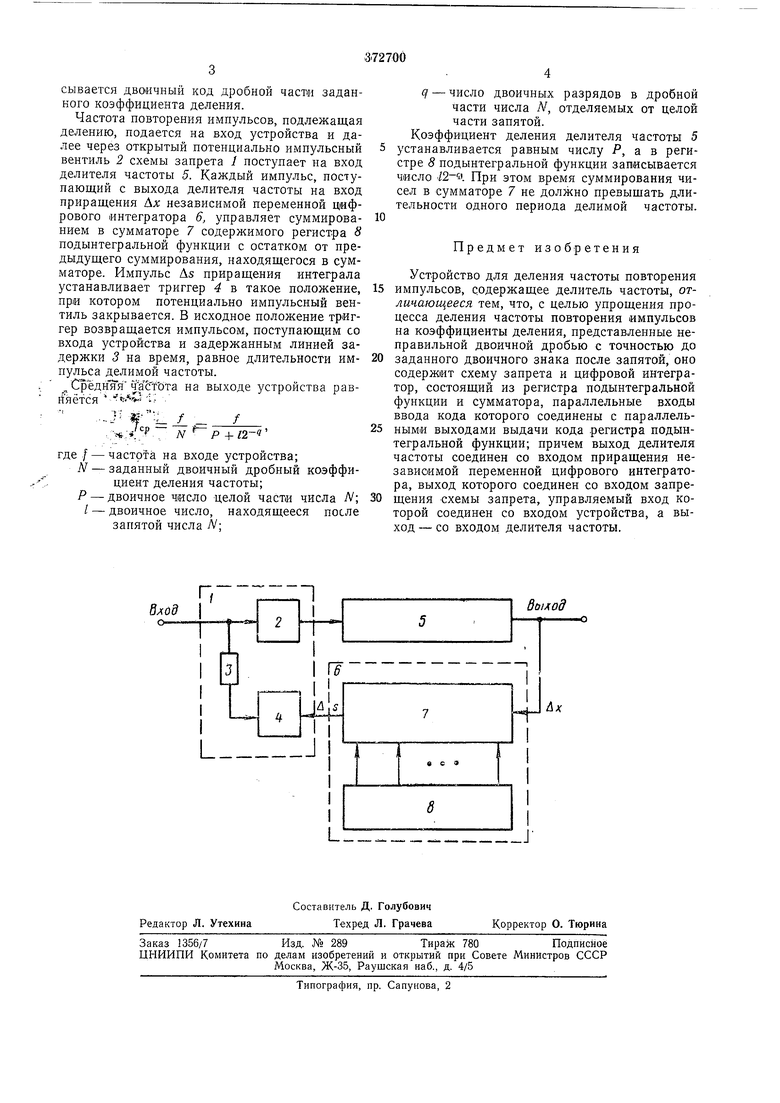

Эта цель достигается тем, что устройство содержит делитель частоты, схему запрета и цифровой интегратор, состоящий из регистра подынтегральной функции и сумматора, параллельные входы ввода кода которого соединены с параллельными выходами выдачи кода

регистра подынтегральной функции. Управляемый вход схемы запрета соединен со входом устройства, а выход - со входом делителя частоты. Выход делителя частоты соединен со входом приращ.ения независимой переменной цифрового интегратора, выход цифрового интегратора - со входом запрещения схемы запрета.

Схема запрета состоит, например, из триггера с разделительными входами управления, линии задержки и потенциально импульсного вентиля, импульсный вход которого соединен со входом устройства, а выход - со входом делителя частоты. Потенциальный вход вентиля соединен с выходом триггера, один из входов которого через линию задержки подключен ко входу устройства, а второй вход соединен с выходом цифрового интегратора.

На чертеже представлена функциональная схема устройства.

Устройство содержит схему запрета /, состоящую из потенциально импульсного вентиля 2, линии задержки 3 и триггера 4, делитель частоты 5, цифровой интегратор 6, состоящий из сумматора 7 и регистра 8 подынтегральной функции.

Коэффициент деления делителя частоты 5 устанавливается равным целой части заданного дробного коэффициента. В регистр 8 запи

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления частоты пов-ТОРЕНия иМпульСОВ | 1979 |

|

SU817891A1 |

| СПОСОБ ДЕЛЕНИЯ ЧАСТОТЫ ПОВТОРЕНИЯ ИМПУЛЬСОВ | 1972 |

|

SU346799A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1973 |

|

SU388277A1 |

| Устройство для моделирования нейрона | 1979 |

|

SU883927A2 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1968 |

|

SU219911A1 |

| Вероятностный коррелометр | 1986 |

|

SU1327121A1 |

| Цифро-частотный интегратор | 1979 |

|

SU935955A1 |

| Цифровой частотомер | 1973 |

|

SU481851A1 |

| Каскад программируемого делителя частоты | 1980 |

|

SU919091A1 |

| Круговой интерполятор для контурных систем программного управления станками | 1973 |

|

SU484502A1 |

Авторы

Даты

1973-01-01—Публикация