{S) циФРО-ЧАСТОТНЫЙ ИНТЕГРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифро-частотный интегратор | 1983 |

|

SU1089580A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1973 |

|

SU388277A1 |

| Сглаживающий преобразователь знакопеременных частотно-импульсных сигналов в код | 1980 |

|

SU869027A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Стохастический интегратор | 1984 |

|

SU1215120A1 |

| ВСЕСОЮСЛЛЛ , HATwiiTIiO - <3>& iтг;:;и(«{?сг:! |•^U'iEKA I | 1964 |

|

SU164487A1 |

| НЕПРЕРЫВНЫЙ ЦИФРОВОЙ ИНТЕГРАТОР | 1969 |

|

SU241121A1 |

| Цифровой интегратор | 1979 |

|

SU840969A1 |

| Генератор напряжения инфранизкой частоты | 1983 |

|

SU1088104A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1990 |

|

RU2015539C1 |

Изобретение относится к вычислительной технике и может быть использовано при построении цифровых интегрирующих машин, цифровых дифференциальных анализаторов, различных цифро-аналоговых и частотно-импульсных вычислительных устройств. Известно цифровое сглаживающее устройство, состоящее из двоичных умнох ителей, реверсивного счетчика, распределителя импульсов,, примем реверсивный очетчик имеет обратную связ с последнего знакового разряда на все р1азряды счетчика, кроме первого, а на входе счетчика подключен распределитель импульсов, управляющие входы которого соединены со знаковыми разрядами. При размыкании контура обратной связи и подаче импульсов приращений на вход распределителя такое устройство MoweT служить цифро-частотным интегратором и позволяет получать зна копеременную подынтегральную функцию l. Известное устройство имеет следующие недостатки: при смене знака подинтегральной функции требуются 2 такта, что ухудшает быстродействие устройства; значение подынтегральной функции представляется в прямом .коде что затрудняет сопряжение такого устройства с ЦВМ, в которой данные представляются как правило в дополнительном двоичном коде. Известно устройство, содержащее регистр подынтегральной функции, в качестве которого ис|1ользуется реверсивный счетчик, опорный делитель частоты и схемы И. ИЛИ, причем выходы счетчика, и делителя частоты соединены со входами схем И, а выходы последних подключены ко входам схемы ИЛИ, выход которой является выходом устройства С2 . Недостатком такого устройства является невозможность использования его при получении знакопеременных значений подынтегральной функции, предтавляемых в дополнительном двоичном оде.

Цель изобретения - расширение (функиональных возможностей за счет получения знакопеременных значений под- 5 нтегральной функции, представляемых в дополнительном двоичном коде.

Поставленная цель достигается тем, что в цифро-частотный интегратор, содержащий реверсивный счетчик, опорный делитель частоты, группу элементов И и элемент ИЛИ, причем вход счетчика подключен к входу приращений подынтегральной функции интегратора, выход каждого разряда счетчика под- 5 ключен к выходной шине подьттегральой функции интегратора, вход опорого делителя частоты подключен к входу опорной частоты.интегратора, первый вход каждого элемента И груп- 20 пы подключен к выходу соответствующего разряда счетчика, второй вход (аждого элемента И группы подключен к соответствующему выходу опорного делителя частоты, выходы элементов И группы подключены к входам элемента ИЛИ, введены триггер знака, три схемы И и триггер, примем вход триггера знака подключен к выходу старшего разряда реверсивного счетчика, 30 выход триггера знака подключен к выходной шине подынтегральной функции к первому входу первого элемента И, второй вход которого подключен к входу опорной частоты интегратора, выходj элемента ИЛИ подключен к пераому входу второго элемента И и устанЪвочному входу триггера, прямой выход которого подключен к второму входу второго элемента И, выход которого яв- -ее ляется первым вь1ходом интегратора, выход первого элемента И подключен k первому входу третьего элемента И и входу сброса триггера, инверсный выход которого подключен к второму 45 входу третьего элемента И, выход которого является вторым выходом интегратора.

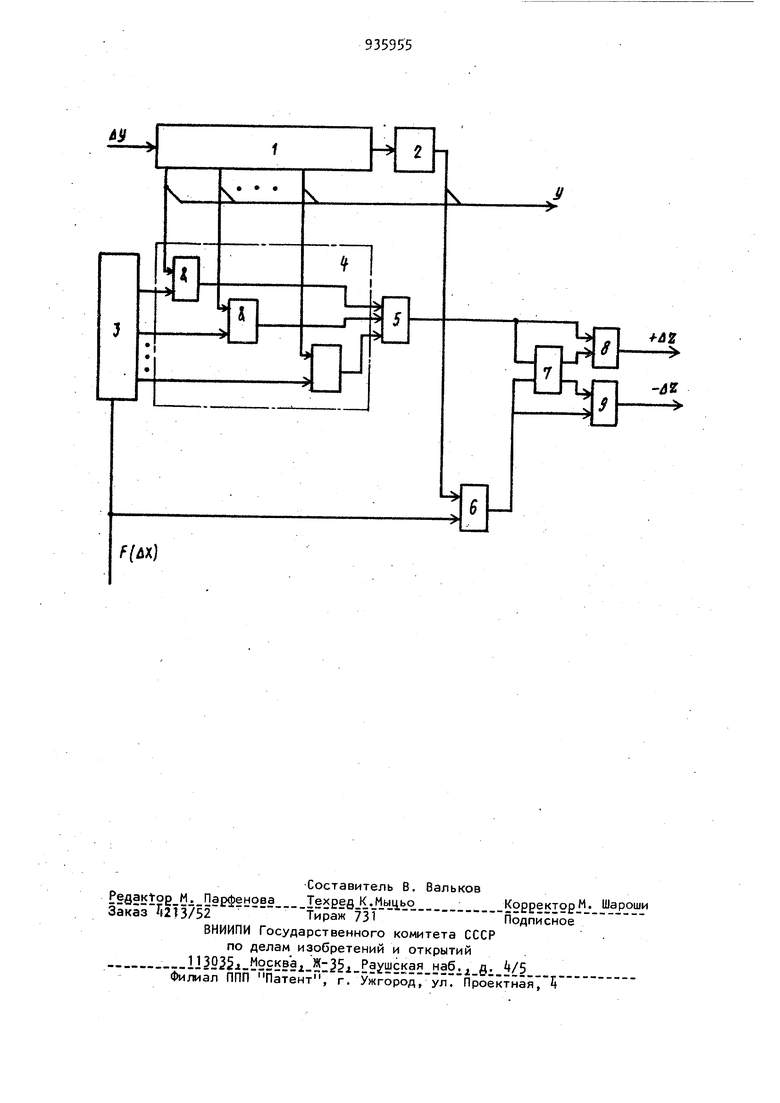

На чертеже изображена структурная схема цифро-частотного интегратора. Интегратор содержит реверсивный четчик 1, триггер знака 2, опорный елитель частоты 3, группу элеменов И k, элемент ИЛИ 5 первый элеент И 6, триггер 7. второй и третий элементы И 8 и 9.

Устройство работает следующим образом.

При положительном значении подынтегральной функции триггер знака 2 находится в нулевом состоянии, первы элемент И 6 закрыт, триггер 7 в единичном состоянии, и на выходе интегратора образуются только положительные приращения в виде импульсов, поступающих через второй элемент И 8 с выхода элемента ИЛИ 5- В этом случае устройство работает точно так же как и известный цифро-частотный интегратор.

Значение кода подынтегральной фунции у определяется суммой поступивших на вход счетчика приращений ду. Делитель частоты осуществляет делени опорной частоты F и Нормирование импульсных последовательностей с часF Р F

Причем эти имтотами 2 2 2 пульсы Vie совпадают друг с другом во времени. Тактовые импульсы, поступающие на вход опорного делителя с частотой Г, представляют собой приращения независимой переменной Дх. На Выход элемента ИЛИ проходят только те импульсные последовательности с опоного делителя частоты, которым соответствуют единичные состояния разрядов счетчика. Таким образом, число входных импульсов (сумма приращений д определяется выражением

К 2 дх.

7 - .-. V i - 775 .2j

K-i

2 1.1 . 0,1 - состояния разрядов

где а

М

счетчика,

или при достаточно малом периоде чередования тактовых импульсов Дх F

JvCxMy.

Z

г

При отрицательном значении подынтегральной функции, которое представляется в дополнительном двоичном коде, триггер знака 2 открывает первый элемент И 6, и число импульсов на выходе устройства представляет собой разность импульсов с выхода элемента ИЛИ и импульсов потока Г. По скольку частота импульсов на выходе элемента ИЛИ 5 всегда меньше частоты Г, то в этом случае на выхЪде третьего элемента И 9 находятся только отрицательные приращения ,Д 2 , число которых определяется выражением

(

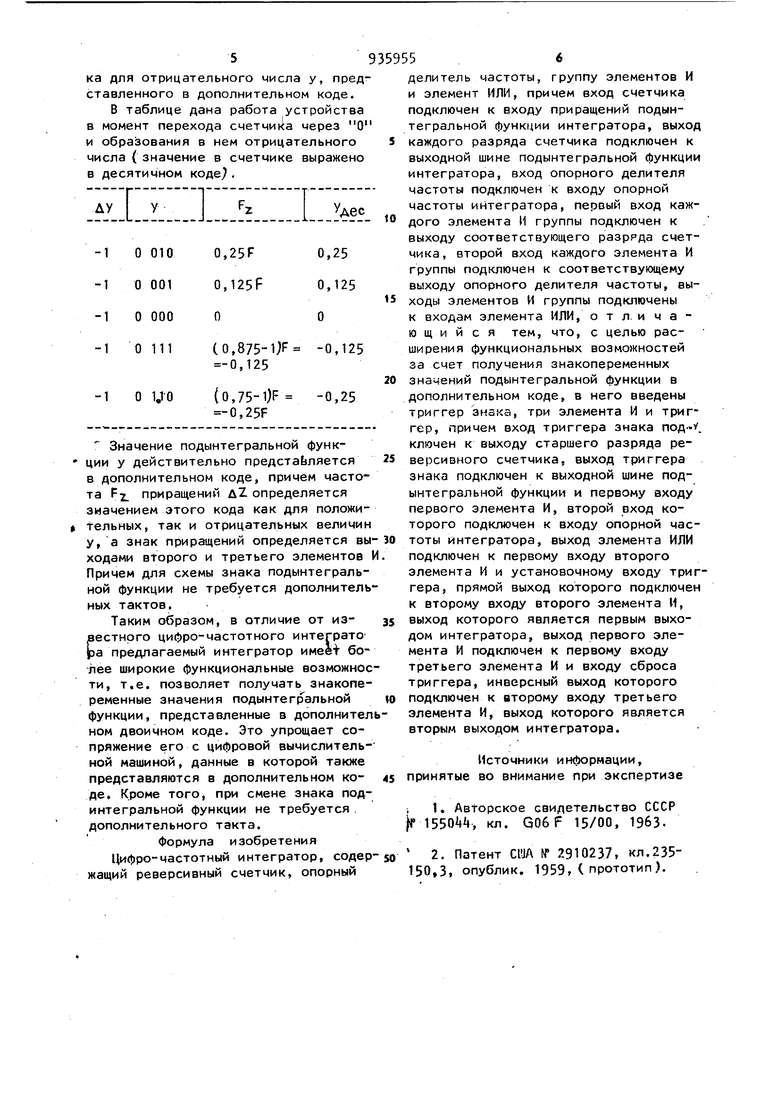

где .. - состояния разрядов счетчика для отрицательного числа у, пред ставленного в дополнительном коде. В таблице дана работа устройства в момент перехода счетчика через О и образования в нем отрицательного числа ( значение в счетчике выражено в десятичном коде. и::; Значение подынтегральной функции у действительно предстаЬляется в дополнительном коде, причем частота р2 приращений дХ определяется значением этого кода как для положи teльныx, так и отрицательных величин у, а знак приращений определяется вы ходами второго и третьего элементов Причем для схемы знака подынтегральной функции не требуется дополнитель ных тактов. Таким образом, в отличие от известнрго цифро-частотного интеграто ра предлагаемый интегратор имее более широкие функциональные возможнос ти, т.е. позволяет получать знакопеременные значения подынтегральной функции, представленные в дополнител ном двоичном коде. Это упрощает сопряжение его с цифровой вычислительной машиной, данные в которой также представляются в дополнительном коде. Кроме того, при смене знака подинтегральной функции не требуется дополнительного такта. Формула изобретения Цифро-частотный интегратор, содер жащий реверсивный счетчик, опорный делитель частоты, группу элементов И и элемент ИЛИ, причем вход счетчика подключен к входу приращений подынтегральной функции интегратора, выход каждого разряда счетчика подключен к выходной шине подынтегральной функции интегратора, вход опорного делителя частоты подключен к входу опорной частоты интегратора, первый вход каждого элемента И группы подключен к выходу соответствующего разряда счетчика, второй вход каждого элемента И группы подключен к соответствующему выходу опорного делителя частоты, выходы элементов И группы подключены к входам элемента ИЛИ, о т л и чающий с я тем, что, с целью расширения функциональных возможностей за счет получения знакопеременных значений подынтегральной функции в дополнительном коде, в него введены триггер знака, три элемента И и триггер, причем вход триггера знака под-v ключен к выходу старшего разряда реверсивного счетчика, выход триггера знака подключен к выходной шине подынтегральной функции и первому входу первого элемента И, второй вход которого подключен к входу опорной частоты интегратора, выход элемента ИЛИ подключен к первому входу второго элемента И и установочному входу триггера, прямой выход которого подключен к второму входу второго элемента И, выход которого является первым выходом интегратора, выход первого элемента И подключен к первому входу третьего элемента И и входу сброса триггера, инверсный выход которого подключен к второму входу третьего элемента И, выход которого является вторым выходом интегратора. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР Г 1550, кл. G06F 15/00, 1963. 2. Патент США № 2910237. кл.235150,3, опублик. 1959, ( прототип).

Авторы

Даты

1982-06-15—Публикация

1979-12-14—Подача