1

Изобретение относится к облает вычислительной техники и может быть использовано при построении цифровых илтегрирующях машин, цифровых дифференциальных анализаторов, различных цифро-аналоговых устройств для систем автоматического управления, частотно-импульсных вычислительных устройств и т. п.

Известен цифровой интегратор, состоящий из регистра подынтегральной функции, в качестве которого -при знакопеременном входном сигнале может быть использован реверсивный счетчик, опорного делителя частоты и двоичного умножителя.

Реверсивный счетчик представляет собой регистр подынтегральной функции Р, значение кода которого определяется суммой поступивших на его вход сигналов Ар. Делитель частоты осуществляет деление опорной частоты Р и формирование на свободных выходах триггеров импульсных последовательF FF

ностей с частотами -, , Импульсы

2 . t

сформированных последовательностей разнесены ъо времени и никогда ие совпадают друг с другом. Тактовые импульсы, поступающие на вход делителя частоты с частотой f, представляют собой приращения независимой переменной Ах или ДЛ Двоичный умно,житель выполнен из « импульсно-потенциальных схем «И, на импульсные входы которых поступают Приращения независимой переменной с частотами -- , а на потенциальные -

А

ВЫХОДЫ соответствующих триггеров регистра подынтегральной функции. Имяульсы, проходящие через открытые схемы «И, подаются через схему «ИЛИ на выход устройства. Если бы импульсы, выходящие из интегратора, были размещены во времени равномерно, то число выходных импульсов было бы пропорционально времени и имело бы место равенство

У

(1)

или при Достаточно малом периоде чередования тактовых импульсов Дл;

л

)dx.

(2)

Однако известное устройство имеет кроме

погрешностей квантования дополнительную

погрешность, обусловленную флуктуацией

частоты выходных импульсов двоичного: :умножятеля.

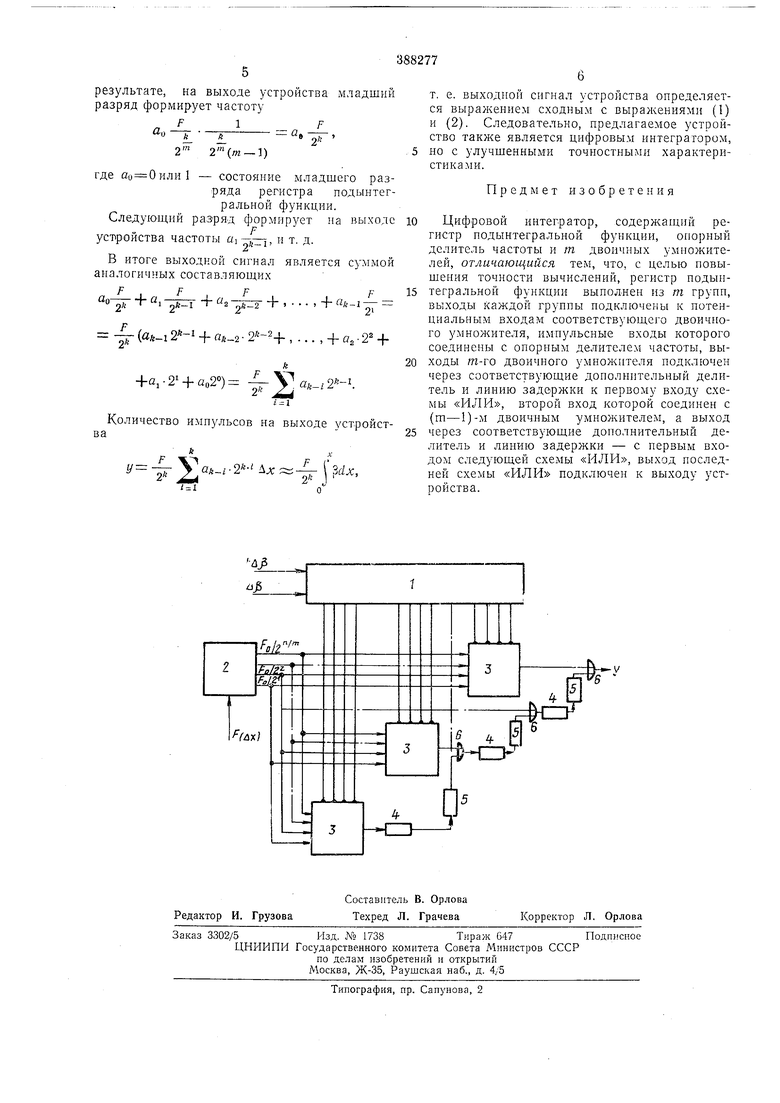

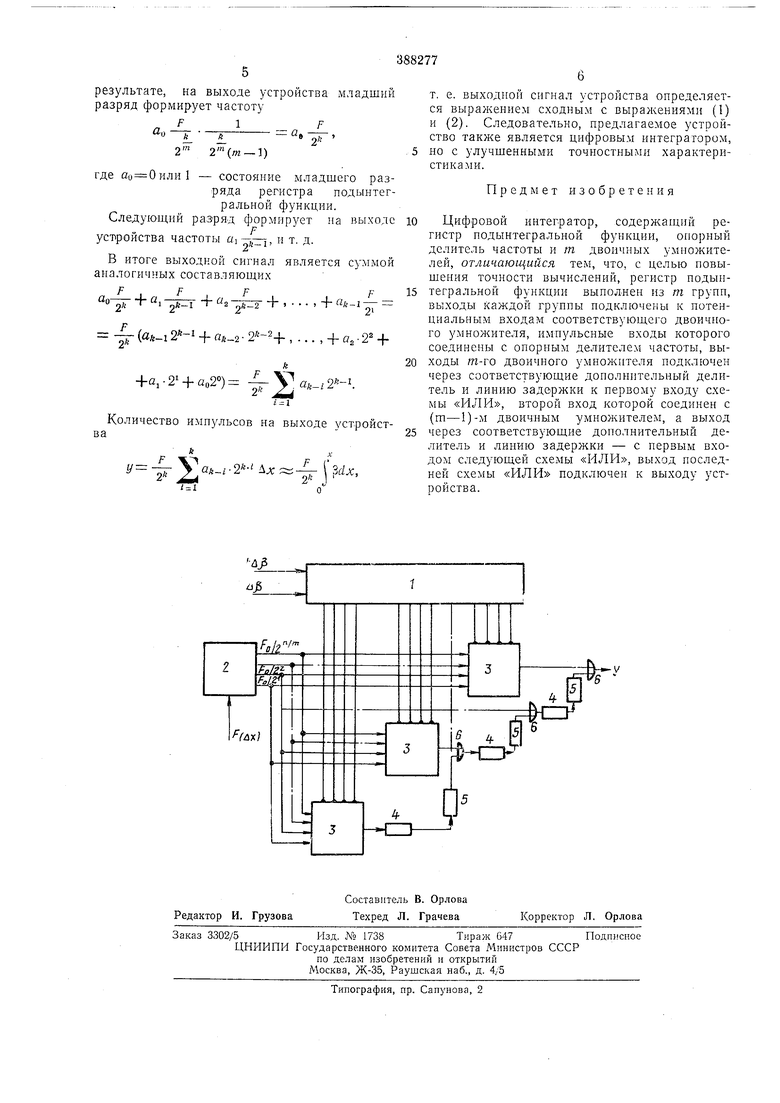

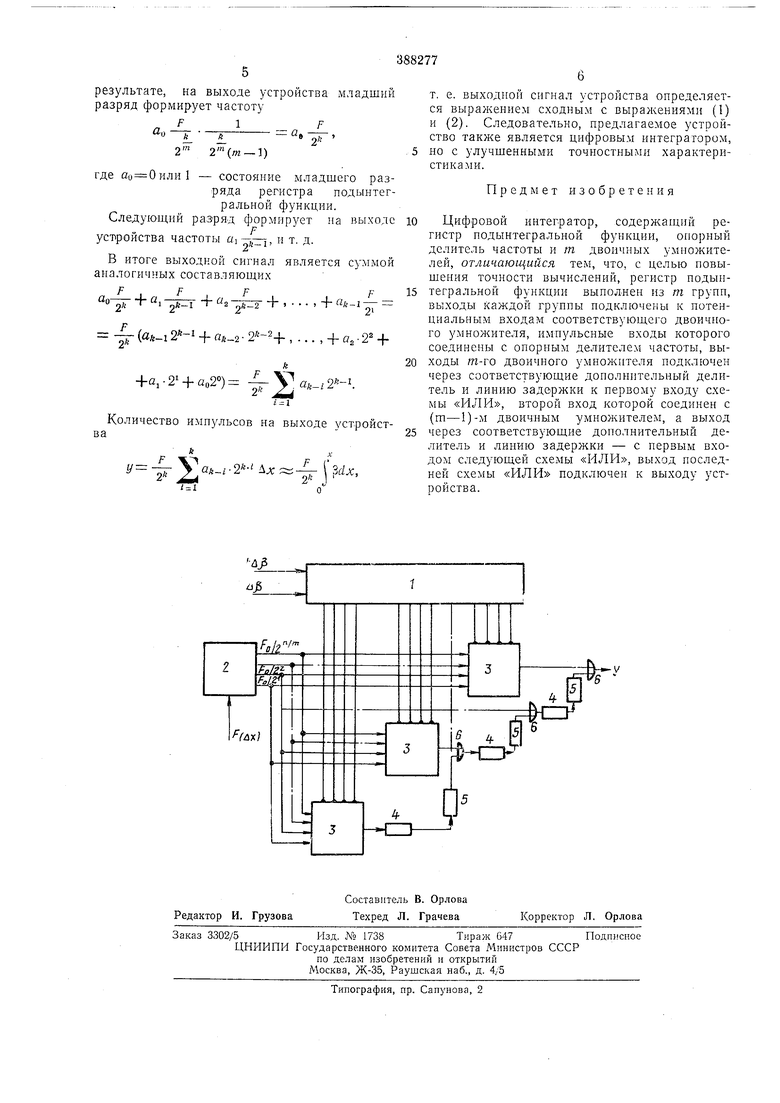

При постояинам значении подынтегральной функции погрешность двоичного умножителя носит знакопеременный характер и за период младшей опорной частоты равный -успедняетсЕ. , F 5 Максимальное значение мгновенной погрешности определяется +т + т - 0,39+0,167 Ппн изменении кода регистра подынте „пй л™ии т е при подаче на его вход сигнал / А8 частота следования которо-is вход сигнала ар, 4di.iu го в общем случае отлична от п У редне,.ы пыхояной частоты двоичного умножитея соответствующй каждому состоянию кода не осуще-вляется, что .Р.ВОДИТ Sb ТьГзванна Гем,Г ;сТеднение флуктуиоующей частоты двоичного умножителя ПРОИСХОДИТ за время, отличное от периода младшей опорной частоты делителя, появив- 25 ГдТд«™с Гм „руеТсГ°„ ТГплГа Й; Поичем величина погрешности возрастает с увеличением частоты следования сигнала др. %1 Гдаче на в- интегратора зо др, частота Д ования 1пульсов превышает младшую опорную частоту д ного умножителя - (что чаще всего бывает .-.o.,lv ппчникают дополни- 35 в шстемах) возник тельные погрешности, ызванн ые , тельные auipcmnuA in, „„.. время существования каждого фиксирован ного состояния кода реверсивного счетчика не все его разряды успеют «опроситься импульсами опорных частот. Цель изобретения - новышение точности работы цифрового интегратора. Это достигается разбиением ft-разрядного реверсивного счетчика на m групп, триггеры реверсишо™ счетчика «а ш J У - j;;-: -- -..„„ „„„. потенциалькаждой ИЗ групп управляю 1 и ным входам работой - -разрядных двоич ных умножителей, на импульсные входы которых с делителя частоты (количество разрядов в нем сокращено от /е до - , т. е. в m 50 РРР раз) поступают опорные частоты-,-°,...,- i а выходные сигналы каждого из которых чеК „.„.,. п.питрли СУММИРУЮТСЯ с резразрядные делители суммируются с выходным сигналом последующего. . В результате увеличения в 2 раз младшей опорной частоты двоичного умно(к-) жителя в 2 раза возрастает частота «опроса триггеров регистра подынтеграль- 65 40 60 ной функции, что приводит к повышению точности Перехода от формулы (3) к формуле (4), т. е. численное интегрирование идет с более мелким шагом, а следовательно, более точно. Разбиение двоичного умножителя на групп с меньшим количеством разрядов --, групп с меньшим количеством разрядов приводит к уменьшению максимальной погрешности в каждом из них в соответствии с выражением (3), где вместо k теперь необхомо поставить -, а постановка дополнительных делителей обеспечивает ее снижение за счет сглаживания. Следовательно, в результате некоторого изменения .структуры устройства, практически увеличения количества оборудования, повышается точность его работы и .расширяется диапазон изменения входного аргумента Др. На чертеже показана схема цифрового ин- L aeMoe устройство состоит из регистра ; подынтегральной функции, .-р азрядного опорного делителя 2 частоты, - « разрядных двоичных умножителей ,разр,д„нх (я.-,) до„олн„ель„ь,х делителе 4, А .разрядных (т-1) линий 5 задержки, «,.тлпы г (l,,,, ,, ..единены с подынтегральной функ потенциальные выходы триггеров реги потенциальными входами группы двоичных умножителей, импульсные входы умножителей - с выходами опорного дели. частоты, выход младшего из них - с входам дополнительного делителя частоты. Выход дополнительного делителя частоты через линию задержки -подключен к одному из входов схемы «ИЛИ, к второму входу схемы «ИЛИ - выход следующего двоичного умножителя, а выход схемы «ИЛИ - к входу дополнительного делителя частоты, выход „,-Г;одсоеди„е„ к цепоч из аиалсп.IVUlUjpUlu jnj.,. -ii чных схем. Выход последней схемы «ИЛИ, чных схем. Выход последней схемы «ИЛИ, к одному из входов которой подключен выход старшего двоичного умножителя, является выходной щиной устройства. Устройство работает следующим образом. В регистре / подынтегральной функции накапливается код р. Устройство формирует выходной сигнал в соответствии с выражениями (1) и (2), т. е. выполняет те же функНИЯМИ i) и ,, 1. с. Dui.iv.v,..... . „ .. ции, что и обычный двоичный умножитель, ,, но с более высокой точностью. При этом младший разряд регистра подынтегральной функции управляет работой вентиля, коммутирующего частоту - делителя частоты. С выхода младшегс двоичного умножителя эта частота проходит (т-1) дополнительный деJLлитель 4 с коэффициентами деления 2 . В

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ИНТЕГРАТОР | 1968 |

|

SU219911A1 |

| Цифро-частотный интегратор | 1979 |

|

SU935955A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2220440C1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1990 |

|

RU2015539C1 |

| ДВОИЧНЫЙ УМНОЖИТЕЛЬ | 1992 |

|

RU2006918C1 |

| Число-импульсное устройство для вычисления обратного тригонометрического тангенса | 1983 |

|

SU1092498A1 |

| ОЮЗНАЯ | 1973 |

|

SU375796A1 |

| Устройство для деления частоты пов-ТОРЕНия иМпульСОВ | 1979 |

|

SU817891A1 |

| Вычислительное устройство | 1983 |

|

SU1080137A1 |

| Цифровой интегратор последовательного переноса | 1986 |

|

SU1357956A1 |

Даты

1973-01-01—Публикация