Изобретение относится к и.мшульсной технике и может быть применено для связи между электронными устройствами, выполненными на интегральных микросхемах транзисторнотранзисторной логики с устройствами, выполненными на навесных элементах.

Известны устройства для согласования интегральных элементов транзисторно-транзисторной логики с выходными узлами, выполненными на навесных элементах, содерж&щие источник напряжения питания, интегральный элемент, выполненный на многоэмиттерном транзисторе и выходном транзисторе, ключевой транзистор и два диода.

Предложенное устройство отличается от известных тем, что в нем коллектор выходного транзистора соединен с базой ключе.вого транзистора и с дополнительным источником напряжения питания через последовательно включенные первый диод и резистор, точка соединения которых через второй диод подключена к коллектору ключевого транзистора и к выходной шине устройства. Эмиттеры выходного и ключевого транзисторов соединены с источником напряжения смещения.

Это позволяет увеличить надежность и выходную мощность устройства.

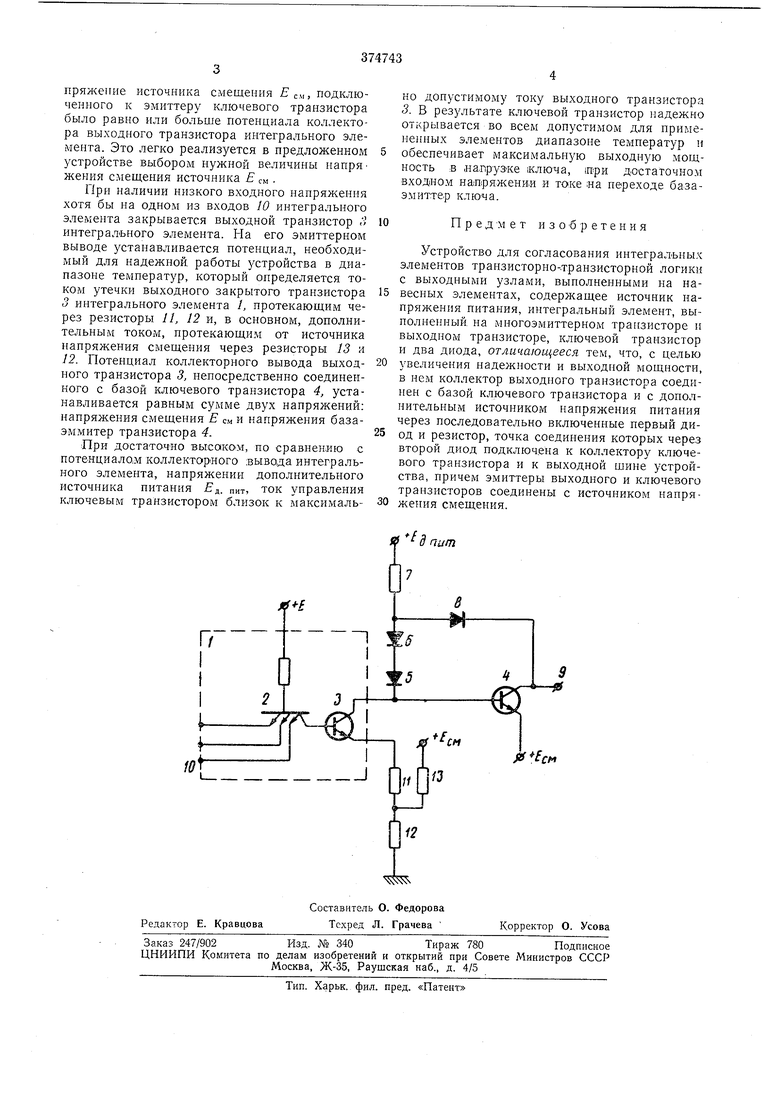

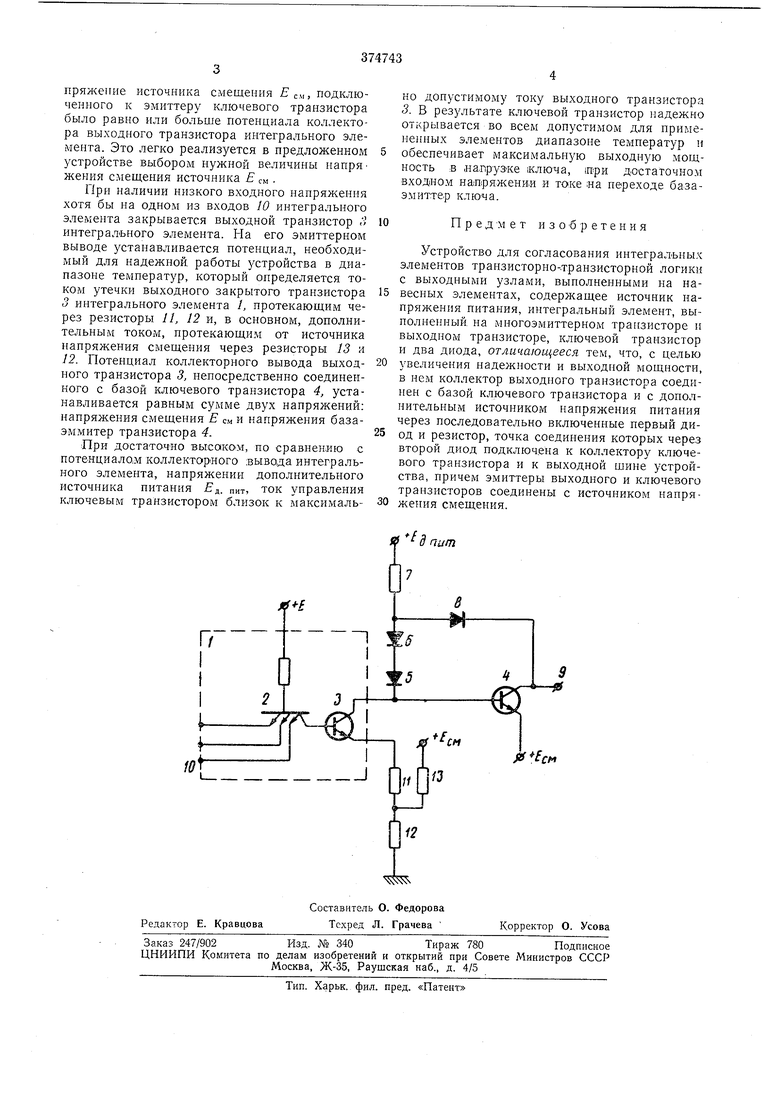

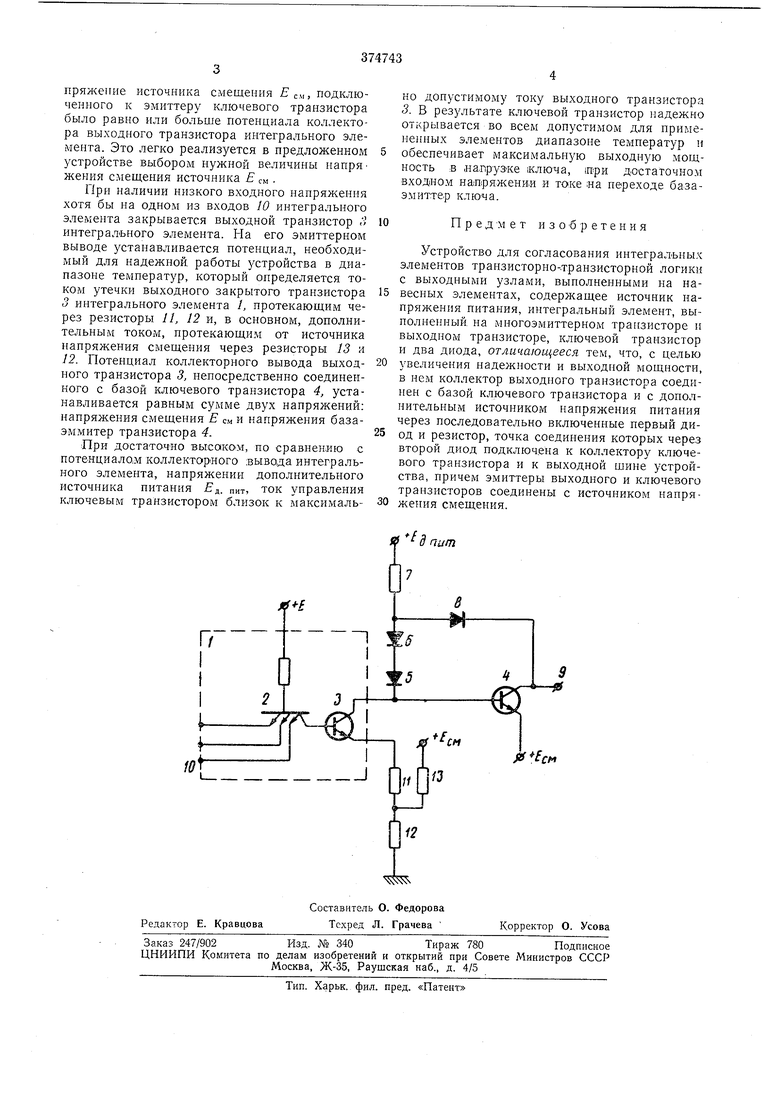

Предложенное устройство изображено на чертеже.

Интегральный элемент 1 содержит многоэмиттерный транзистор 2, источник питания Е, выходной транзистор 3, коллектор которого соединен с элементами, выполненными навесным монтажом, с базой ключевого транзистора 4 и с дополнительным источником напряжения Ед. пиг через диоды 5, 6 и резистор 7, точка соединения которых через диод 5 соединена с коллектором ключевого транзистора -/ и с выходной шиной 9При наличии высокого уровня на всех входах 10 интегрального элемента выходной транзистор 3 интегрального элемента открыт, и ток идет от дополнительного высоковольтного источника нанрял ения Е д. „ит через резистор 7, диоды 5, 6, открытый выходной транзистор 3, резнсторы //, 12.

В результате протекания тока на резисторах 11, ,12 напряжение падает, что обеспечивает нормальную работу интегрального элемента I/, а на коллекторном выводе выходного транзистора появляется нотенциал, равный сумме падения напряжения на резисторах 11, 12 и напряжения эмиттер-коллектор открытого выходного транзистора интегрального элемента.

Для надежного закрытия ключевого транзистора необходимо, чтобы во всем диапазоне температур управляющее напряжение базаэмиттер было приложено в направлении, запирающем переход, т. е. необходимо, чтобы напряжение источника смещения см, подключенного к эмиттеру ключевого транзистора было равно или больше потенциала коллектора выходного транзистора интегрального элемента. Это легко реализуется в предложенном устройстве выбором нужной величины напря жения смещения источника Е см .

Прп наличии низкого входного напряжения хотя бы на одном пз входов 10 интегрального элемента закрывается выходной транзистор Л интегрального элемента. На его эмиттерном выводе устанавливается потенциал, необходимый для надежной, работы устройства в диапазоне температур, который определяется током утечки выходного закрытого транзистора 3 интегрального элемента /, протекающим через резисторы П, 12 и, в основном, дополнительным током, протекающим от источника напряжения смещения через резисторы 13 и 12. Потенциал коллекторного вывода выходного транзистора 3, непосредственно соединенного с базой ключевого транзистора 4, устанавливается равным сумме двух напряжений; напряжения смещения Е см и напряжения базаэммитер транзистора 4.

При достаточно высоком, по сравнению с потенциалам коллекторНОГо вывода интегрального элемента, напряжении дополнительного источника питания Е, „ит, ток управления ключевым транзистором близок к максимально допустимому току выходного транзистора 3. В результате ключевой транзистор надежно открывается во всем допустимом для примененных элементов диапазоне температур и обеспечивает максимальную выходную мощность ,в ,на.пруЗке ключа, три достаточном входном напряжении и токе на переходе базаэмиттер ключа.

Предмет изобретения

Устройство для согласования интегральных элементов транзисторно-транзисторной логики с выходными узлами, выполненными на навесных элементах, содержащее источник напряжения питания, интегральный элемент, выполненный, на многоэмиттерном тра 1зисторе и выходном транзисторе, ключевой транзистор и два диода, отличающееся тем, что, с целью увеличения надежности и выходной мощности, в нем коллектор выходного транзистора соединен с базой ключевого транзистора и с дополнительны.м источником напряжения питания через последовательно включенные первый диод и резистор, точка соединения которых через второй диод подключена к коллектору ключевого транзистора и к выходной шине устройства, причем эмиттеры выходного и ключевого транзисторов соединены с источником напряжения смещения.

fdni

Пит

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| Элемент для согласования насыщенных и ненасыщенных логических схем | 1972 |

|

SU438119A1 |

| Одновибратор | 1978 |

|

SU733088A1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ДЛЯ ВОЗБУЖДЕНИЯ ДЛИННЫХ ЛИНИЙ | 1973 |

|

SU364106A1 |

| Интегральный логический элемент и-не | 1978 |

|

SU790333A1 |

| Элемент транзисторно-транзисторной логики | 1986 |

|

SU1336225A1 |

| Транзисторно-транзисторный логический элемент "и-или-не | 1977 |

|

SU790331A1 |

| Транзисторно-транзисторный логический элемент | 1983 |

|

SU1128387A1 |

| Многофункциональный пороговый модуль | 1973 |

|

SU493030A1 |

Авторы

Даты

1973-01-01—Публикация