Предлагаемое устройство относится к области автоматики и вычислительной техники и может быть использовано при реализации технических средств цифровой автоматики и дискретных вычислительных машин.

Известен комларатор двоичных чисел, содержащий два 2п-разрядных регистра и последовательно соединенные пороговые элементы. Однако известные устройства сложны и имеют время распространения сигнала, равное примерно пт, где т-задержка сигнала в одном разряде.

Предлагаемый компаратор отличается от известных тем, что в нем применено п пороговых элементов с порогом ( + 4) и пятью входами, два из которых имеют веса ( + 2), а остальные - ( + 1), прямые выходы каждого i-ro разряда первого регистра (,3... 2,,1 ) и инверсные выходы каждого одноименного разряда второго регистра связаны с-двумя из входов с весом ( + 1) /-го порогового элемента (, 2,...п), соответственно, а прямые выходы каждого (i+l)-ro разряда первого регистра и инверсные выходы каждого одноименного разряда второго регистра соединены с двумя другими входами с весом {Ч-2) того же /-ГО порогового элемента соответственно: пятый вход первого порогового элемента связан с шиной контрольного сигнала, у пятые входы всех

последующих пороговых элементов связаны с выходами предыдущих: выход последнего порогового элемента связан с выходной шиной устройства.

Это позволяет упростить устройство и

повысить его быстродействие.

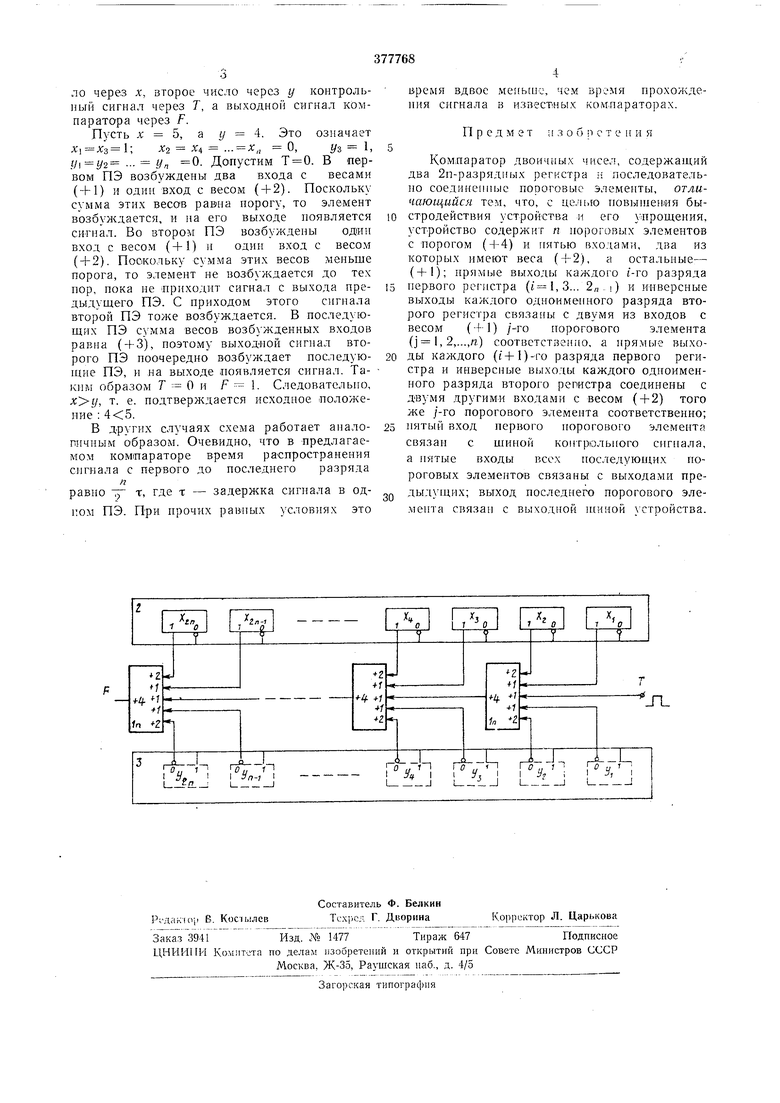

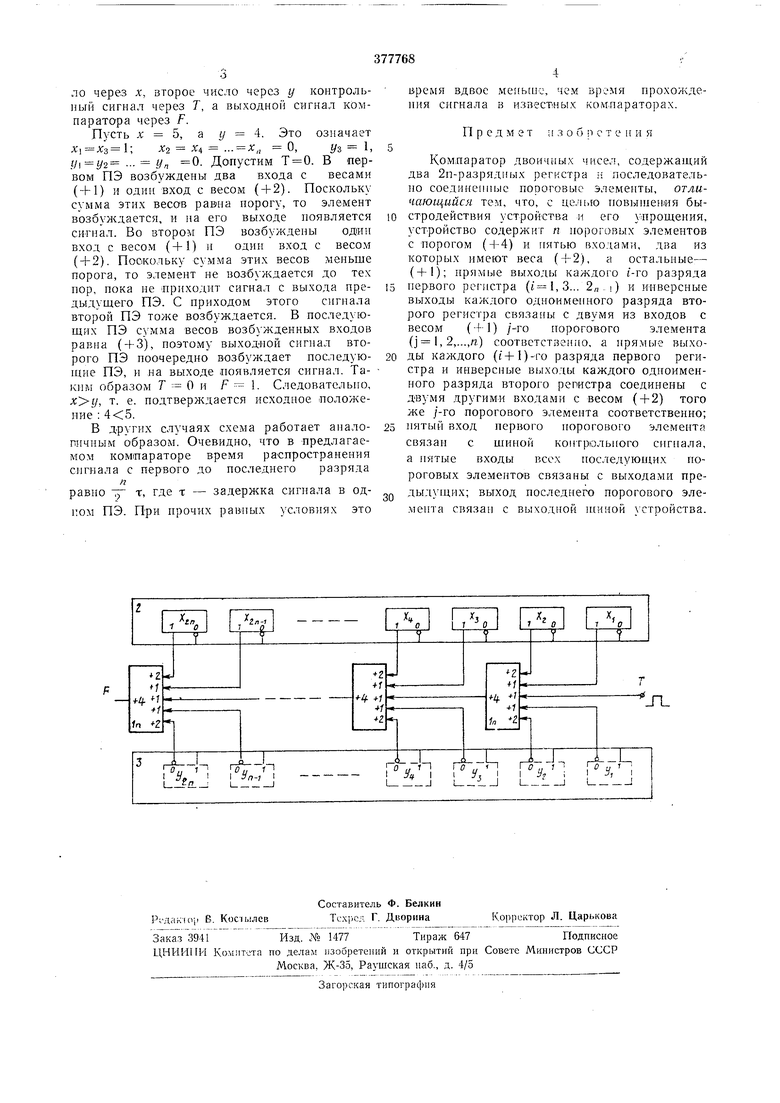

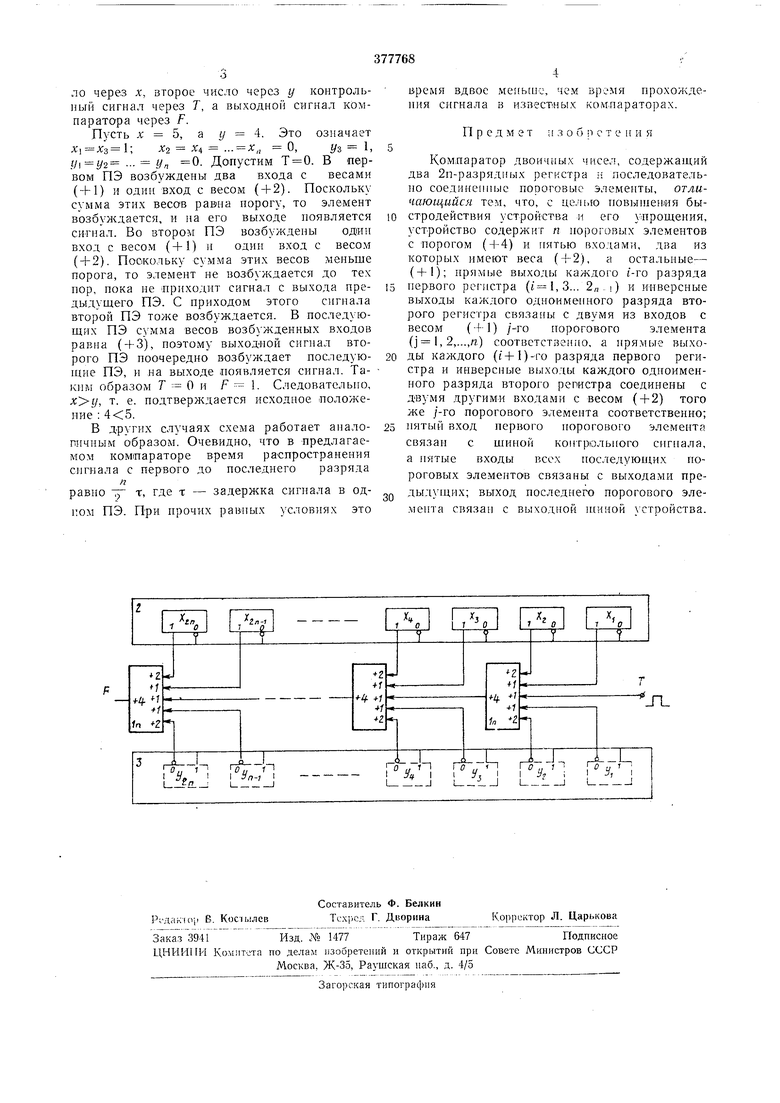

На чертеже приведена блок-схема предлагаемого комларатора,

Он содерл-сит п пороговых элемептов

(li, lo,... « ) и два регистра 2 и 3, предназначенные для приема сравниваемых чисел. На каждые два разряда сравниваемых двоичных чисел используется один пороговый элемеит (ПЭ), который имеет порог ( + 4) и

пять входов, два из которых имеют вес ( + 2), а остальные три имеют вес (+1). Одни из входов с весом ( + 2) подключен к прямому выходу триггера данного разряда первого числа, второй вход с весом ( + 2) подключей к инверсному выходу триггера данного разряда второго числа, один из входов с весом ( + 1) подключен к прямому выходу триггера предыдущего разряда первого числа, второй вход с весом ( + 1) лодключен к

инверсному выходу триггера предыдущего разряда второго числа, а третий вход с весом ( + 1) подключен к выходу предыдущего порогового элемента.

Работу предлагаемого компаратора рассмотрим на примере. Обозиачим первое число через х, второе число через у контрольный сигнал через Т, а выходной сигнал компаратора через F.

Пусть Л 5, а i/ 4. Это означает Х2 х ... х„ 0, Уз 1, Уп 0- ДОПустим Т 0. В первом ПЭ возбуждены два входа с весами ( + 1) и одии вход с весом { + 2). Поскольку сумма этих весов равна порогу, то элемент возбуждается, и на его выходе ноявляется сигнал. Во втором ПЭ возбуждены один вход с весом (+1) и один вход с весом ( + 2). Поскольку сумма этих весов меньше порога, то элемент не возбуждается до тех пор, пока не приходит сигнал с выхода предыдущего ПЭ. С приходом этого сигнала второй ПЭ тоже возбуждается. В последующих ПЭ сумма весов возбужденных входов равна ( + 3), поэтому выходной сигнал второго ПЭ поочередно возбуждает последующие ПЭ, и на выходе появляется сигнал. Таким образом Г - О п F 1. Следовательно, , т. е. подтверждается исходное положение : .

В других случаях схема работает аналоличным образом. Очевидно, что в предлагаемом компараторе время распространения снгнала с первого до последнего разряда

/г

равно Д - задержка сигнала в одном ПЭ. При прочих условиях это

время вдвое меныне, чем время прохождения сигнала в известеных компараторах.

Предмет и з о б р о

Компаратор двоичиых чисел, содержащий два 2п-разрядиых регистра н последовательно соединенные пороговые элементы, отличающийся тем, что, с целью повьпнения быстродействия устройства и его упрощения, устройство содержит п пороговых элементов с порогом (+4) и пятью входами, два из которых имеют веса ( + 2), а остальные- (+1); прямые выходы каждого t-ro разряда первого регистра (,3... 2п-) и нпверсные выходы каждого одноименного разряда второго регистра связаны с двумя из входов с весом (+1) /-ГО норогового элемента (j 1,2,...,,) соответственио, а прямые выходы каждого (( + 1)-го разряда первого регистра и инверсные выходы каждого одноименного разряда второго регистра соединены с двумя другими входами с весом ( + 2) того же /-ГО порогового элемента соответствеипо; нятый вход первого порогового элемента связан с щиной контрольного сигнала, а нятые входы всех иоследуюохих пороговых элементов связаны с выходами предыдущих; выход последнего порогового элемента связан с выходной 1пииой устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения числа,ближАйшЕгО K зАдАННОМу | 1979 |

|

SU809166A1 |

| Генератор случайных чисел | 1984 |

|

SU1310813A1 |

| Устройство для сравнения чисел | 1980 |

|

SU932486A1 |

| Сумматор с контролем | 1979 |

|

SU788108A1 |

| Амплитудный временной квантователь с регулируемым порогом | 1982 |

|

SU1345150A1 |

| Устройство для выделения экстремальных чисел | 1983 |

|

SU1109736A2 |

| Устройство для контроля равновесного кода | 1987 |

|

SU1580563A1 |

| Устройство для умножения | 1988 |

|

SU1571574A1 |

| Пороговый элемент | 1986 |

|

SU1387191A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587641A1 |

Авторы

Даты

1973-01-01—Публикация