Изобретение относится к вычислительной технике и может быть использовано.при построении ЦВМ повышенной надежности. Известен сумматор с контролем ошибок, каждый разряд которого содер)шт одноразрядный сумматор, входы и выходы которого подключены к декодирующему преобразователю, выходы Которого через э ииттерный повторител подключены к схеме неравнозначности, второй вход которой соединен с шиной опорного напряжения. Выходы схем неравнозначности всех разрядов соединены через многовходовой элемент ИЛИ с шиной ошибки. В таком сумматоре обнаружение ошибок осуществляется на основе закономерности, заключающейся в том, что при правильной работе арифметическая сум ма инверсных входных сигналов одноразрядного сумматора к сигна.,и суммы, взятых с единичными весами, и сигнала переноса в следующий разряд, взятого с весом, равным 2, всегда равна 3. При неправ1-шьной работе это соотношение нарушается, что определяется схемой неравнозначности 1. Наиболее близким техническим решением к изобретению является контролируемый п-разрядный сумматор, каждый разряд которого содержит два полусумматора для формирования сумм по модулю 2 и переносов, элемент ИЛИ, объединяющий выходы переносов полусумматоров, элементы И и НЕ н два пороговых элемента, подключенных к прямым и инверсным входам и выходам полусумматоров и элемента ИЛИ. Выходы пороговых элементов всех разрядов подключены через многовходовой элемент ИЛИ к ишне ошибки сумматора. При правильной работе сумматора сумма входов пороговых элементов равна константе, при неправильной работе сумма входов одного из пороговых элементов превышает значение константы (порога) и на его выходе появляется сигнал ошибки 2. Недостатком известных сумматоров являются значительные аппаратурные затраты. Цель изобретения - сокращение аппаратурных затрат. Поставленная цель достигается тем, что в сумматоре с контролем, содержащем элемент

ИЛИ, n одноразрядных сумматоров, соединенных последовательно цепями переноса, n пороговых элементов с порогом на 6, причем выходы всех пороговых элементов соединены с соответствуюищми входами элемента ИЛИ, выход которого является выходом устройства, первый, второй и третий входы каждого одноразрядного сумматора соединены соответственно с ишнами i-ro разряда первого, второго операнда и с выходом переноса одноразрядного сумматора (i-1)-го разряда, шина i-ro разряда первого операнда соединена с первым входом с весом 1 i-ro порогового элемента и, с первым инверсным входом с весом 1 (i+l)-r порогового элемента,, шина 1-го разряда второго операнда соединена со вторым входом с весом 1 |-го порогового элемента и со вторым инверсным входом с весом 1 (i+l).roi порогового элемента, шина переноса из (i-l)-ro разряда соединена с третьим входом с весом 1 1-го порогового элемента и с третьим инверсным входом с весом 1 (i+l)-ro порогового элемента, выход суммы i-ro одноразрядного сумматора соединен с первым инверсным входом с весом 1 i-ro порогового элемента и с первым входом с весом 1 (i+l)-ro порогового элемента, выход переноса i-ro одноразрядного сумматора соединен, со вторым инверсным входом с весом 1 i-ro порогового элемента и со вторым входом с весом 1 (i+l)-ro порогового элемента, шина (i+l)-ro разряда первого операнда соединена с четвертым входом с весом 1 i-ro порогового элемента и четвертым инверсным входом с весом 1 (i+l)-ro порогового элемента, шина (i+l)-ro разряда второго операнда соединена с пятым входом с весом 1 i-ro порогового элемента и с пятым инверсным входом с весом 1 (i + l)-ro порогового элемента, выход суммы (i + l)-ro одноразрядного сумматора соединен с третьим инверсным входом с весом 1 i-ro порогового элемента и с третьим входом с весом 1 (i+l)-ro порогового элемента, выход переноса (i+l)-ro одноразрядного сумматора соединен с четвертым инверсным входом с весом 2 i-ro порогового элемента и четвертым входом с весом 2 (i+l)-ro порогового элемента,

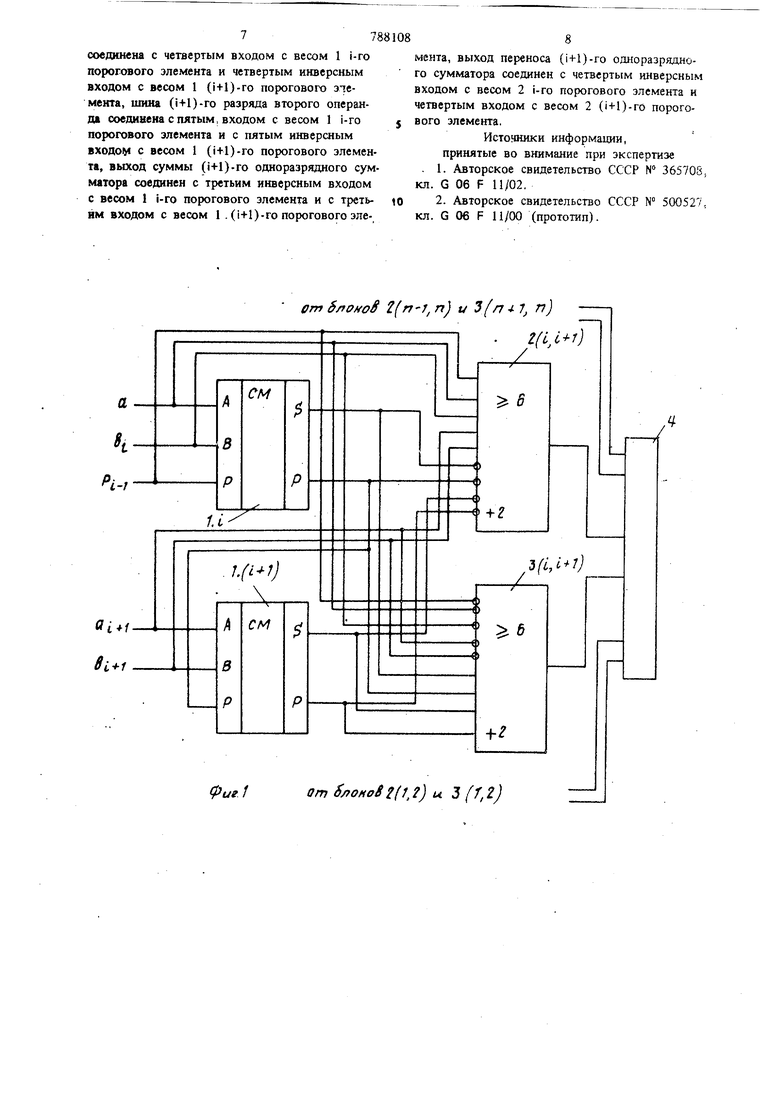

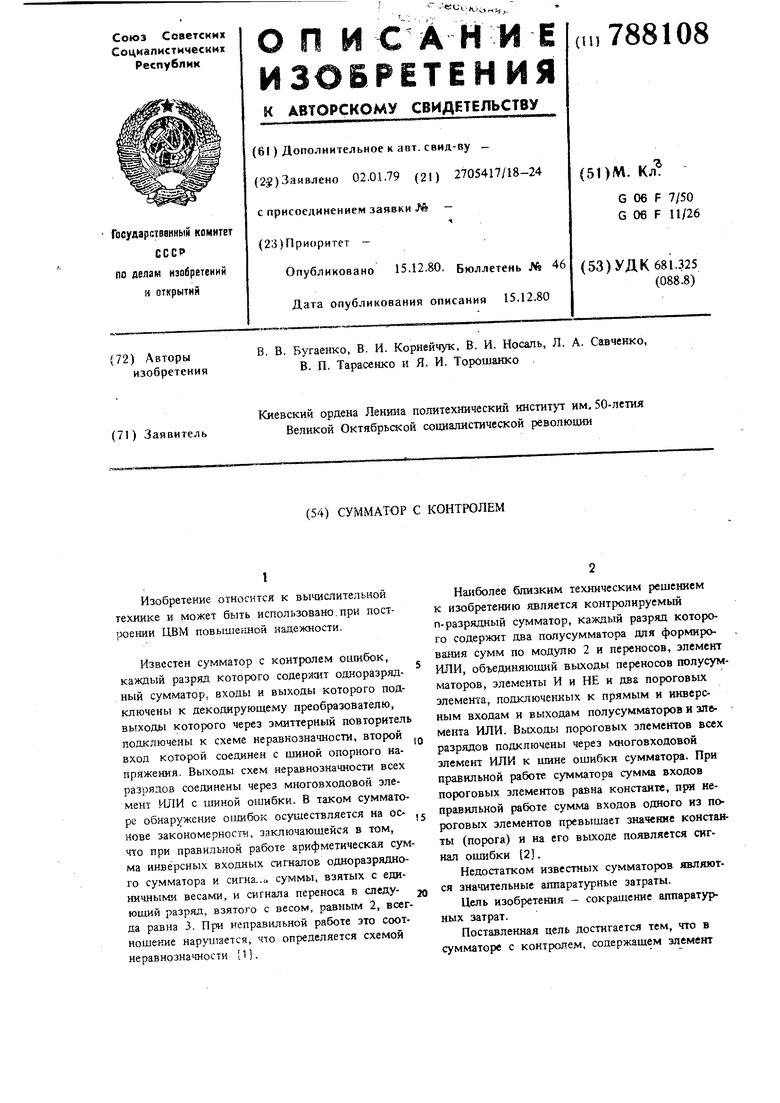

На фиг. 1 изображена функциональная схема i-ro и (i+l)-ro разрядов сумматора; на фиг. 2 - таблица, поясняющая работу сумматора.

Устройство содержит n одноразрядных сумматоров 1, соединенных последовательно цепями переноса. Входы каждого одноразрядного сумматора 1 подключены ко входам соответствующих разрядов операндов. Ко входам и выходам каждого i-ro 1 i и (i+l)-ro l.(i+l) одноразрядных сумматоров подключены два девятивходовых пороговых элемента 2

(i, i+1) и 3.(i, i+1) с порогами срабатывания, равными 6. Обозначение пороговых элементов 2,(i, 1+1) и 3.(i, i+1) говорит о том, что пороговые элементы относятся к i-му и (i+l)-M разрядам сумматора. Входы с весом 1 порогового элемента 2. (i, i+1) подключены ко входам операндов одноразрядных сумматоров l.i и l.(i+l), ко входу переноса одноразрядного сумматора 1,1. Инверсные входы с весом 1 этого порогового элемента подключены к выходам сумм одноразрядных сумматоров i.j и l.(i+l) и к выходу переноса одноразрядного сумматора 1.1, Инверсный вход порюгового элемента с весом 2 подключен к выходу переноса одноразрядного сумматора l,(i+l). Инверные входы с весом 1 порогового элемента 3.(1, 1+1) подключены ко входам операндов одноразрядных сумматоров 1. i и l.(i+l), ко входу переноса одноразрядного сумматора l.i. Прямые входы с весом 1 этого порогового элемента подключены к вь ходам сумм одноразрядных сумматоров l.i и l.(i+l) и к выходу переноса одноразрядного сумматора l.i. Прямой вход порогового элемента с весом 2 подключен к выходу переноса одноразрядного сумматора 1. (i+I), Выходы пороговых элементов 2. (1, i+1) и 3,(i, i+1) всех разрядов подключены через п-входовой элемент ИЛИ 4 к выходу ошибки сумматора.

Обнаружение ошибок осуществляется на основании следующей закономерности: арифметическая сумма, составленная из операндов а, bji,, , Ь; 1-го и (i+l)-ro разрядов, входного переноса Р,, обратных кодов сумм i-ro и (i+l)-ro разрядов, инверсных значений переноса i-ro и (i + l)-ro разрядов, а также арифметическая сумма, составленная из обратных кодов операндов а, Ь;, а;,, Ь i-ro и (1+1)-го разрядов, инверсного входного переноса Р , выходов сумм 1-го и (i+t)-ro разрядов, значений переноса i-ro и (i + 1)-го разрядов должна быть равной

ьсм + SL + SL

а; + Ь;

Л

+ ч (1)

PI

+ 2Р;, 5 чs:+ S,

Р.-1 зь

Чл,

Ь,

+ 1 +

t 5

(2)

+2Р1

Р;

bj,- значения

соответствене

i-ro и (i + l)-ro разрядов входных операндов;

PI-I

-значение переноса из предыдущего (i-l)-ro разряда;

SL, s

-значения сумм i-ro

I-+1

и (1-)-1)-го разрядов;

-значения переноса i-ro

I-;, t-v-vi и (i+1) -го разрядов

-сумматора 1,1 и l,(i + U 5 При появлении неисправности на одном из выходов сумматоров l.i или l.(i-H) появляет ся ошибочный сигнал, в результате чего соотношение (1) и (2) нарушается, т.е. сумма входных, сигналов одного из пороговых элементов 2. (i, i+l) и 3.(i, i+1) превышает порог его срабатьюания, в результате чего на выходе этого порогового элемента 2. (1,1+1) и 3.(i, i+1) появляется сигнал ошибки. На фиг. 2 показана таблица состояний i-ro и (i-H)-ro разрядов сумматора, в которой приведены значения сумм входных сигналов ПЭ, срабатьтающего при появлешш ошибки на одном из выходов i-ro или (i+l)-ro разрядов сумматора. В графе Р. , aj, Ь, Ь..., указан рассматриваемый входной набор, в графе S;,, S; , PC, - соответствующий входному выходной набор, в осталь ных четырех графах - арифметическая сумма значений входных сигналов (с учетом весов) срабатьшаемого порогового элемента при появлешш ошибочного сигнала на одном из вых дов i-ro.или (i+l)-ro разряда Si, PI;, S , PaccMOT|HiM работу сумматора на входном наборе О, а; 1, Ь-|, 1, а, О, Ь. при появлении оишбочного сигнала переноса Р ,.1. При правильной работе на выходе (i+l) сумматора сигнап переноса равен 1. При появлении на этом выходе сигнала О на входы nopo-jo гового элемента 2. (i, i+1) поступает код 011011120 (с учетом весов). Сумма значений входных сигналов равна 7, что превышает порог срабатьгаания порогового элемента 2 (i, i+1) и на его выходе появляется сигнал ,, ошибки. Значения входных сигналов п|жведены в том же порядке, что и в таблице, т.е. Р, ai+T .,, Si, SL+i, Pi.vt , PI . При появлении ошибочного сигнала (О вместо 1) на выходе Р; на вход порогового эле мен-4в та 2.(1, i+1) поступает код 011011021, сумма весов равна 7 и на выходе порогового элемента 2.(1, i+1) появляется сигнал ошибки. В сумматоре обнаруживаются все ошибки, вызванные одиночными неисправностями. Кроме того, анализируя состояние выходов пороговых элементов, обнаружить неисправный разряд Оценкой сложности цифровых схем может быть цена по Квайну С .f , где Kj количество элементов i-ro типа, используемых в схеме; С; - цена элемента по Квайну, которая определяется числом входов элемента. Сложность известно о сумматора С С,о + + C..IJ,, сложность предлагаемого сумматора 250+ , , где индексы 1 и 2 отнесены соответственно к известному и предлагаемому сумматорам; йос сложность одноразрядного сумматора сложность схем контроля. 8 Очевидно, что С,о- t-ioc- Разница между сложностью известного и предлагаемого сумматоров Р Cj it R- Сложность схемы контроля известного устройства Cjj 7п f 8п 15п, так как для контроля каждого разряда требуется два ПЭ с количеством входов 7 и 8. Сложность схемы контроля предлагаемого устройстваС 9п Сравним сложность известного 1) и предлагаемого сумматоров. Если схеманеравнозначности этого .сумматора построена на двух 5-ти входовых ПЭ, то сложность схемы сумматора равна Ciyj 2п 5 Юп. Таким образом, рассматриваемый сумматор требует меньше аппаратурных затрат для построения схемы контроля по сравнению с известным. Формула изобретения Сумматор с контролем, содержащий элемент ИЛИ, п одноразрядных сумматоров, соединеных последовательно цепями переноса, п пороговых элементов с порогом на 6, причем выходы всех пороговых элементов соединены с соответствуюшими входами элемента ИЛИ, выход которого является выходом устройства. первый, второй и третий входы каждого i-ro одноразрядного сумматора соединены соответственно с шинами i-ro разряда первого, второго операнда и с выходом переноса одноразрядного сумматора (i-1)-го разряда, о т л и ч аip ш и и с я тем, что, с целью сокращения аппаратурных затрат, ишна i-ro разряда первого операнда соединена с первым входом с весом 1 1-го порогового элемента и с первым инверсным входом с весом 1 (i+1)-го порогового элемента, шина i-ro разряда второго операнда соединена со вторым входом с весом 1 i-ro порогов.ого элемента и со вторым инверсным входом с весом 1 (i+1)-го порогового элемента, шина переноса из (i -1)-го разряда соединена с третьим входом с весом 1 i-ro порюгового элемента и с третьим инверсным входом с весом 1 (i+1)-го порогового элемента, выход суммы i-ro одноразрядного сумматора соединен с первым инверсным входом с весом 1 i-ro порогового элемента и с первым входом с весом 1 (i + l)-ro порогового элемента, выход переноса i-ro одноразрядного сумматора соединен со вторым инверсным входом с весом 1 i-ro порогового элемента и со вторым входом с весом 1 (i+1)-го порогового элемента, шина (i+l)-ro разряда первого операнда

7788108

соединена с четвертым входом с весхэм 1 i-ro порогового элемента и четвертым инверсным входом с весом 1 {i+l)-ro порогового элемента, шина (i-H)-ro разряда второго операнда соединена с пятым, входом с весом 1 i-ro j порогового элемента н с пятым инверсным входом с весом 1 (i+l).ro порогового элемента, выход суммы (i+l)-ro одноразрядного сумматора соединен с третьим инверсным входом с весом 1 i-ro порогового элемента и с треть- ю им входом с весом 1 .(i+1)-го порогового элемента, выход переноса (i+1)-го одноразрядного сумматора соединен с четвертым инверсным входом с весом 2 i-ro порогового элемента и четвертым входом с весом 2 (i+1)-го порогового элемента.

Источники информации, принятые во внимание при экспертизе . 1. Авторское свидетельство СССР № 365708. кл. G 06 F 11/02,

2. Авторское свидетельство СССР № 500527, кл. G 06 F 11/00 (прототап).

| название | год | авторы | номер документа |

|---|---|---|---|

| Контролируемый сумматор | 1978 |

|

SU811261A1 |

| Устройство для вычисления произведения векторов (его варианты) | 1984 |

|

SU1280389A1 |

| Устройство для вычисления сумм произведений | 1984 |

|

SU1166101A1 |

| Устройство для деления чисел | 1981 |

|

SU970356A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU938282A1 |

| Комбинационный сумматор | 1986 |

|

SU1327092A1 |

| Вычитающее устройство с контролем | 1978 |

|

SU807274A1 |

| Матричный вычислитель | 1983 |

|

SU1137464A1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Обратимый п-разрядный сумматор | 1979 |

|

SU824204A1 |

от flOffof (, ) - 7, }

и

Pi4

Qi+f

SL+I

Авторы

Даты

1980-12-15—Публикация

1979-01-02—Подача