1

Сумматор может быть исиользован в вычислительных, управляющих и информационно-логических устройствах, в частности в арифметических устройствах различного .назначения.

Известны сумматоры в системе остаточных классов, содержащие два входных регистра и оиерационную схему, выиолненную на ферритовых сердечниках. Такие сумматоры сложны и имеют больиюе количество элементов.

Цель изобретения заключается в унрощении су.мматора, уменьшении количества элементов, необходимых для ностроення схем, а также в иовышении его надежности в работе. Это достигается введением в сумматор схемы «ИЛИ, причем каждая выходная шина одного регистра через схему «ИЛИ .и соответствующую обмотку ферритового сердечника операционной схемы соединена с каждой выходной шиной другого регист;ра.

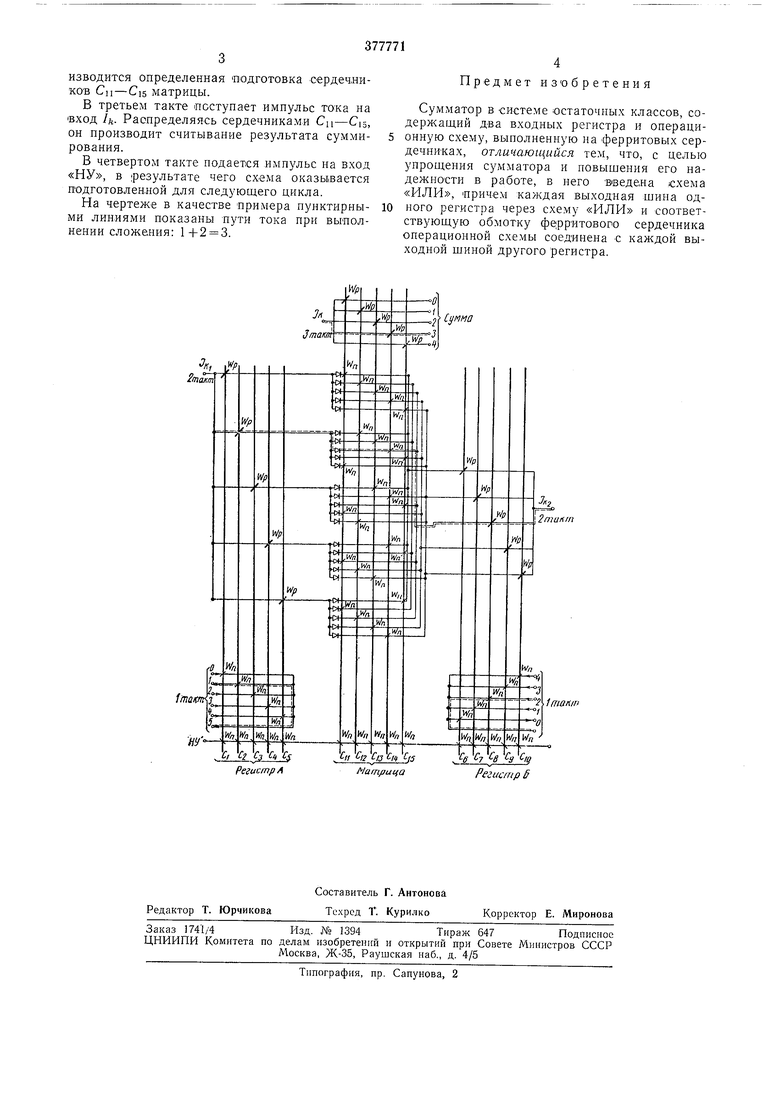

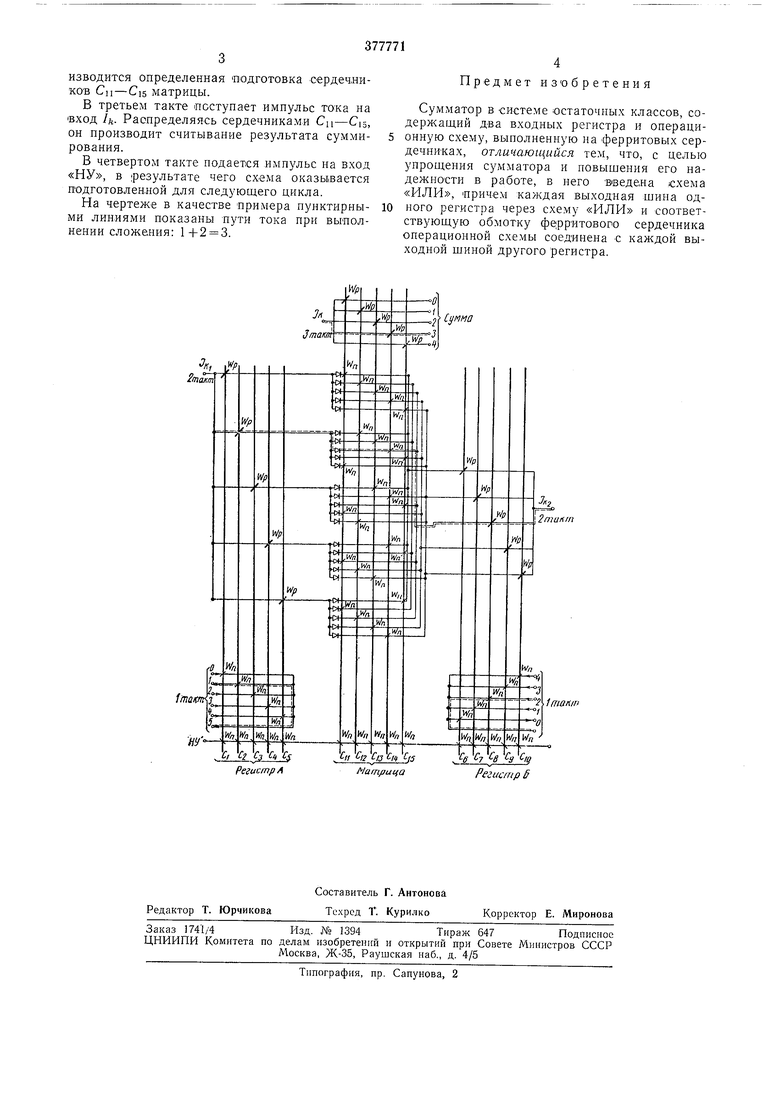

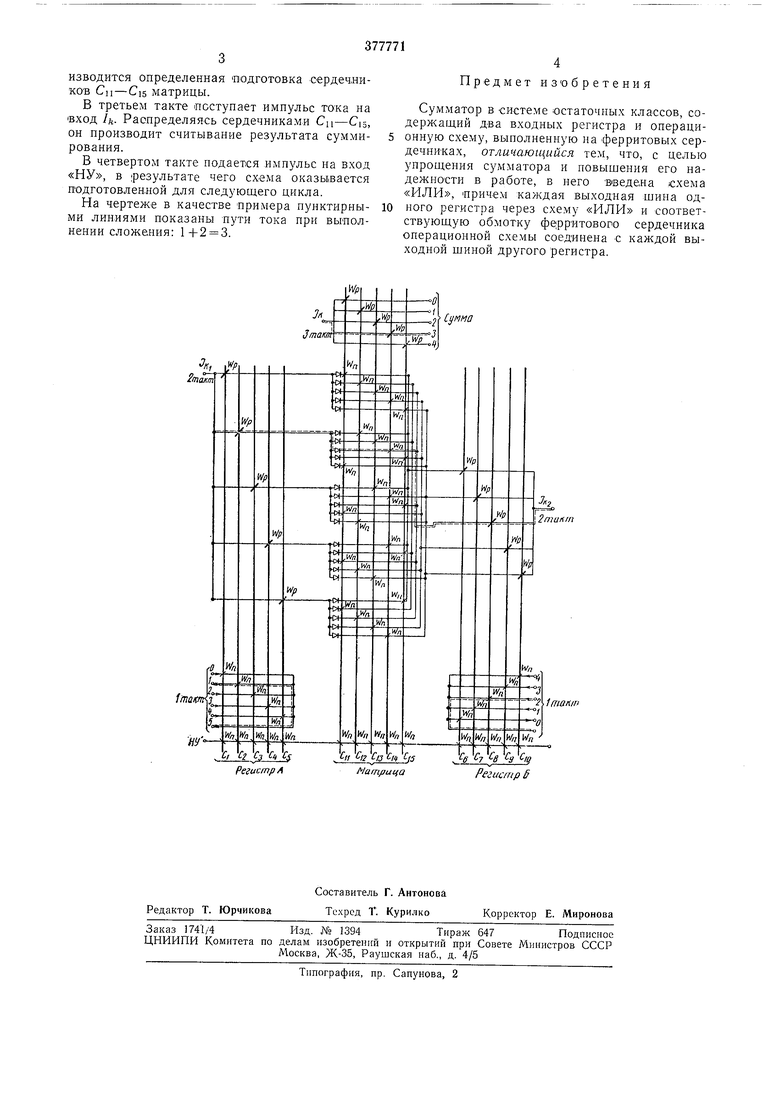

На чертеже иоказаиа схема сумматора в системе остаточных классов но модулю нять.

Матричная схема, выполненная на сердечниках Ci-€5 с обмотками Wn подготовки и расиределяющими обмотками Wp, является одним входным регистром А. Схема, вынолненная на сердечниках Се-Сщ, является другим входным регистром Б. На входных регистрах

2

могут быть нредставлены остатки чисел (О, 1, 2, 3, 4) по модулю нять.

Оиерационная матричная схема выполнена на ферритоБых сердечниках Си - Cis с обмотками Wn подготовки и раснределяюи1,нми обмотками Wp. Схема «ИЛИ выполнена на днодах.

Начальная установка элементов схемы производится но щине «НУ Путем аюдачи имиульса тока в обмотки подготовки. Нри этом все сердечники подготовлены «вниз и -распределяюихие обмотки имеют большое индуктивное сопротивление для токов //, , / и 1/.. В первом такте в регистры /1 и Б вводится

информация о величннах слагаемых остатков путем подачи импульсов на один из входов 0(А)-4(А) и на один из входов 0(Б)-4(Б). Сердечники, в обмотки подготовки которых поступают имнульсы, иереводятся в положение

«вверх, иоэтому индуктивное сопротивленне расиределяющих обмоток этих сердечи 1ков имеет малую величину.

Во втором такте подается импульс тока на входы //( и /д,. Он раснределяется сердечннками Ci-Cs и Сб-Сю и проходит одним из 25 нутей в соответствнн с сочетанием слагаемых. Нри прохождении импульса тока производится определенная подготовка сердечников Си - Ci5 матрицы.

В третьем такте поступает импульс тока на ВХОД /А. Распределяясь сердечниками Сц-Cis, он производит считывание результата суммирования.

В четвертом такте подается импульс на вход «НУ, в результате чего схема оказывается подготовленной для следуюпаего цикла.

На чертеже в качестве примера пунктирными линиями показаны пути тока при выполнении сложения: 1+2 3.

Нредмет изобретения

Сумматор в системе остаточных классов, содерл-сащий два входных регистра и операционную схему, выполненную на феррнтовых сердечниках, отличающийся тем, что, с целью упрощения сумматора и повышения его надежности в работе, в него введена :Схема «ИЛИ, причем каждая выходная шина одного регистра через схему «ИЛИ и соответствуюшую обмотку ферритовооо сердечника операционной схемы соединена с каждой выходной шиной другого регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор по модулю | 1979 |

|

SU855659A1 |

| ВСЕСОЮЗН/лЯ I ПАТЕНТКО-ИКьл-- HA": | 1973 |

|

SU374595A1 |

| ПАТЕНТНО-ТЕХНННЕСКАЯ]БИБЛИОТЕКА | 1971 |

|

SU304704A1 |

| Двоичный параллельный сумматор со сквозным переносом | 1960 |

|

SU142818A1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР | 1967 |

|

SU197281A1 |

| Устройство для выравнивания порядков чисел,представленных в системе остаточных классов | 1973 |

|

SU781812A1 |

| НАКАПЛИВАЮЩИЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1966 |

|

SU224164A1 |

| Преобразователь магнитных полей к дефектоскопу | 1983 |

|

SU1191812A1 |

| Параллельный матричный сумматор- вычитатель | 1977 |

|

SU737950A1 |

| ФЕРРИТОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1968 |

|

SU208347A1 |

Авторы

Даты

1973-01-01—Публикация