1

Изобретение отрюеится к вычислительной технике и предназначено для преобразования десятичных кодов в коды системы остаточных классов (СОК).

Известно устройство для преобразования кодов из любой позиционной системы счисления (Б том числе из десятичной) в коды СОК, содержащее входные регистры, блоки суммирования, блоки двоичного кодирования и дешифраторы.

Предлагаемое устройство отличается от известного тем, что в нем разрядные преобразователи выполнены на цифровых элементах распределения тока с числом сердечников, равным значению соответствующего модуля системы, обмотки записи каждого сердечника соединены с соответствующими выходами соответствующего входного регистра, а обмотки считывания соединены со входами арифметического устройства по соответствующему модулю.

Это позволяет упростить схему устройства и повысить его надежность.

Устройство использует следующий принцип работы.

Любое (k + ) -разрядное десятичное число может быть представлено в форме Х А,-10 + + ... + ЛЛО+Ло10«

:: AftCft + Aii iCk-l -)-.+ jCj -|- ЛоСо,

где о Лг 9, о / /fe, Сг 10 (mod Pj).

Тогда для получения значения X в СОК необходимо иметь значения Лг и С.

Разряды числа X в СОК образуются путем суммирования значений Л; и Cj по

k модулю, т. е. ccj S (Лг Cj) -mod Pj.

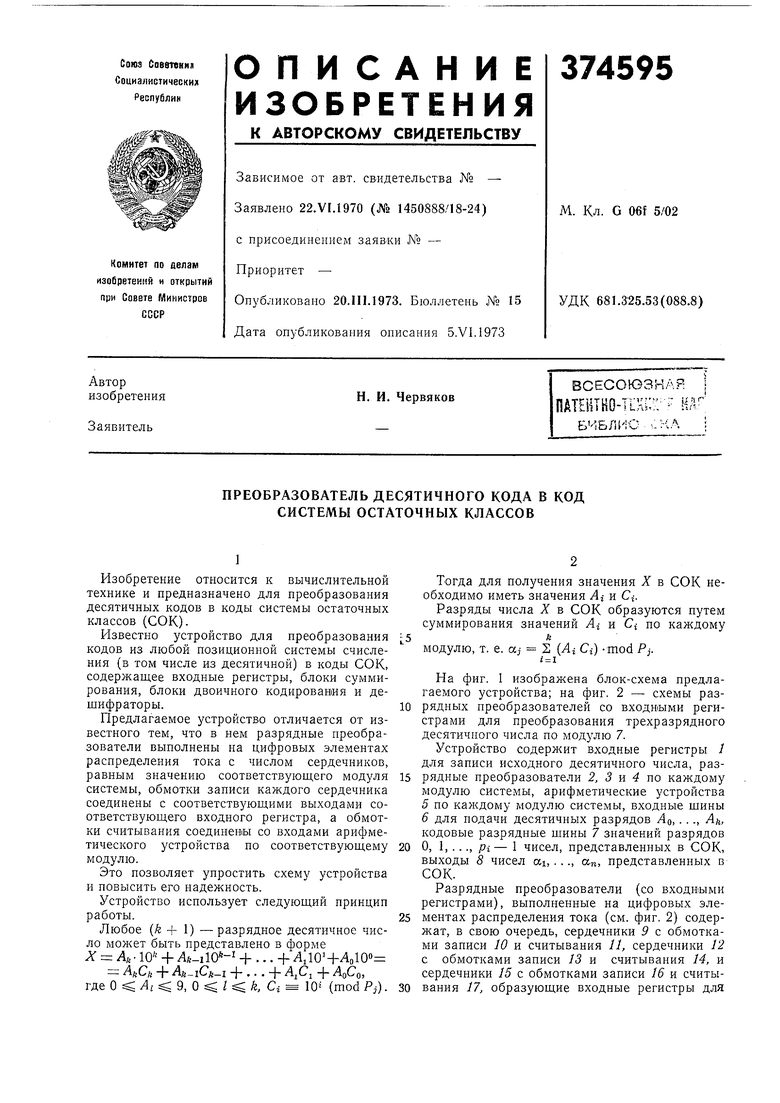

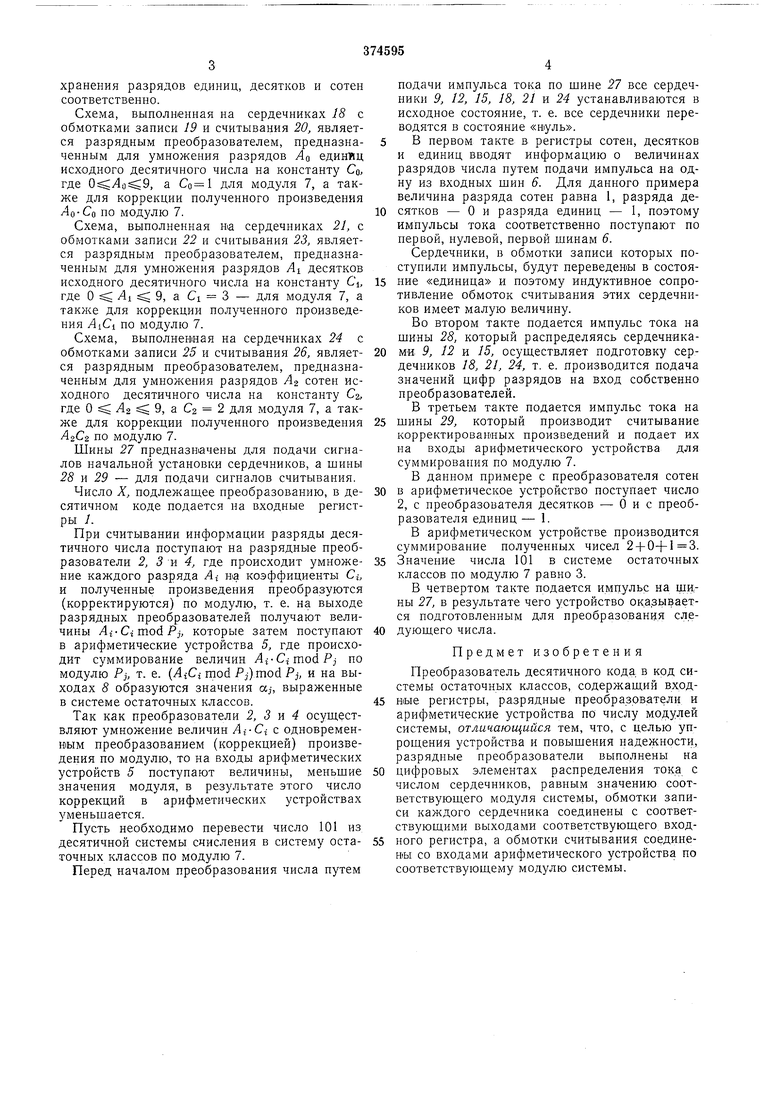

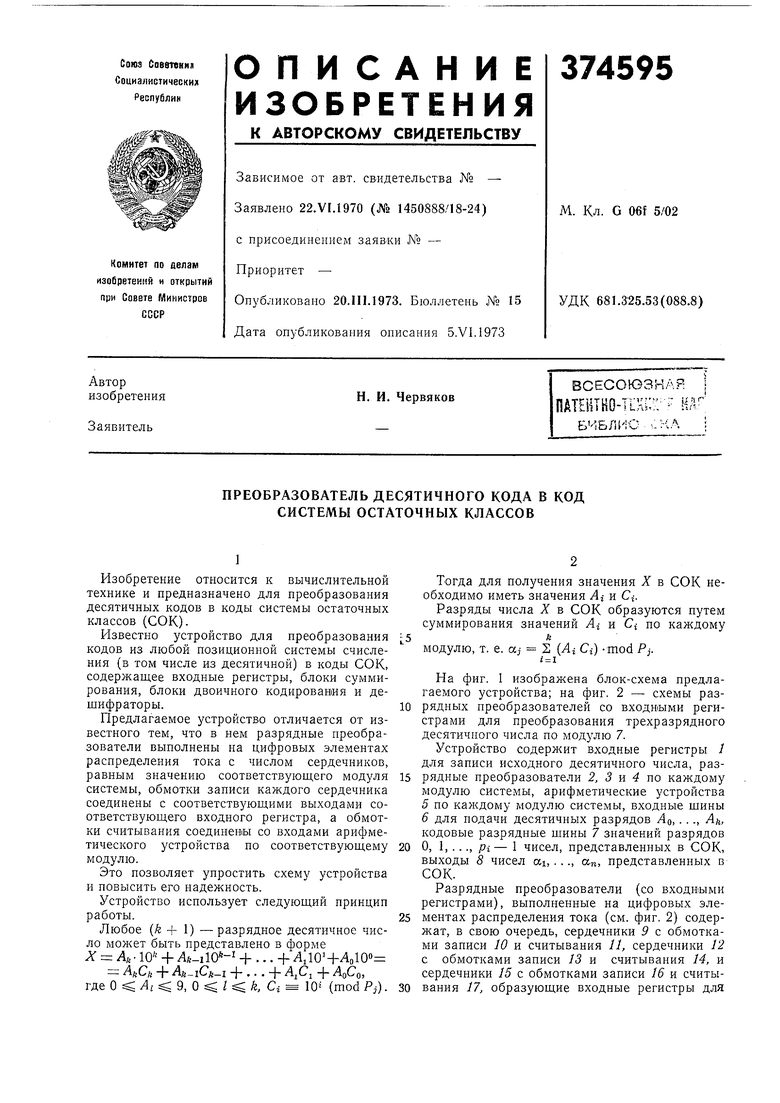

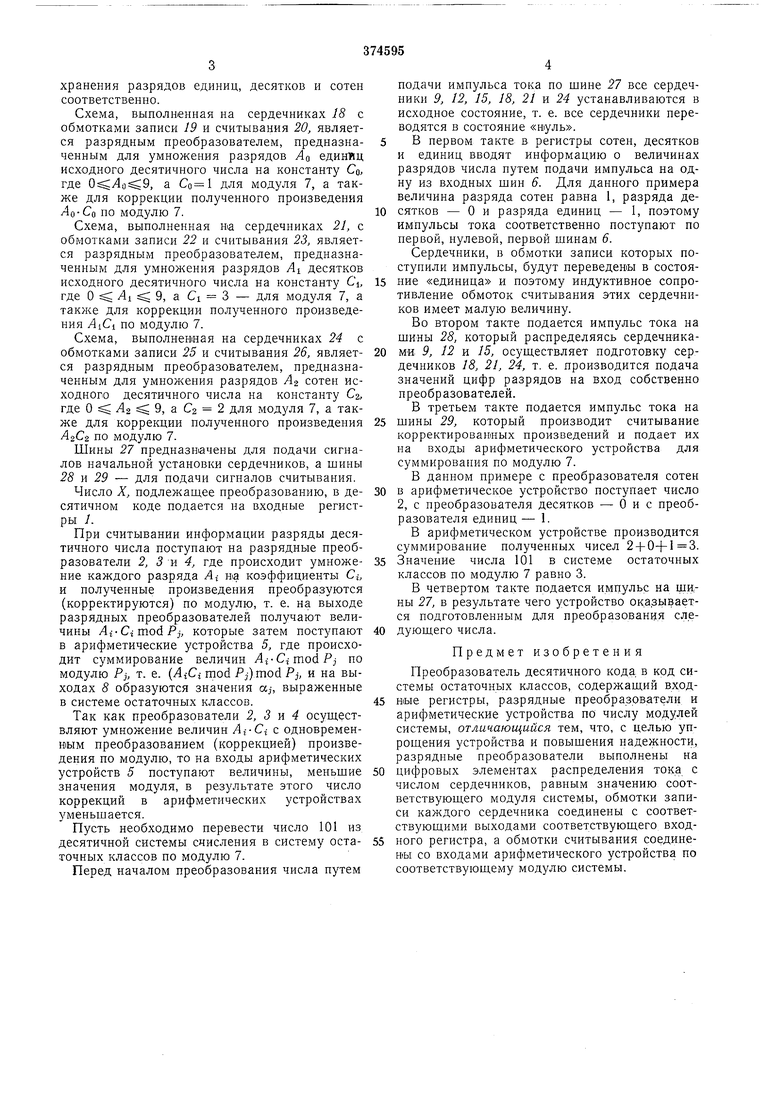

На фиг. 1 изображена блок-схема предлагаемого устройства; на фиг. 2 - схемы разрядных преобразователей со входными регистрами для преобразования трехразрядного десятичного числа по модулю 7.

Устройство содержит входные регистры 1 для записи исходного десятичного числа, разрядные преобразователи 2, 3 к 4 ио каждому модулю системы, арифметические устройства

5по каждому модулю системы, входные шины

6для подачи десятичных разрядов Л о, . . ., Ли, кодовые разрядные шины 7 значений разрядов О, I, ..., рг - 1 чисел, представленных в СОК, выходы 8 чисел аь . .., «„, представленных в СОК.

Разрядные преобразователи (со входными регистрами), выполненные на цифровых элементах распределения тока (см. фиг. 2) содержат, в свою очередь, сердечники 9 с обмотками записи 10 и считывания //, сердечники 12 с обмотками записи 13 и считывания 14, и сердечники 15 с обмотками записи 16 и считывания 17, образующие входные регистры для

хранения разрядов единиц, десятков и сотен соответственно.

Схема, выполненная на сердечниках 18 с обмотками записи 19 и считывания 20, является разрядным преобразователем, предназначенным для умножения разрядов AQ единиц исходного десятичного числа на константу Со, где , а для модуля 7, а также для коррекции полученного произведения

AQ-CQ по модулю 7.

Схема, выполненная на сердечниках 21, с обмотками записи 22 и считывания 23, является разрядным преобразователем, предназначенным для умножения разрядов AI десятков исходного десятичного числа на константу Ci, где О Л1 9, а Ci 3 - для модуля 7, а также для коррекции полученного произведения AiCi по модулю 7.

Схема, выполненная на сердечниках 24 с обмотками записи 25 и считывания 26, является разрядным преобразователем, предназначенным для умножения разрядов Ла сотен исходного десятичного числа на константу Cz, где О Л2 9, а Сз 2 для модуля 7, а также для коррекции полученного произведения ЛоСг по модулю 7.

Шины 27 предназначены для подачи сигналов начальной установки сердечников, а шины 28 Е 29 - для подачи сигналов считывания.

Число X, подлежащее преобразованию, в десятичном коде подается на входные регистры /.

При считывании информации разряды десятичного числа поступают на разрядные преобразователи 2, 3 и 4, где происходит умножение каждого разряда Л г па коэффициенты Сг, и полученные произведения преобразуются (корректируются) по модулю, т. е. на выходе разрядных преобразователей получают величины Лг-СгШодР,, которые затем поступают в арифметические устройства 5, где происходит суммирование величин Ai-CimodPj по модулю PJ, т. е. (AiCi mod f j) mod Pj, и на выходах 5 образуются значения а,-, выраженные в системе остаточных классов.

Так как преобразователи 2, 3 и 4 осуществляют умножение величин AfCi с одновременным преобразованием (коррекцией) произведения по модулю, то на входы арифметических устройств 5 поступают величины, меньщие значения модуля, в результате этого число коррекций в арифметических устройствах уменьшается.

Пусть необходимо перевести число 101 из десятичной системы счисления в систему остаточных классов по модулю 7.

Перед началом преобразования числа путем

подачи импульса тока по шине 27 все сердечники 9, 12, 15, 18, 21 и 24 устанавливаются в исходное состояние, т. е. все сердечники переводятся в состояние «нуль.

В первом такте в регистры сотен, десятков и единиц вводят информацию о величинах разрядов числа путем подачи импульса на одну из входных шин 6. Для данного примера величина разряда сотен равна 1, разряда десятков - О и разряда единиц - 1, поэтому импульсы тока соответственно поступают по первой, нулевой, первой шинам 6.

Сердечники, в обмотки записи которых поступили импульсы, будут переведены в состояние «единица и поэтому индуктивное сопротивление обмоток считывания этих сердечников имеет малую величину.

Во втором такте подается импульс тока на шины 28, который распределяясь сердечниками 9, 12 и 15, осуществляет подготовку сердечников 18, 21, 24, т. е. производится подача значений цифр разрядов на вход собственно преобразователей. В третьем такте подается импульс тока на

шины 29, который производит считывание

корректированных произведений и подает их

на входы арифметического устройства для

суммирования по модулю 7.

В данном примере с преобразователя сотен

в арифметическое устройство поступает число 2, с преобразователя десятков - бис преобразователя единиц - 1.

В арифметическом устройстве производится суммирование полученных чисел 2 + .

Значение числа 101 в системе остаточных классов по модулю 7 равно 3.

В четвертом такте подается имцульс на щины 27, в результате чего устройство оказывается подготовленным для преобразования следующего числа.

Предмет изобретения

Преобразователь десятичного кода, в код системы остаточных классов, содержащий входHibie регистры, разрядные преобразователи и арифметические устройства по числу модулей системы, отличающийся тем, что, с целью упрощения устройства и повышения надежности, разрядные преобразователи выполнены на

цифровых элементах распределения тока с числом сердечников, равным значению соответствующего модуля системы, обмотки записи каждого сердечника соединены с соответствующими выходами соответствующего входного регистра, а обмотки считывания соединены со входами арифметического устройства по соответствующему модулю системы. Регистр единиц PcZJ€inp двсс.-:::зЗ Регистр сотен { it-Jr-Y-l- - -v- -

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в код системы остаточных классов | 1981 |

|

SU1001079A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1981 |

|

SU983701A1 |

| Побайтный преобразователь из двоичного в двоично-кодированное остаточное представление | 1972 |

|

SU437067A1 |

| Устройство для преобразования чисел из порционной системы счисления в систему остаточных классов | 1981 |

|

SU1008729A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386444A1 |

| АССОЦИАТИВНО-АДРЕСНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU336697A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДОВ ИЗ ОСТАТОЧНОЙ СИСТЕМЫ СЧИСЛЕНИЯ В ПОЛИАДИЧЕСКУЮ | 1973 |

|

SU407301A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1973 |

|

SU368605A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ЧИСЕЛ | 1973 |

|

SU377767A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1969 |

|

SU255993A1 |

Авторы

Даты

1973-01-01—Публикация