il

Изобретение относится к области запоминающих устройств.

Известно запоминающее устройство (ЗУ), содержащее поразрядно соединенные регистры, схемы управлени-я перезаписью по числу регистров, выход каждой из которых подключен ко входу маркерного разряда соответствующего регистра, ади.н вход каждой схемы, кроме двух последних, подсоединен к первому выходу маркерного р азряда последующего регистра, а другой вход каждой схемы, кроме первой, - ко второму выходу маркерного разряда соответствующего регистра.

Однако лри использаван1Ии известного запоминающего устройства в адаптивных системах телеизмерения оно не позволяет проводить в процессе залиси и передачи информации сжатие «пустых слов, т. е. слов, не содержащих приращений параметров контролируемых объектов.

Предлагаемое запоминающее устройство отличается от известного тем, что оно содержит коммутатор, входы которого подключены ко входным щина,м устройства, а выходы - к разрядным входам входного регистра, дополиительные маркерные разряды в каждом регистре, соедиленные между собой последовательно, переключатель, информационный вход которого соединен с выходом считывания маркерного разряда выходного регистра,

выходы - со входами считывания информационных разрядов и дополнительного ма.ркерного разряда выходного регистра, а управ.ляющий вход подключен к выходу дополнительно введенной в устройство схемы «ИЛИ, входы которой соединены с выходами информационных разрядов предвыходного регистра, выход дополнительного маркерного разряда входного регистра подключен ко второму входу первой схемы, управления перезаписью, а выход дополнительного маркерного разряда выходного регистра - к первому входу пред последней схемы управления перезаписью,, в результате чего значительно ра,сщиря,ется область применения запоминающего устройства, т. е. эффективное использование его в адаптивных системах телеизмерения.

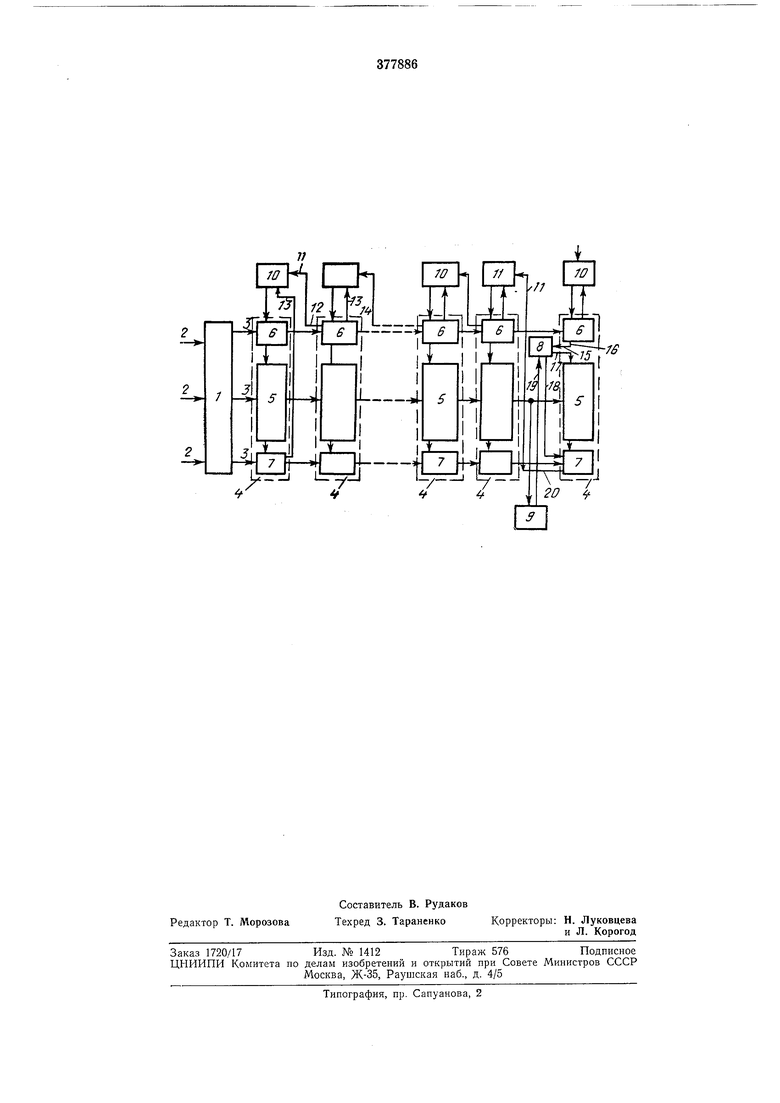

На чертеже дана блок-схема предлагаемого запоминающего устройства,.

Предлагаемое устройство содержит коммутатор /, входы которого подключены к входным щинам 2 устройства, а выходы - к разрядным входам 3 входного регистра 4 (на чертеже левый регистр). Входной и другие регистры 4 содержат информационные разря,ды 5, основные и дополнительные маркерные разряды 6 п 7 соответственно.

Все регистры соединены поразрядно последовательно.

Устройство также содержит переключатель 8, схему «ИЛИ 9 и схемы 10 управления перезаписью, количество последних равно числу регистров 4 ЗУ. Выход каждой схемы 10 подключен ко входу маркерного разряда соответствующего регистра 4. Один вход // схемы JO, кроме двук последних (правые на чертеже), подсоединен к первому выходу 12 маркерного разряда 6 последующего регистра 4, а другой вход 13 каждой схемы 10, кроме первой,-ко BTOipOMy выходу 14 маркерного разряда 6 соответствующего регистра 4. Информационный вход 15 переключателя 8 соединен с выходом считывания 16 маркерного разряда 6 выходного регистра 4, выходы 17 и 18 - с входами считывания информациовных разрядов 5 и дополнительного маркерного разряда 7 выходного регистра 4, а управляющий вход 19 подключен к выходу схемы «ИЛИ 9, входы которой соединены с выходами информационных разрядов 5 .предвыходного регистра 4. Выход 20 дополнительного маркерного разряда 7 входного регистра 4 подключен ко второму входу 13 первой схемы 10, а выход 20 дополвительно-го маркерного разряда 7 выходного регистра 4 - к первому входу // предпоследней схемы 10.

Устройство работа.ет следующим образом.

Коммутатор 1 .последовательно вводит в запоминающее устройство кодовый адрес кадра-, кодовую посылку времени, кодовые посылки приращений, распределяя последние в соответствии с программой формирования слов ПО разрядам регистра, и при необходимости, вторую кодовую лосылку времени, а также маркерные импульсы начала и окончания слова.

По о.кончан1ии заполнения входного регистра 4 с маркерного разряда 7 этого регистра на первую схему 10 управления перезаписью поступает сигнал готовности к перезаписи; при наличии свободных последующих регистров 4 происходит автоматическое .продвижение слова к выходу запоминающего устройства.

При перезаписи СЛОЪА из предвыходного регистра в выходной регистр сигналы информационных разрядов поступают также на входы схемы «ИЛИ 9. При наличии в разряда.х 5 хотя бы одной единицы схема «ИЛИ 9 формирует сигнал, переводящий переключатель 8 в положение, при котором импульсы считывания выходного регистра 4 последовательно опрашивают все его разряды. С выходного регистра снимается полное слово.

В случае, -если слово оказалось «пустым (в информационных разрядах 5 нет ни одной единицы) переключатель 8 остается е положении, при котором импульс считывания сразу -поступает в дополнительный маркерный

разряд 7. С выходного регистра 4 снимается сжатое слово (маркер начала слова и следующий непосредственно за ним маркер оконча.ния слова).

Предмет изобретения

Запоминающее устройство, содержащее поразрядно соединенные регистры, схемы управления перезаписью по числу регистров, выход каждой из которых подключен ко входу маркерного разряда соответствующего регистра, ОДИН вход каждой схемы, кроме двух последних, подсоединен к первому выходу маркерного ра-зряда последующего регистра, а другой вход каждой схемы, кроме первой,- ко второму выходу маркерного разряда соответствующего регистра, отличающееся тем, что, с целью расширения, области применения, оно

содержит коммутатор, входы, которого подключены К входным шинам устройства, а выходы- к разрядным входам входно.го регистра, дополнительные маркерные разряды в каждом регистре, соединенные между собой

последовательно, переклю1чатель, информационный вход которого соединен с выходом считывания маркерного разряда выходного регистра, выходы - со входами считывания ин формационных разрядов и дополнительного

маркерного разряда выходного регистра, а управляющий вход подключен к выходу дополнительно введенной в устройство схемы «ИЛИ, входы которой соединены с выходами информационных разрядов предвыходнюго

регистра, выход дополнительного маркерного разряда входного регистра подключен ко второму входу первой схемы управления перезаписью, а выход дополнительного маркерного разряда выходного регистра - к первому

входу предпоследней схемы управления перезаписью.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU397972A1 |

| Буферное запоминающее устройство | 1978 |

|

SU748509A1 |

| ВСЕСОЮЗНАЯ пм?нтно^.:^--' Щ | 1973 |

|

SU375681A1 |

| Буферное запоминающее устройствоС АВТОНОМНыМ КОНТРОлЕМ | 1979 |

|

SU842973A1 |

| Буферное запоминающее устройство | 1974 |

|

SU487422A2 |

| Буферное запоминающее устройство | 1980 |

|

SU858109A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU427389A1 |

| Декодер кодов Рида-Соломона | 1988 |

|

SU1690202A1 |

| Запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1381605A1 |

| ПЕРЕКЛЮЧАТЕЛЬ КАНАЛОВ | 1973 |

|

SU373868A1 |

Авторы

Даты

1973-01-01—Публикация