со

00 О5

Изобретение относится к вычислительной технике и может быть использовано при создании высоконадежных запоминакяцих и вычислительных систем.

Целью изобретения - упрощение устройства и повышение достоверности контроля.

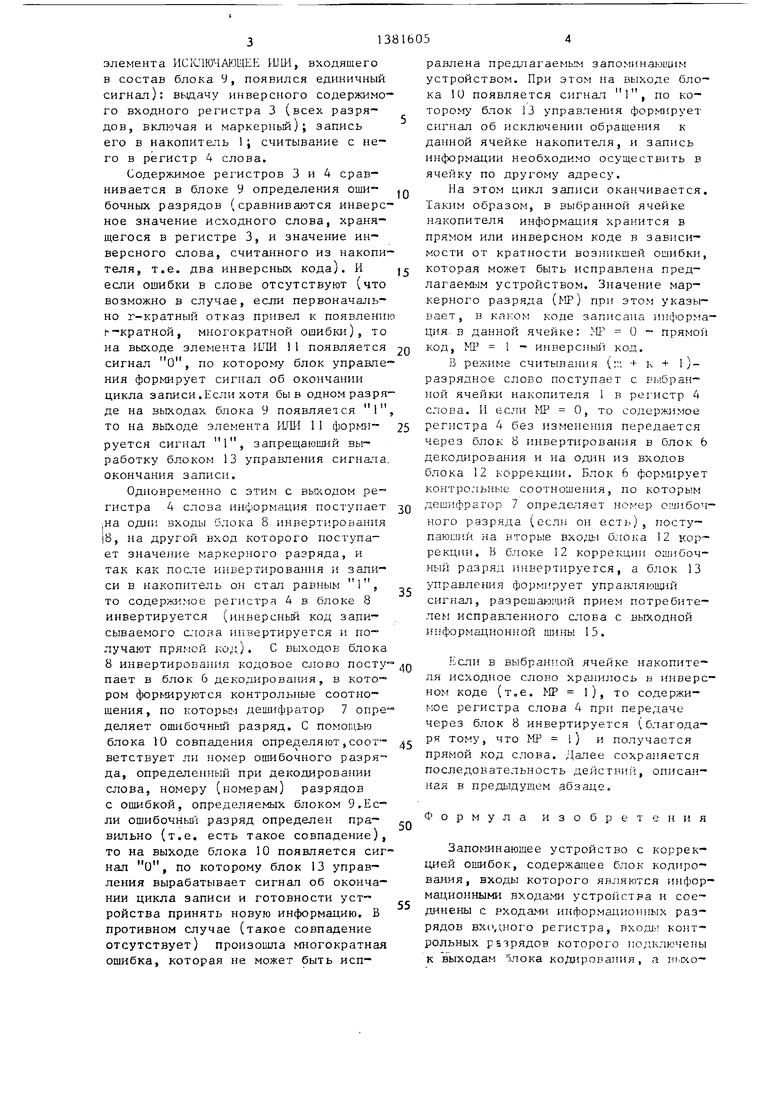

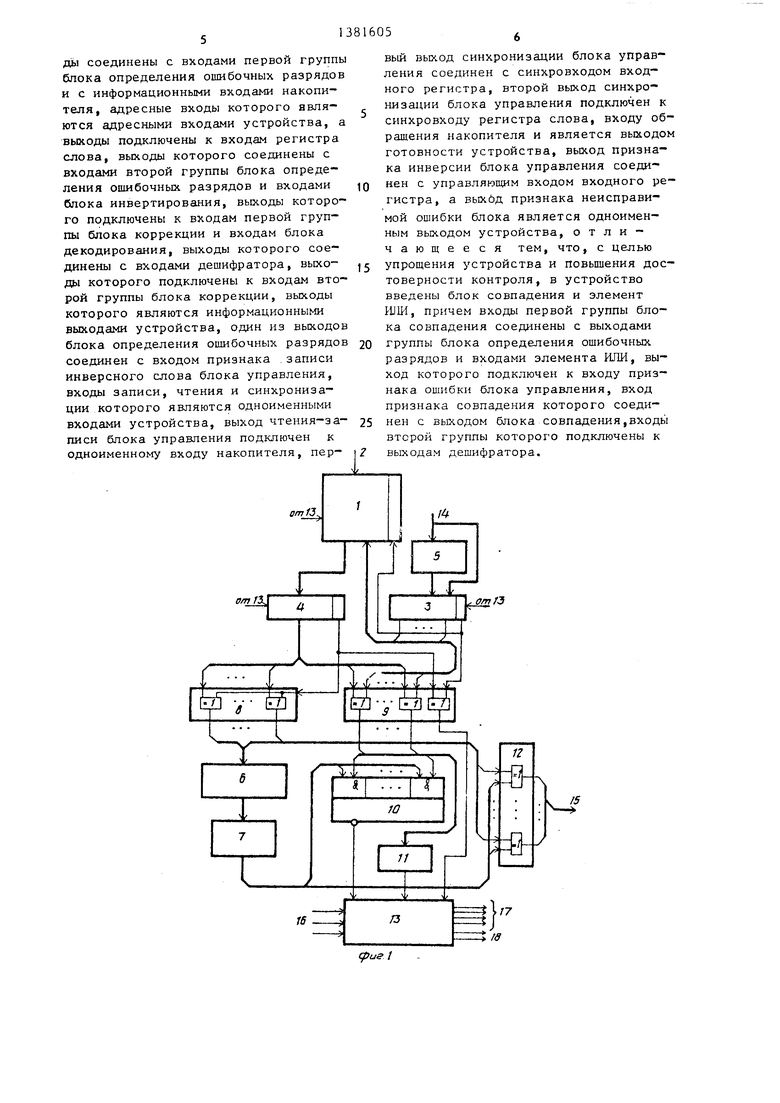

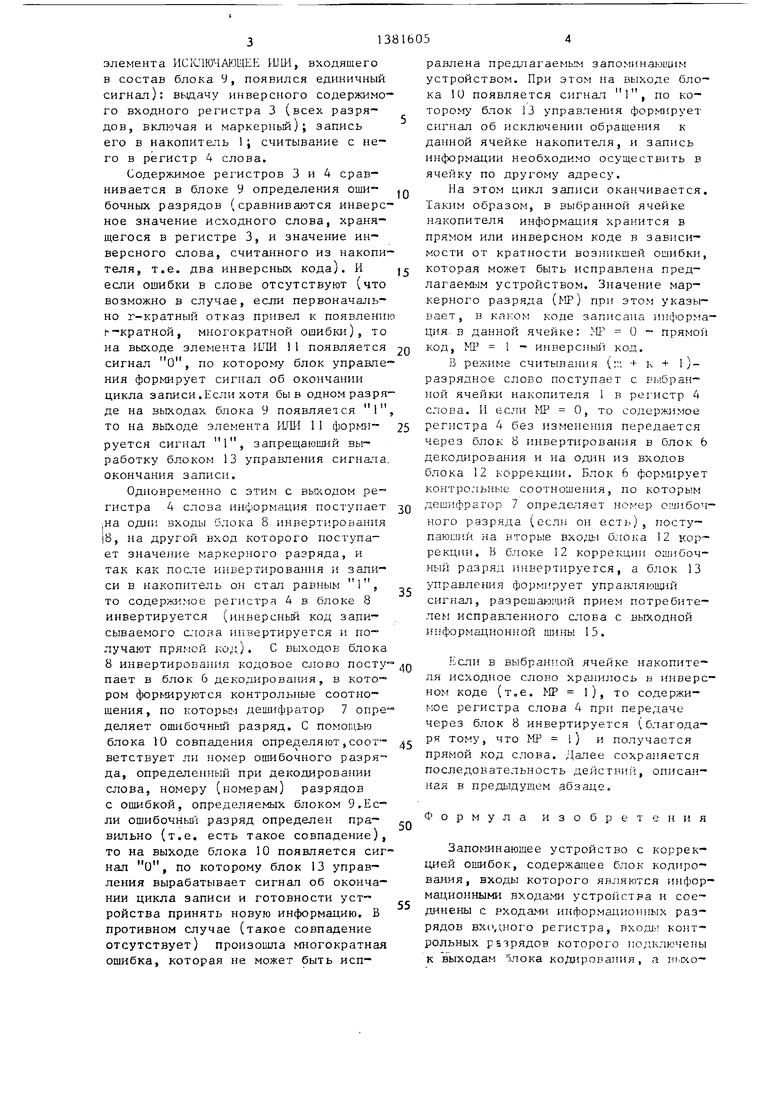

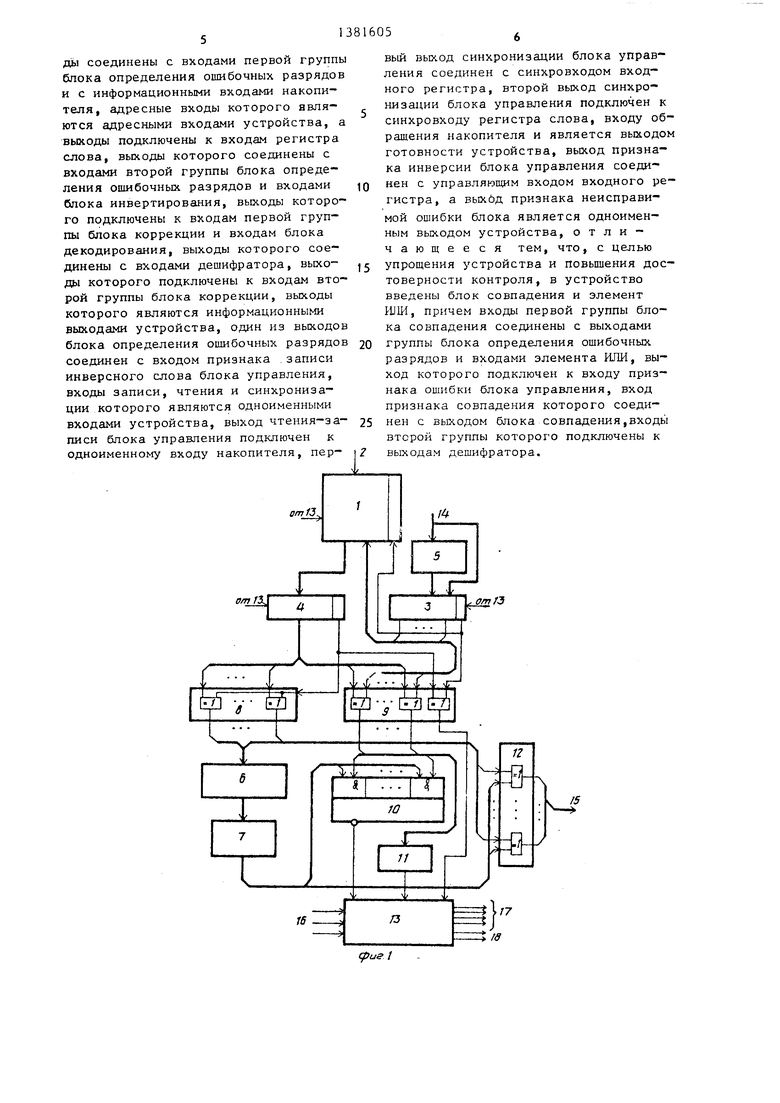

На фиг.I приведена структурная схема запоминающего устройства с кор- рекцией ошибок; на фиг.2 - пример схемы блока управления.

Запоминающее устройство с коррекцией ошибок содержит накопитель 1 с адресными входами 2, входной регистр 3 и регистр 4 слова, блоки 5 кодирования и декодирования 6, дешифратор 7, блок 8 инвертирования, блок 9 определения ошибочных разрядов, блок 10 совпадения, элемент ИЛИ 11, блок 12 коррекции, блок 13 управления, а также информационные входы 14 и выходы 15, управляющие входы записи, чтения и синхронизации 16. На фиг.1 также обозначены выходы 17, 18 блока 13 управления.

Входной регистр 3 выполнен на TD- триггерах, причем Т-входы всех триггеров объединены и образуют управляю щий вход инвертирования содержимого регистра.

Блок 13 управления содержит D- триггеры 19 и 20, элементы И 21 - 24 элемент ИЛИ 25 и элемент ИЛИ-НЕ 26.

Запоминающее устройство с коррек- цией ошибок работает следующим образом.

При записи т-разрядное информационное слово поступает по входу 14 в блок 5 кодирования, в котором коди- руется в соответствии с кодом, исп- равляюшд1м одну ошибку, например кодом Хэмминга. К полученному кодовому слову добавляется также один маркерный разряд, который первоначально устанавливается в состояние О.Зате полученное таким образом кодовое слово передается во входной регистр 3, с выходов которого записывается в выбранную ячейку накопителя 1 (адрес ячейки поступает па шине 2). Запоми- наюи;ие ячейки накопителя 1 имеют разрядность (ш + к + 1), где к - количество контрольных разрядов, формируемых блоком кодирования, и один разряд - маркерный.

Для контроля правильности хранящейся в накопителе 1 информации (т + + к + 1)-разрядное слово считывается

на регистр слова 4. Содержимое регистров 3 и 4 поступает на входы блока

9определения ошибочных разрядов, представляющего собой группу элементов ИСК:1ЮЧА1аДЕЕ ШШ. в блоке 9 коды поразрядно сравниваются. На выходах блока 9 в тех же разрядах, которые

не совпадают, появляются 1. Это свидетельствует о том, что в этих разрядах возникла ошибка. В случае, если ошибки в слове нет, т.е. выходы схемы 9 - в нулевом состоянии, на выходе элемента ИЛИ 11 формируется О, поступающий в блок 13 управления. По этому сигналу вырабатывается сигнал, свидетельствующий об окончании цикла записи. В случае, если хотя бы в одном разряде на выходах блока 9 появится 1, на выходе элемента ИЛИ 11 вырабатывается 1.

Одновременно с этим содержимое регистра слова 4 без изменений (так как маркерный разряд - О) передается через блок 8 инвертирования и поступает в блок 6 декодирования, в котором формируются контрольные соотношения, по которым дешифратор 7 устанавливает ошибочньй разряд. Информация с выходов дешифратора и блока определения ошибочного разряда поступает в блок 10 совпадения, который определяет, соответствует ли ошибочный разряд, определенньм при декодировании слова, номеру (или номерам) разрядов с ошибкой, определенных блоком 9. Если такое совпадение существует (т.е. ошибочный разряд определен правильно), на выходе блока 10 формируется сигнал О, по которому блок 13 управления вырабатывает сигнал об окончании цикла записи и готовности устройства принять следующее слово. В противном случае (такое совпадение отсутствует, что возможно при возникновении многократной ошибки, которая, однако,идентифицируется, либо при неправильном функционировании блока декодирования 6 или дешифратора 7) на выходе блока

10формируется сигнал 1, по которому блок I3 управления вырабатывает сигналы для выполнения следующей последовательности действий (необходимо отметить, что сигналы для выполнения этих же действий блок управления формирует н в случае, если произошла ошибка в маркерном разряде ячейки, т.е. на вькоде последнего

элемента ИС ШЮЧАКЛДЕЕ ШШ, входящего в состав блока 9, появился единичный сигнал): выдачу инверсного содержимого входного регистра 3 (всех разрядов, включая и маркерный); запись его в накопитель 1; считывание с него в регистр 4 слова.

Содержимое регистров 3 и 4 сравнивается в блоке 9 определения оши- бочных разрядов (сравниваются инверсное значение исходного слова, хранящегося в регистре 3, и значение инверсного слова, считанного из накопителя, т.е. два инверсных кода). И если ошибки в слове отсутствуют (что возможно в случае, если первоначально г-кратный отказ привел к появлению г-кратной, многократной ошибки), то на выходе элемента 1ШИ 11 появляется сигнал О, по которому блок управления формирует сигнал об окончании цикла записи .Если хотя быв одном разряде на выходах блока 9 появляется 1 то на выходе элемента ШШ 1 1 формя-

руется сигнал

Г

запрещающий выработку блоком 13 управле}шя сигнала, окончания записи.

Одновременно с этим с выходом регистра 4 слова информация поступает |На одни входы блока 8 инвертирования IB, на другой вход которого поступает значение маркерного разряда, и так как после инвертирования и записи в накопитель он стал равным 1, то содержимое реги.стра 4 в блоке 8 инвертируется (инверсньй код записываемого слова инвертируется и получают прямой код.). С выходов блока 8 инвертирования кодовое слово посту™ пает в блок 6 декодирования, в котором формируются контрольные соотношения, по которьм дешифратор 7 определяет ошибочный разряд. С помощью блока 10 совпадения определяют,соответствует ли номер ошибочного разряда, определенный при декодировании слова, номеру (номерам) разрядов с ошибкой, определяемых блоком 9.Если ошибочньп разряд определен правильно (т.е. есть такое совпадение), то на выходе блока 10 появляется сигнал о, по которому блок 13 управления вырабатывает сигнал об окончании цикла записи и готовности уст ройства принять новую информацию. В противном случае (такое совпадение отсутствует) произошла многократная ошибка, которая не может быть исп-

0 5

0

5

0

5

0

5

равлена предлагаемым запомянаьэ1 у1м устройством. При этом на выходе блока 10 появляется сигнал 1, по которому блок 13 управления фор п{рует сигнал об исключении обращения к данной ячейке накопителя, и запись информации необходимо осуществить в ячейку по другому адресу.

На этом цикл записи оканчивается. Таким образом, в выбранной ячейке накопителя информация хранится в прямом или инверсном коде в зависимости от кратности возникшей ошибки, которая может быть исправлена предлагаемым устройством. Значение маркерного разряда (МР) при этом указывает, в каком коде записана информация, в данной ячейке: МР О - прямой код, № 1 - инверсный код.

J3 режиме считывания (г. + к + 1 )- разрядное слово поступает с выбранной ячейки накопителя 1 в регистр 4 слова. И если МР О, то содержимое регистра 4 без изменения передается через блок 8 инвертирования в блок 6 декодирования и на один из входов блока 12 коррекции. Блок 6 фop QIpyeт контрольные соотношения, по которь м дешифратор 7 определяет номер ошибочного разряда (если он есть), посту- паюоий на вторые входы блока 12 кор рекции. В блоке 12 коррекции ошибочный разряд инвертируется, а блок 13 управления формирует управляю1ций сигнал, разрешающий прием потребителем испраатенного слова с выходной и нформационной Ш1ны 15.

Если в выбранной ячейке накопителя исходное слово хралилось в инверсном коде (т.е. МР l), то содержимое регистра слова 4 при передаче через блок 8 инвертируется (благода- Р.Я тому, что МР 1 ) и получается прямой код слова. Далее сохраляется последовательность действий, описанная в предыдущем абзаце.

Формула изобретения

ЗaпoмJ нaюшee устройство с коррекцией ошибок, содержащее блок кодирования, входы которого являются информационными входами ycTpoiicTBa и соединены с входами информационных разрядов вхс дного регистра, входы KOIIT- рольных разрядов которого подключены к выходам блока кодирования, а пькодь соединены с входами первой группы блока определения ошибочных разрядов и с информационными входами накопителя, адресные входы которого являются адресными входами устройства, а выходы подключены к входам регистра слова, выходы которого соединены с входами второй группы блока определения ошибочных разрядов и входами блока инвертирования, выходы которо го подключены к входам первой группы блока коррекции и входам блока декодирования, выходы которого соединены с входами дешифратора, вько- ды которого подключены к входам второй группы блока коррекции, выходы которого являются информационными выходами устройства, один из выходов блока определения ошибочных разрядов соединен с входом признака .записи инверсного слова блока управления, входы записи, чтения и синхронизации которого являются одноименными входами устройства, выход чтения-за- писи блока управления подключен к одноименному входу накопителя, пер-

вый выход синхронизации блока управления соединен с синхровходом входного регистра, второй выход синхронизации блока управления подключен к синхровходу регистра слова, входу обращения накопителя и является выходом готовности устройства, выход признака инверсии блока управления соединен с управляющим входом входного регистра, а выхбд признака неисправимой ошибки блока является одноименным выходом устройства, отличающееся тем, что, с целью упрошения устройства и повьш1ения достоверности контроля, в устройство введены блок совпадения и элемент ШШ, причем входы первой группы блока совпадения соединены с выходами группы блока определения ошибочных разрядов и входами элемента ИЛИ, выход которого подключен к входу признака ошибки блока управления, вход признака совпадения которого соединен с выходом блока совпадения,входы второй группы которого подключены к выходам дешифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с исправлением ошибок | 1983 |

|

SU1133624A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU898509A1 |

| Запоминающее устройство с самоконтролем | 1976 |

|

SU600618A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1149318A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU855730A1 |

| Запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1374286A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Запоминающее устройство | 1972 |

|

SU448480A1 |

| Запоминающее устройство с исправлением ошибок | 1984 |

|

SU1226536A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU875470A1 |

Изобретение относится к вычислительной технике и монет быть использовано при создании высоконадежных запоминающих и вычислительных систем. Целью изобретения является упрощение устройства и повьшение достоверности контроля. Устройство содержит накопитель, входной регистр и регистр слова, блоки кодирования, декодирования и коррекции, дешифратор, блок инвертирования, блок определения ошибочных разрядов, блок управления, элемент ШШ и блок совпадения. Цель изобретения достигается введением в устройство блока совпадения и элемента ИЛИ, позволяющих отказаться от подсчета количества ошибок в считанном слове для определения возможности их кЪррекции, а также использовать в устройстве коды (например, итеративные), для которых количество ошибок в считанном слове не является определяющим фактором при определении возможности их коррекции. 2 ил. (С (Л

amis

om1

13

omS/fOHcifC от б/foffo ff

от 5ло/1с(9

23

21

19

76

2

22

/7

фиг.г

| Устройство для исправления ошибокВ блОКЕ пАМяТи | 1979 |

|

SU842976A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Конопелько В.К., Лосев В.В | |||

| Надежное хранение информации в полупроводниковых запоминающих устройствах | |||

| - Радио и связь, 1986, с.199-200, рис | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-15—Публикация

1986-02-07—Подача