1

Изобретение относится к области вычислительной техники и может быть использовано в буферных запоминающих устройствах (БЗУ) BbicOiKoro .быстродействия.

По основному авт. св. № 375681 известно БЗУ, содержащее поразрядно соединенные регистры, узлы управления перезаписью по числу регистров, выход и один вход каждого из которых подключены соответственно к входу считывания и выходу маркерного разряда одноименного регистра, а другой вход каждого узла управления перезаписью, кроме последнего, подключен к выходу маркерного разряда следующего регистра.

Однако это устройство не обеспечивает необходимого быстродействия при большом количестве регистров из-за многократных последовательных передач между регистрами.

Цель изобретения - повышение быстродействия и увеличение объема известного БЗУ.

Эта цель достигается за счет того, что предложенное устройство содержит узел поиска старшего из свободных регистров, входы которого соединены с выходами .маркерных разрядов каждого регистра, а -выходы- с одними управляющими входами узлов управления перезаписью. Входы одноименных разрядов регистров объединены и соединены с одноименными входами устройства и другими выходами узлов управления перезаписью каждого регистра, кроме первого. Вход управления считыванием устройства подключен к другим управляющим входам

узлов управления перезаписью всех регистров.

При этом входная ннфор.мация записывается сразу в старший нз свободных регистров без МНогократных передач и одновременно

передается инфомация во всех регистрах при считывании, что позволяет увеличить быстродействие БЗУ и число регистров в нем.

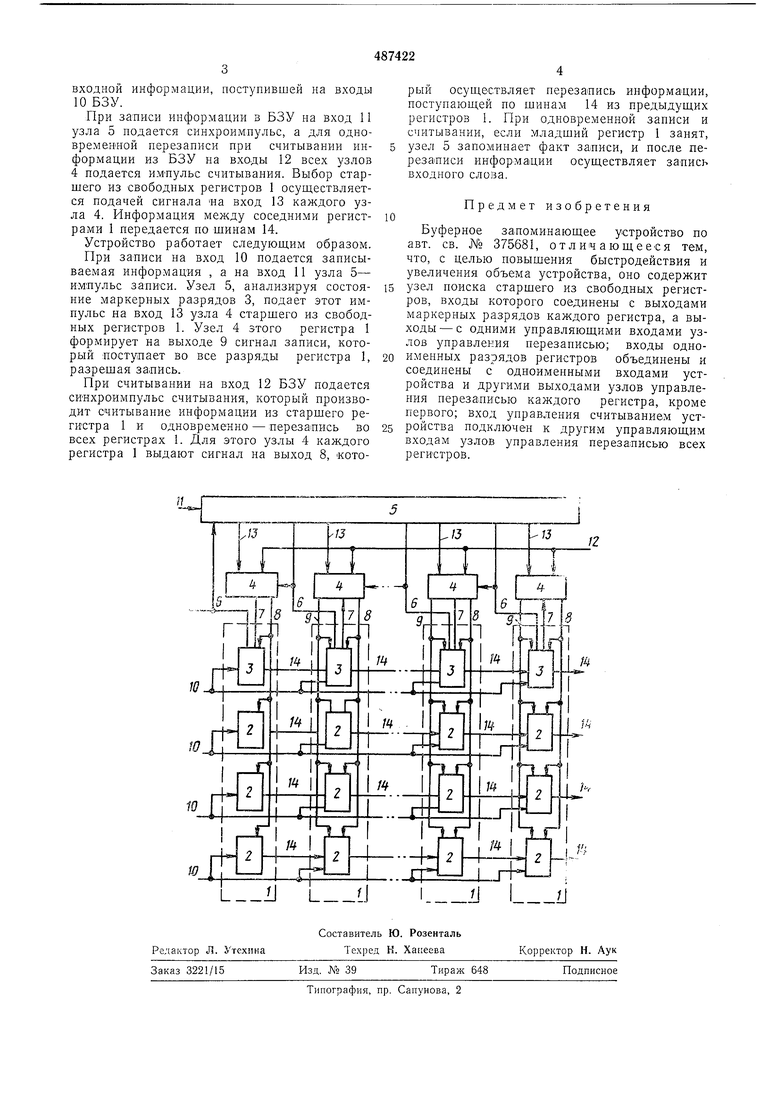

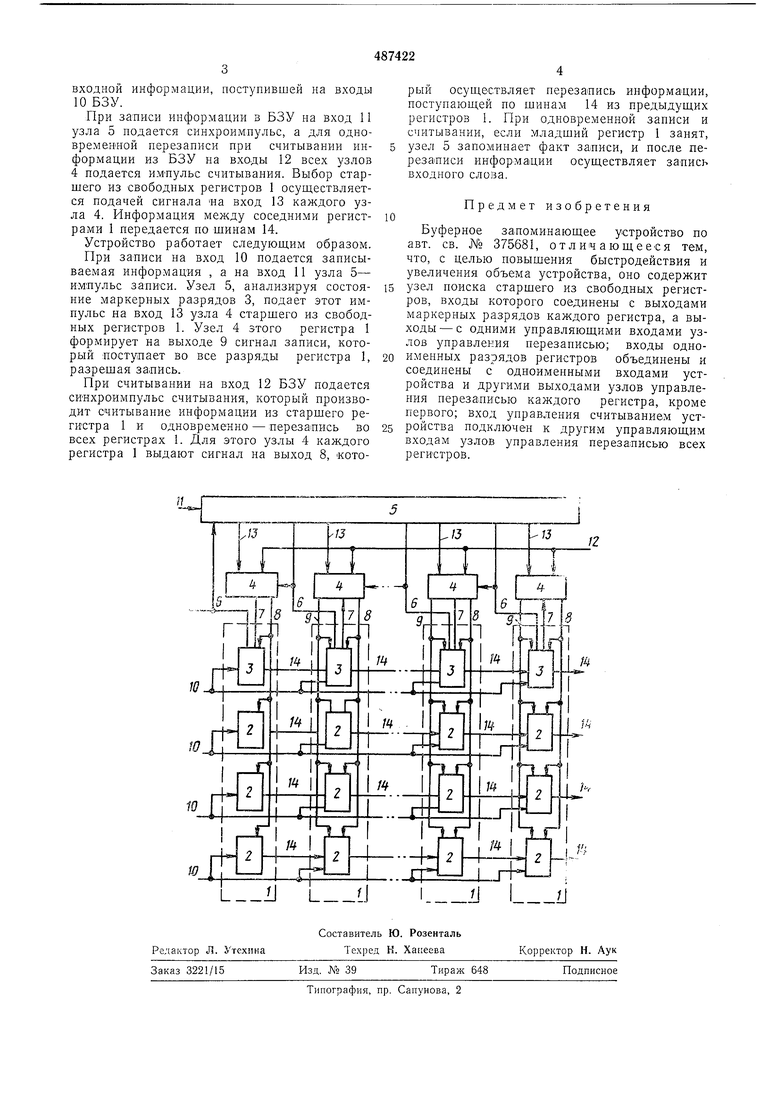

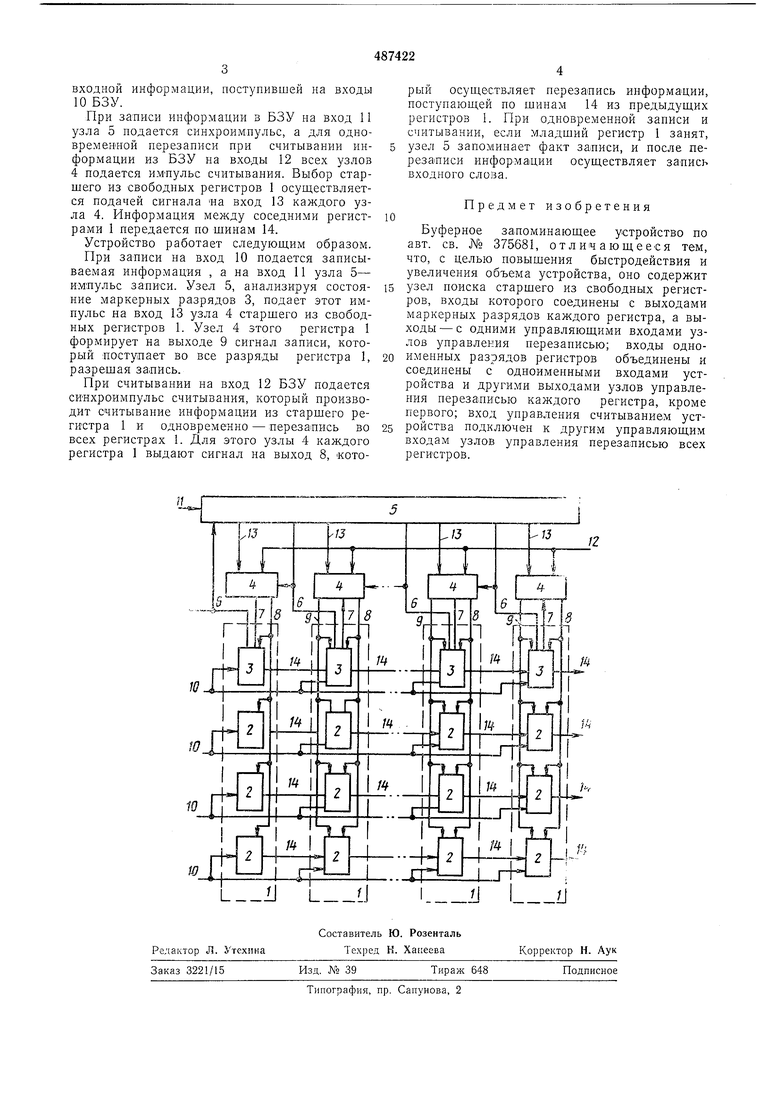

Структурная схема предложенного БЗУ показана на чертеже.

Устройство содержит регистры 1, каждый из которых состоит из информационных разрядов 2 и маркерного разряда 3, узлы 4 управления перезаписью по числу регистров 1, узел 5 поиска старшего из свободных регистров 1. Выход 6 маркерного разряда 3 каждого регистра 1 подключен к входу предыдущего узла 4 управления перезаписью и входам узла 5 поиска старшего из свободных регистров 1. Выход 7 маркерного разряда 3

каждого регистра 1 соединен с входом одноименного узла 4 унравлення перезаписью. Выходная шина 8 узла 4 осуществляет управление перезаписью между двумя соседними регистра.ми 1. Шина 9 узла 4, кроме

первого регистра 1, обеспечивает запись

входной информации, поступившей на входы 10 БЗУ.

При записи информации в БЗУ па вход 11 узла 5 иодается синхроимпульс, а для одновременной перезаписи при считывании информации из БЗУ на входы 12 всех узлов 4 подается импульс считывания. Выбор старшего из свободных регистров 1 осуществляется подачей сигнала ща вход 13 каждого узла 4. Информация между соседними регистрами 1 передается по шинам 14.

Устройство работает следующим образом.

При записи на вход 10 подается записываемая информация , а на вход 11 узла 5- импульс зациси. Узел 5, анализируя состояние маркерных разрядов 3, подает этот импульс на вход 13 узла 4 старшего из свободных регистров 1. Узел 4 этого регистра 1 формирует на выходе 9 сигнал записи, который поступает во все разряды регистра 1, разрешая запись.

При считывании на вход 12 БЗУ подается синхроимпульс считывания, который производит считывание информации из старшего регистра 1 и одновременно - перезапись во всех регистрах 1. Для этого узлы 4 каждого регистра 1 выдают сигнал на выход 8, который осуществляет перезапись информации, поступающей по шинам 14 из предыдущих регистров 1. При одновременной записи и считывании, если младший регистр 1 занят, узел 5 запоминает факт записи, и после переза1писи информации осуществляет запись входного слова,

Предмет изобретения

Буферное запоминающее устройство по авт. св. № 375681, отличающееся тем, что, с целью повыщения быстродействия и увеличения объема устройства, оно содержит

узел поиска старшего из свободных регистров, входы которого соединены с выходами маркерных разрядов каждого регистра, а выходы- с одними управляющими входами узлов управления перезаписью; входы одноименных разрядов регистров объединены и соединены с одноименными входами устройства и другими выходами узлов управления перезаписью каждого регистра, кроме первого; вход управления считыванием устройства подключен к другим управляющим входам узлов управления перезаписью всех регистров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1978 |

|

SU748509A1 |

| Устройство для воспроизведения ВРЕМЕННыХ METOK | 1979 |

|

SU800955A1 |

| Буферное запоминающее устройство | 1980 |

|

SU936029A1 |

| Буферное запоминающее устройство | 1978 |

|

SU746720A1 |

| ВСЕСОЮЗНАЯ пм?нтно^.:^--' Щ | 1973 |

|

SU375681A1 |

| Буферное запоминающее устройствоС АВТОНОМНыМ КОНТРОлЕМ | 1979 |

|

SU842973A1 |

| Буферное запоминающее устройство | 1975 |

|

SU551702A1 |

| Буферное запоминающее устройство | 1980 |

|

SU858109A1 |

| Буферное запоминающее устройство | 1981 |

|

SU1003145A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

Авторы

Даты

1975-10-05—Публикация

1974-01-28—Подача