1

Р1зобретение относится к запоминающим устройствам (ЗУ) и может быть использовано в качестве буферного ЗУ для ЭЦВМ.

Известно ЗУ, содержащее входной регистр, выходы которого подключены ко входам блока основных регистров, соединенных поразрядно, ко 5мутатор, входы которого подсоединены к выходам блока основных регистров, а nepiBbie выходы - к выходному регистру, и схемы «ИЛИ.

Недостатком известного ЗУ является необходимость последовательного считывания храняш,ейся в нем информации из-за отсутствия цнклического доступа к последней.

Целью изобретения является расщирение области применения ЗУ за счет обеспечения циклического доступа .к хранящейся в нем информации.

Описываемое ЗУ отличается от известного тем, что оно содержит сумматор, первый и второй входы которого подключены к дополнительному выходу блока основных регистров и входной щине устройства соответственно, а выходы - ко входам первой схемы «Р1ЛИ и одному из входов введенной в устройство схемы «Запрет. Другой вход последней подсоединен к выходу первой схемы «ИЛИ и одному входу второй схемы «ИЛИ, выход - к другому входу второй схемы «ИЛИ, к дополнительному входу коммутатора i третьему входу сумматора. Выход второй схемы «ИЛИ подключен к четвертому входу сумматора и допол.нительнойму входу блока основных регистров. Вторые выходы коммутатора подключены ко входам введенного в устройство блока буферных регистров, выходы которого соединены со входами блока основных регистров.

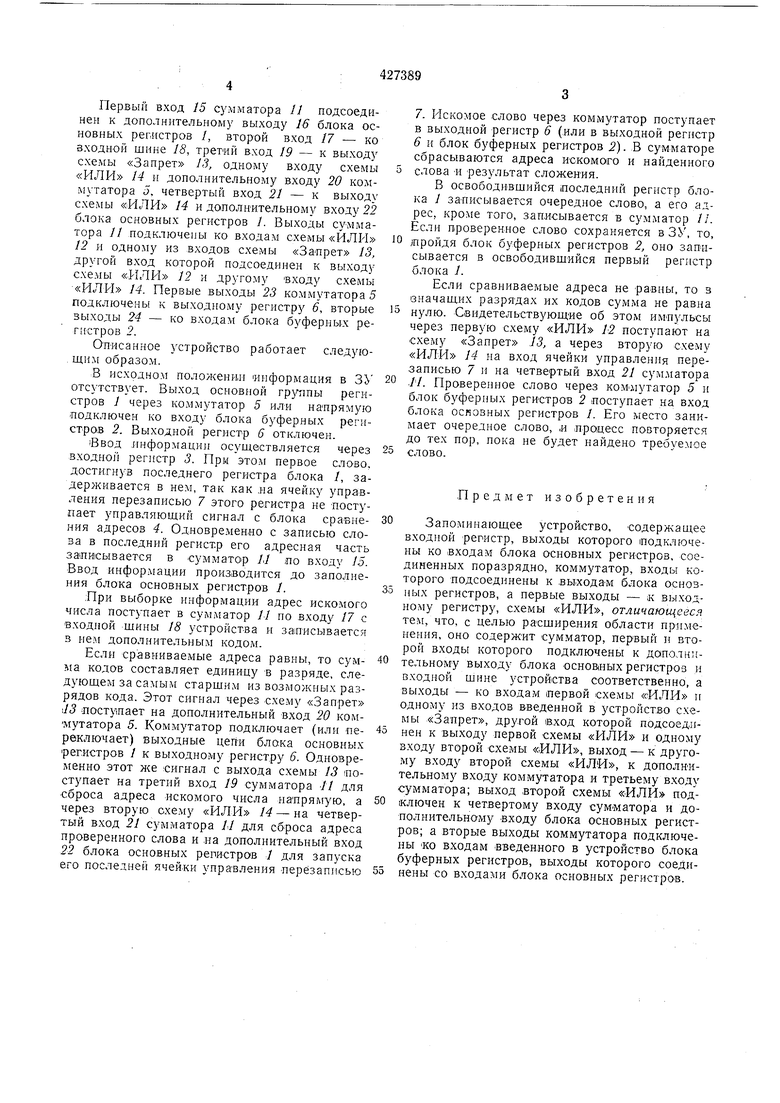

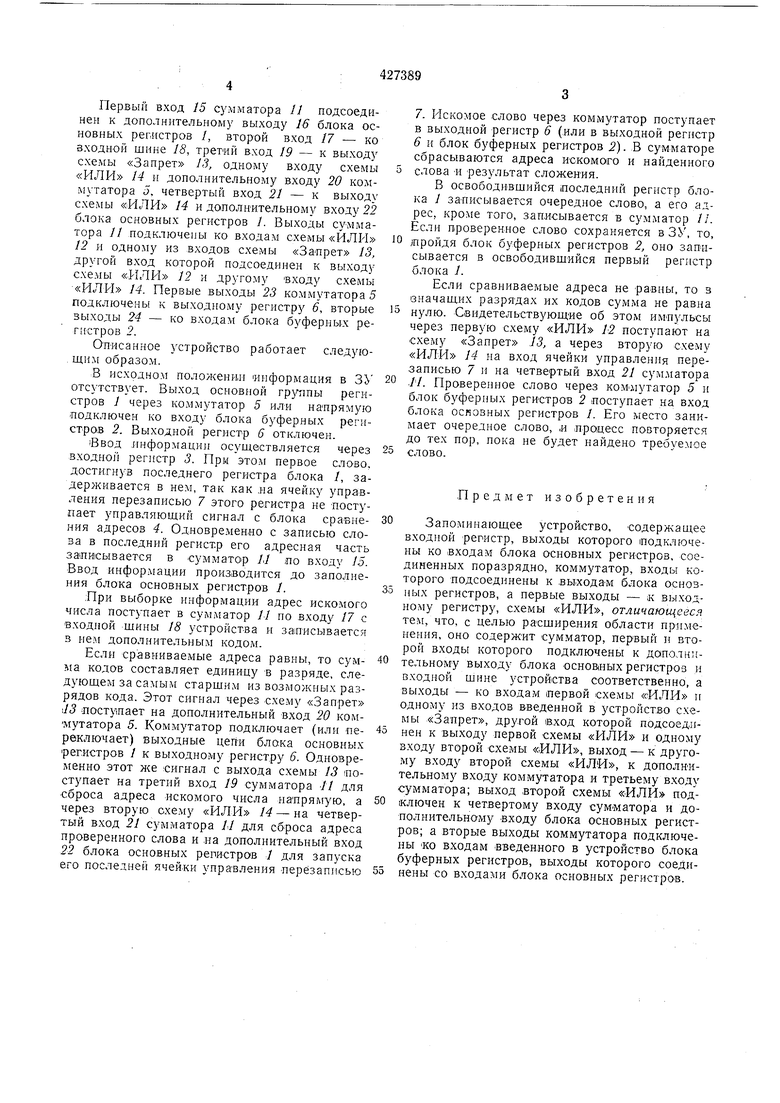

Функциональная схема предложенного ЗУ приведена на чертеже.

ЗУ содержит блок основных регистров /. блок буферных регистров 2, входной регистр 3, блок сравнения адресов 4, ко:ммутатор 5 и выходной регистр 6.

Каждый регистр, являющийся регистром параллельного действия, содержит ячейку управления перезалисью 7, ячейку маркера наличия слова 8, адресную группу разрядов 9 и значащую группу разрядов W.

В состав блока сравнения адресов входят сумматор //, первая схема «ИЛИ 12, схема «Запрет 13 и вторая схема «ИЛИ М.

Выходы входного регистра 3 подключены ко входам блока OCHOBHPJIX регистров 1 и к выходам блока буферных регистров 2.

Первый вход 15 сумматора 11 подсоединен к дополнительному выходу 16 блока основных рег-истров /, второй вход /7 - ко входной шине /5, третий вход 19 - к выходу схемы «Запрет 13, одному входу схемы «ИЛИ 14 и дополнительному входу 20 коммутатора 5. четвертый вход 21 - к выходу схемы «ИЛИ 14 и дополнительному входу 22 блока основных регистров /. Выходы сумматора // подключены ко входам схемы «ИЛИ 12 и одному из входов схемы «Запрет 13, другой вход которой подсоедннен к выходу схемы «ИЛИ 12 и другому входу схемы «ИЛИ 14. Первые выходы 23 коммутатора 5 подключены к выходному регистру 6, вторые выходы 24 - ко входам блока буферных регистров 2.

Описанное устройство работает следующим образом.

В исходном положении информация в 3i отсутствует. Выход основной груяпы регистров 1 через коммутатор 5 или напрямую подключен ко входу блока буферных регистров 2. Выходной регистр 6 отключен.

Ввод .информации осуществляется через входной регистр 3. При этом первое слово, достигнув последнего регистра блока /, задерживается в нем, так как ,на ячейку управления перезаписью 7 этого регистра не -поступает управляющий сигнал с блока сравнения адресов 4. Одновременно с записью слова в последний регистр его адресная часть записывается в -сумматор // по входу 13. Ввод инфор.мации производится до заполнения блока основных регистров /.

При выборке информации адрес искомого числа поступает в сумматор 11 по входу 17 с входной шины J8 устройства и записывается в пе.м дополнительным кодом.

Если сравниваемые адреса равны, то сумма кодов составляет единицу в разряде, следующем за самым старшим из возможных разрядов кода. Этот сигнал через схем} «Запрет il3 поступает на дополнительный вход 20 коммутатора 5. Коммутатор подключает (или переключает) выходные цеПи блока основных регистров / к выходному регистру 6. Одновременно этот же сигнал с выхода схемы / поступает на третий вход 19 сумматора -// для сброса адреса искомого числа напрямую, а через вторую схему «ИЛИ 14 - на четвертый вход 21 сумматора // для сброса адреса проверенного слова и .на дополнительный вход 22 блока основных релистрО(в 1 для запуска его последней ячейки управления перезаписью

7. I-icKOMoe слово через коммутатор поступает в выходной регистр 6 (или в выходной регистр 6 и блок буферных регистров 2). В сумматоре сбрасываются адреса искомого и найденного слова И результат сложевпя.

В освободивщийся последний регистр блока 1 записывается очередное слово, а его адрес, кроме того, записывается в сумматор //. Если проверенное слово сохраняется в ЗУ, то,

лройдя блок буферных регистров 2, оно записывается в освободившийся первый регистр блока /.

Если сравниваемые адреса не равны, то в 8начащ.их разрядах их кодов сумма не равна

нулю. Свидетельствующие об этом импульсы через первую схему «ИЛИ 12 поступают на схему «Запрет 13, а через вторую схему «ИЛИ 14 на вход ячейки управления перезаписью 7 и на четвертый вход 21 сумматора

77. Проверенное слово через коммутатор 5 и блок буферных регистров 2 .поступает на вход блока основных регистров /. Его место занимает очередное слово, ,и процесс повторяется до тех пор, пока не будет найдено требуемое

слово.

Предмет изобретения

Запоминающее устройство, содержащее входной регистр, выходы которого подключены ко входам блока основных регистров, соединенных поразрядно, коммутатор, входы которого подсоединены к вы-хода-м блока оснозHbix регистров, а первые выходы - к выходному регистру, схемы «ИЛИ, отличающееся тем, что, с целью расширения области применения, оно содержит сумматор, первый и второй входы которого подключены к дополнительному выходу блока основ(ных регистров и входной шине устройства соответственно, а выходы - ко входам первой схемы «ИЛИ и одному из входов введенной в устройство схемы «Запрет, другой «.ход которой подсоедлнен к выходу первой схемы «ИЛИ и одному входу второй схемы «ИЛИ, выход - к другому входу второй схемы «ИЛИ, к дополнительному входу коммутатора и третьему входу сумматора; выход второй схемы «ИЛИ подключей к четвертому входу сумматора и дополнительному входу блока основных регистров; а вторые выходы коммутатора подключены КО входам введенного в устройство блока буферных регистров, выходы которого соединены со входами блока основных регистров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1981 |

|

SU1037262A1 |

| Резервное запоминающее устройство | 1976 |

|

SU604036A1 |

| Устройство для распаковки команд | 1984 |

|

SU1196865A1 |

| Запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1444898A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Устройство для сопряжения электронной вычислительной машины с дискретными датчиками | 1982 |

|

SU1084774A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| Арифметическо-логическое устройство для обработки десятичных данных | 1984 |

|

SU1244660A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Многоканальный многомерныйцифРОВОй КОРРЕлОМЕТР | 1978 |

|

SU809199A1 |

Даты

1974-05-05—Публикация

1971-04-19—Подача