Изобретение относится к цифровой вычисчительной технике.

В современных цифровых вычислительных машинах (ЦВМ) часто нрименяют микропрограммное управление выполнением операций. Это объясняется рядом достоинств микропрограммного способа управления: гибкостью, однородностью, надежностью, увеличением быстродействия при выполнении ряда операций.

Микропрограммное устройство управления содержит в своем составе накопитель, в котором хранятся микрокоманды, имеющие операциоиную и адресную части. Число разрядов онерациоииой части обычно соответствует количеству управляющих каналов ЦВМ. В адресной части микрокоманды хранится адрес перехода при выполнеиии микрокоманд передачи управления и в случае принудительного порядка следования микрокоманд-адрес следующей микрокоманды.

В устройстве для управления процессом вычисления на ЦВМ микронрограммы хранятся в статическом накопителе, причем переходы при выполнении микронрограмм осуществляются вынолнением следующей микрокоманды, адрес которой указан в адресной части кода выполняемой микрокоманды.

Известное устройство содержит счетчикрегистр адреса микрокоманд, дешифратор

адреса микрокоманд, накопитель, блок усилителей воснроизведения, регистр микрокоманд и ряд логических элементов, управляющих работой устройства. В качестве датчика сигналов применен статический накопитель, число разрядов которого соответствует количеству управляющих каналов объекта. Кроме этого, имеется несколько разрядов, кодирующих адрес, и три служебных разряда.

Однако при работе такого устройства наблюдается большая разрядность накопителя и регистра слова, составляющая в современных ЦВМ величину порядка 60-100.

Цель изобретения - уменьшить количество

оборудования.

Предлагаемое устройство отличается от известного тем, что в него введен блок собирательных схем и используются сигналы выборки адреса накопителя в качестве унравляюш,их сигналов.

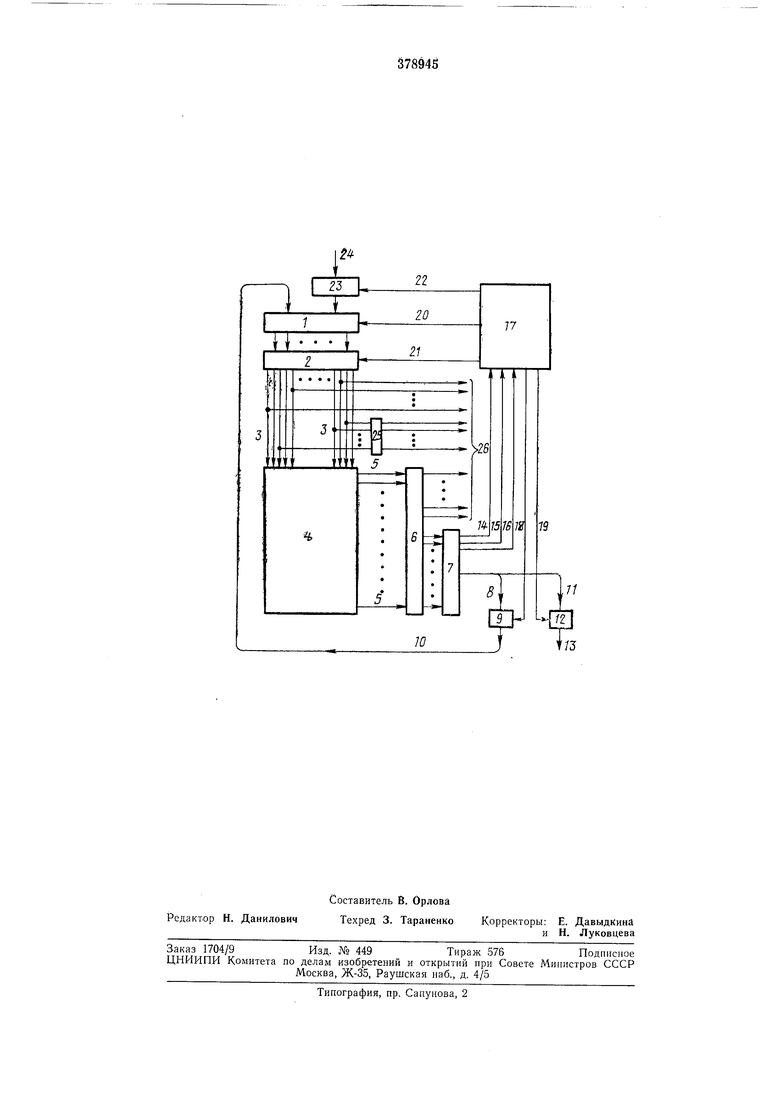

На чертеже дана функциональная схема предлагаемого устройства.

Устройство содержит счетчик / адреса микрокоманд, соединенный через дешифратор

2 адреса микрокоманд с адресными шинами 3 выборки информации из накопителя 4.

Разрядные выходные щины 5 накопителя 4 через блок 6 усилителей воснроизведения соединены со входами регистра 7 микрокоманд,

выход которого через шину 8, блок 9 вентилей передачи адреса микрокоманды и шину 10 подключен ко входам счетчика 1, а через шину 11 и блок 12 вентилей - к шине 13 передачи адресной части микрокоманды во внешнее онерациоппое устройство.

1ри разряда регистра 7 микрокоманд управляюшими шинами М, 15 и 16 соединены с блоком 17 синхронизации, который имеет пять выходных шин: шину 18 опроса блока 9 вентилей, шину 19 опроса блока 12 вентилей, шину 20 управления счетчиком /, шину 21 опроса дешифратора 2 адреса микрокоманд и шину 22 опроса блока 23 вентилей передачи кода онерации по шипам 24 из внешнего операционного устройства.

Устройство имеет блок 25 собирательных схем. Выходные управляюшие шины 26 устройства соединены или с выходами блока 6 усилителей воспроизведения, или с адресными шинами 3 выборки, или с выходами блока 25 собирательных схем, входы которого подключены к адресным шипам 3 выборки.

Предлагаемое устройство работает следуюшим образом.

В исходном состоянии на счетчике / хранится код операции, который был передан по шинам 24 через блок 23 вентилей из внешнего операционного устройства при поступлении управляющего сигнала по шине 22. Код операции является адресом первой микрокоманды микропрограммы вынолнения этой операции.

Цикл работы устройства определяется блоком 17 синхронизации и составляет два такта.

В первом такте импульсом, поступающим по шине 21, проводится опрос дешифратора 2 адреса микрокоманд. При этом возбуждается одна из адресных шин 5 и из накопителя 4 через блок 6 усилителей воспроизведения на регистр 17 микрокоманд считывается микрокомандное слово. Несколько старших разрядов микрокомандного слова, соответствуюшие наиболее часто встречающимся микрооперациям при принятой системе команд, считываются на блок 6 усилителей воспроизведения и возбуждают соответствующие выходные управляющие шины 26. Микрооперации, встречаюшиеся в небольшом числе микрокоманд, реализуются при возбуждепии выходных управляющих шип 26 сигналами выборки адреса на адресных шинах 3 через блок 25 собирательных схем, а мажрооперацни, встречающиеся однократно, минуя блок 25 собирательных схем.

Во втором такте при нулевом значении разряда в регистре 7 микрокоманд, связанного шиной 14 с блоком 17 синхронизации, увеличивается содержимое счетчика 1 импульсом, поступившим по шине 20, и передача адресной части кода микрокоманды во Biienniee операционное устройство по шине 13 путем опроса блока 12 вентилей управляющим импульсом, поступившим по шине 19. При единичном значении этого разряда регистра 7

микрокоманд управляющий потенциал на щине 14 блокирует прибавление единицы к счетчику /, запрещает опрос блока 12 вентилей по шине 19 и опрашивает по шине 18 блок вентилей 9 передачи адреса перехода по шинам W в счетчик /. Таким образом реализуется произвольпый порядок следования микрокоманд.

В дальнейшем цикл работы устройства повторяется.

При необходимости циклического повторения одного или нескольких элементарных действий в соответствуюшем разряде кода микрокоманды, связанном управляюшей шиной 15 с блоком 17 синхронизации, записывается единица; при этом блокируется прибавление единицы к содержимому счетчика / во втором такте.

В последней микро-команде микропрограммы выполнения любой онерации в разряде, связанном унравляющей шиной 16 с блоком 17 синхронизации, записывается единица. В соответствии с этим сигиалом блок 17 синхронизации опрашивает импульсом, поступившим по шине 22 опроса блок 23 вентилей; при этом по шинам 24 на счетчик / поступает код следующей операции из внешнего операционного устройства.

Задержка между моментом передачи адреса в операциопное устройство и поступлением управляющих сигналов, обычно обеспечиваемая последовательным опросом разрядов регистра микрокоманд, хранящих адрес операнда и код микрооперации, в предлагаемом устройстве реализуется специальной структурой микрокомаидного слова, в адресной части которого указывается адрес операнда следующей микрокоманды. При этом каждая микрооперация вынолняется над операндом, адрес которого был передан в операциоппое устройство в предыдущем мнкрокомандном цикле.

Предмет изобретения

Устройство для микропрограммпого управления, содержащее счетчик, соединенный через дешифратор с наконителем, выходы которого через блок усилителей воспроизведения и регистр микрокомаид связаны с блоком синхронизации, первым блоком вентилей, вторым блоком вентилей, выход которого соединен со счетчиком, выходы блока синхронизации подключены к первому и второму блокам веитилей, счетчику, дешифратору и третьему блоку вентилей, выход которого соединен со счетчиком, отличающееся тем, что, с целью уменьшения количества оборудования, в устройство введен блок собирательных схем, а первая грунпа выходных управляющих шин подключена к выходам дешифратора, вторая группа выходных управляющих шин через блок собирательных схем - к выходам дешифратора, третья группа - к выходам блока усилителей воспроизведения.

| название | год | авторы | номер документа |

|---|---|---|---|

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1971 |

|

SU423127A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| АН СССР J „T.'^i''; • •-^^^••';• ^--i^A,. .jf;:.\tC2CO!GC;ri'^^>& плг^иткз •->& | 1965 |

|

SU172567A1 |

| Микропрограммное устройство управления | 1972 |

|

SU437073A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1084793A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386444A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1985 |

|

SU1298762A2 |

| Микропроцессор | 1985 |

|

SU1330634A1 |

| Микропрограммное устройство управления | 1980 |

|

SU934473A1 |

Авторы

Даты

1973-01-01—Публикация