1

Изобретение относится к вычислительной технике и может найти применение в устройствах управления цифровых вычислительных машин (ЦВМ).

Известны микропрограммные устройства управления, содержащие блок постоянной памяти с выходными усилителями, управляемый дешифратором, связанным через группы вентилей с регистрами кода операций и схемой управления за-сылкой адреса микрокоманды с триггером управления.

В известных устройствах разряд регистра, в который поступает признак, не должен изменять своего состояния от прибавления единицы в младший разряд второго регистра кода операций. Это требование приводит к тому, что за каждым признаком должен быть закреплен строго определенный массив памяти, что создает трудности при составлении на уровне микроопераций ветвящихся последовательностей микропрограмм и распределении массива памяти микрокоманд.

Цель изобретения - упрощение программирования на уровне микрооперации при составлении ветвящихся микропрограмм.

Это достигается тем, что в устройство введен блок объединения признаков условного перехода, два входа которого подключены соответственно ко второму и третьему входам устройства, выход блока объединения признаков условного перехода соединен с первыми входами первой и второй схем «И, инверсный выход блока объединения признаков условного перехода подключен к первым входам третьей и четвертой схем «И, вторые входы первой и третьей схем «И соединены с инверсным выходом триггера управления, выход которого подключен ко вторым входам второй и четвертой схем «И, выходы второй и третьей схем «И через первую схему «ИЛИ, выходы первой и четвертой схем «И через вторую схему «ИЛИ подключены соответственно к управляющим входам первой и второй групп схем «И, первые входы пятой и шестой схем «И подключены к первому входу устройства, второй вход пятой схемы «И соединен с выходом первой схемы «И, второй вход шестой схемы «И - с выходом второй схемы «И, выход пятой схемы «И подключен к нулевому входу триггера управления, единичный вход которого соединен с выходом шестой схемы «И, два установочных входа триггера управления подключены соответственно к четвертому и пятому входам устройства.

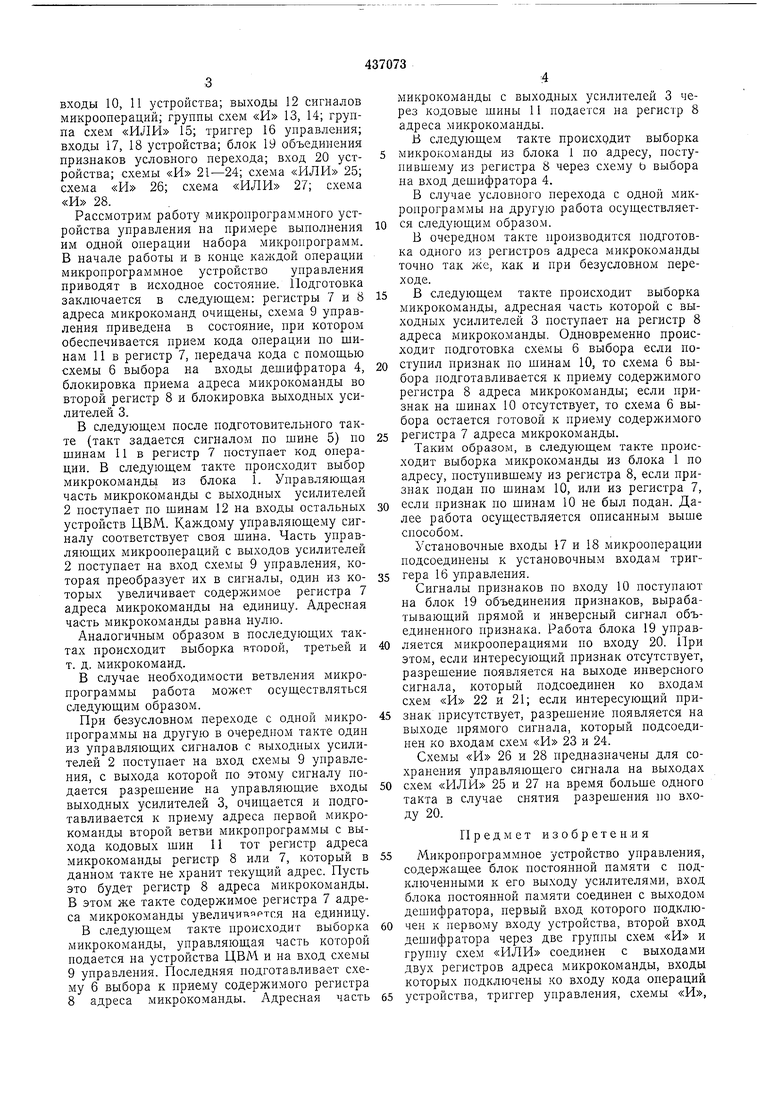

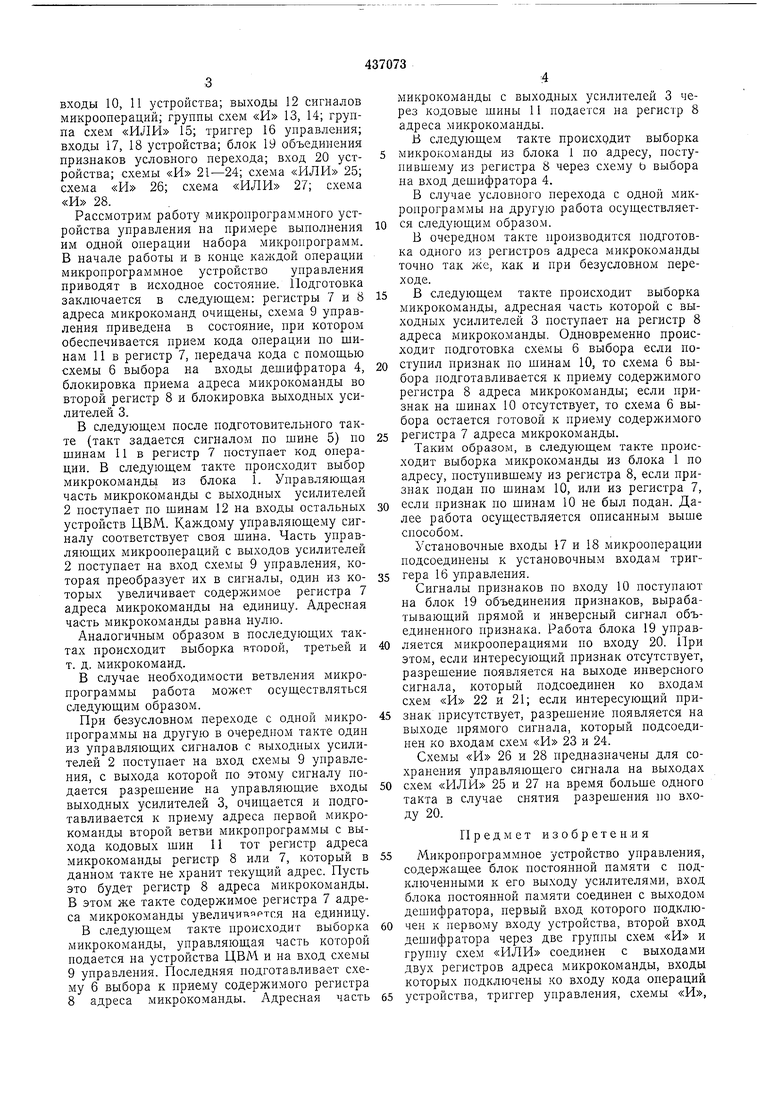

На чертеже представлена схема предлагаемого устройства.

В устройство входят: блок 1 постояпной памяти; усилители 2, 3; дешифратор 4; вход 5 устройства; схема 6 выбора; регистры 7, 8 адреса микроком:анды; схема 9 управления;

входы 10, 11 устройства; выходы 12 сигналов микроопераций; группы схем «И 13, 14; группа схем «ИЛИ 15; триггер 16 управления; входы 17, 18 устройства; блок 19 объединения признаков условного перехода; вход 20 устройства; схемы «И 21-24; схема «ИЛИ 25; схема «И 26; схема «ИЛИ 27; схема «И 28.

Рассмотрим работу микропрограммного устройства управления на примере выполнения им одной операции набора микропрограмм. В начале работы и в конце каждой операции микропрограммное устройство управления приводят в исходное состояние. Подготовка заключается в следующем: регистры 7 и 8 адреса микрокоманд очищены, схема 9 управления приведена в состояние, при котором обеспечивается прием кода операции но шинам 11 в регистр 7, передача кода с помощью схемы 6 выбора на входы дешифратора 4, блокировка приема адреса микрокоманды во второй регистр 8 и блокировка выходных усилителей 3.

В следующем после подготовительного такте (такт задается сигналом но шине 5) по шинам 11 в регистр 7 поступает код операции. В следующем такте происходит выбор микрокоманды из блока 1. Управляющая часть микрокоманды с выходных усилителей 2 поступает по шинам 12 на входы остальных устройств ЦВМ. Каждому управляющему сигналу соответствует своя шина. Часть управляющих микроопераций с выходов усилителей 2 поступает на вход схемы 9 управления, которая нреобразует их в сигналы, один из которых увеличивает содержимое регистра 7 адреса микрокоманды на единицу. Адресная часть микрокоманды равна нулю.

Аналогичным образом в последующих тактах происходит выборка втооой, третьей и т. д. микрокоманд.

В случае необходимости ветвления микропрограммы работа можо.т осуществляться следующим образом.

При безусловном переходе с одной микропрограммы на другую в очередном такте один из управляющих сигналов с выходных усилителей 2 поступает на вход схемы 9 управления, с выхода которой по этому сигналу подается разрешение на управляющие входы выходных усилителей 3, очищается и подготавливается к приему адреса первой микрокоманды второй ветви микропрограммы с выхода кодовых шин 11 тот регистр адреса микрокоманды регистр 8 или 7, который в данном такте не хранит текущий адрес. Пусть это будет регистр 8 адреса микрокоманды.

8этом же такте содержимое регистра 7 адреса микрокоманды увеличи«яртся на единицу.

В следующем такте происходит выборка микрокоманды, управляющая часть которой подается на устройства ЦВМ и на вход схемы

9управления. Последняя подготавливает схему 6 выбора к приему содержимого регистра 8 адреса микрокоманды. Адресная часть

микрокоманды с выходных усилителей 3 через кодовые шины 11 подается на регистр 8 адреса микрокоманды.

В следующем такте происходит выборка микрокоманды из блока 1 по адресу, поступившему из регистра 8 через схему о выбора на вход дешифратора 4.

В случае условного перехода с одной микропрограммы на другую работа осуществляется следующим образом.

В очередном такте нроизводится подготовка одного из регистров адреса микрокоманды точно так же, как и при безусловном переходе.

В следующем такте нроисходит выборка микрокоманды, адресная часть которой с выходных усилителей 3 поступает на регистр 8 адреса микрокоманды. Одновременно происходит подготовка схемы 6 выбора если поступил признак по шинам 10, то схема 6 выбора подготавливается к нриему содержимого регистра 8 адреса микрокоманды; если признак на шинах 10 отсутствует, то схема 6 выбора остается готовой к нриему содержимого

регистра 7 адреса микрокоманды.

Таким образом, в следующем такте происходит выборка микрокоманды из блока 1 по адресу, поступивщему из регистра 8, если признак подан по шинам 10, или из регистра 7,

если признак по шинам 10 не был подан. Далее работа осуществляется описанным выше способом.

Установочные входы 17 и 18 микроонерации подсоединены к установочным входам триггера 16 управления.

Сигналы признаков по входу 10 поступают на блок 19 объединения признаков, вырабатывающий прямой и инверсный сигнал объединенного признака. Работа блока 19 управляется микрооперациями но входу 20. При этом, если интересующий нризнак отсутствует, разрешение появляется на выходе инверсного сигнала, который подсоединен ко входам схем «И 22 и 21; если интересующий нризнак присутствует, разрешение появляется на выходе нрямого сигнала, который подсоединен ко входам схем «И 23 и 24.

Схемы «И 26 и 28 предназначены для сохранения управляюшего сигнала на выходах

схем «ИЛИ 25 и 27 па время больше одного такта в случае снятия разрешения но входу 20.

Предмет изобретения

Микропрограммное устройство управления, содержашее блок постоянной памяти с подключенными к его выходу усилителями, вход блока постоянной памяти соединен с выходом дешифратора, первый вход которого нодключен к первому входу устройства, второй вход дешифратора через две группы схем «И и группу схем «ИЛИ соединен с выходами двух регистров адреса микрокоманды, входы которых подключены ко входу кода операций

устройства, триггер управления, схемы «И,

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| Микропрограммное устройство управления | 1988 |

|

SU1649540A1 |

| МОДУЛЬНОЕ УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2112269C1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

Авторы

Даты

1974-07-25—Публикация

1972-04-07—Подача