1

Изобретение относится к электронню-вычислительной технике и можзт найти применение в запоминающих устройствах цифровых электронно-вычислительных машин.

Известные устройства содержат в каждом разрезе формирователь разрядного тока, записи, подключенный к разрядной обмотке магнитного накопителя и к дифференциальному усилителю, стробирующий усилитель и усилитель-формирователь.

Цель изобретения - повышение помехоустойчивости устройства.

Для этого в каждом разряде предлагаемого устройства введен дополнительный формирователь разрядного тока записи, подключенный к разрядной обмотке магнитного накопителя и к дополнительному дифференциальному усилителю дополнительный стробирующий и две схемы «И, первые входы которых соединены с шиной строба, а вторые входы - с соответствующими кодовыми спинами адреса, выходы схем «И со входами соответствующих стробирующих усилителей, входы которых соединены с выходами соответствующих дифференциальных усилителей, а выходы стробирующих усилителей через схему «ИЛИ - со входом усилителя-формирователя.

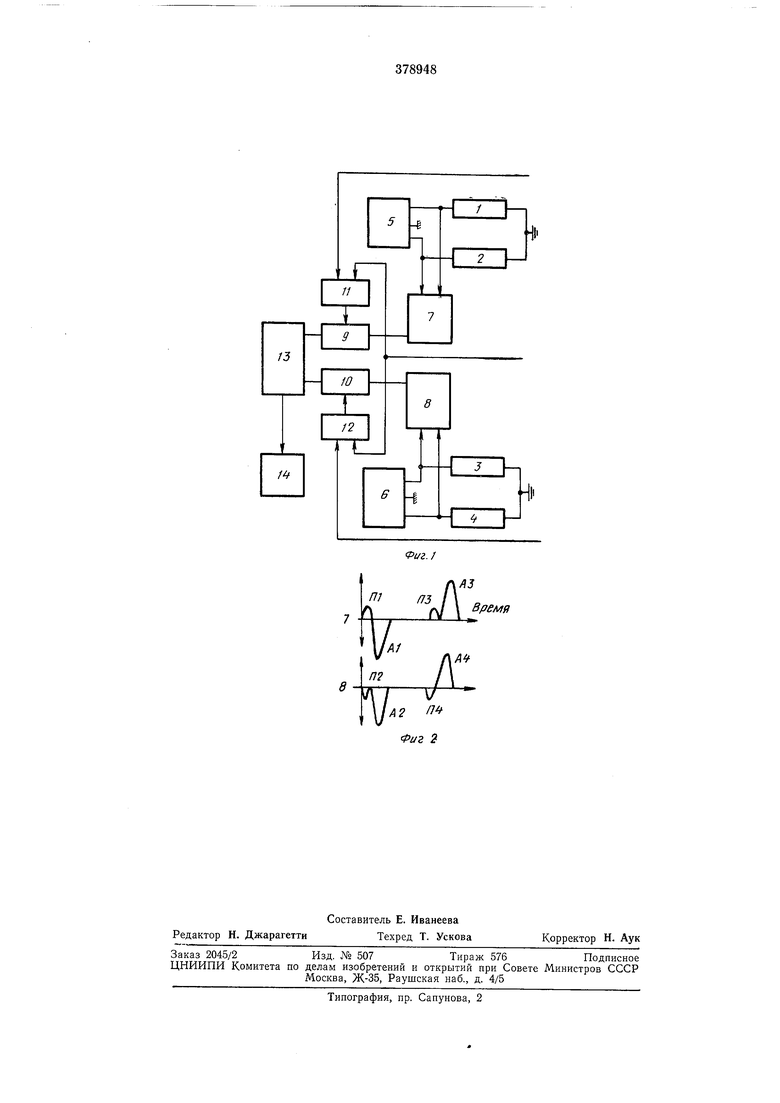

На фиг. 1 представлена блок-схема устройства для временной селекции; на фиг. 2 - осциллограммы сигналов и помех на входах стробирующих усилителей.

Устройство содержит первую 1, 2 л вторую 3, 4 разрядные обмотки магнитного накопителя, включенные в схему моста, формирователи разрядного тока записи 5 и 6, подключенные к соответствующим разрядным обмоткам 1, 2 vi 3, 4. Входы первого однополярного дифференциального усилителя 7 подключены к

первой разрядной обмотке /, 2 магнитного накопителя, а входы второго однополярного усилителя 8 - ко второй разрядной обмотке 3, 4 магнитного накопителя. Выходы дифференциальных усилителей 7, 8 подключены к соответствующим стробирующим усилителям 9, 10. Шина строба и соответствующие кодовые щины адреса подключены ко входам схем «И 11 и 12. Выход схемы «И 11 подключен ко входу первого стробирующего усилителя 9, а

выход схемы «И 12 - ко входу второго стробирующего усилителя 10. Выходы стробирующих усилителей подключены через схему «ИЛИ 13 на вход усилителя-формирователя 14.

Устройство работает следующим образом.

Формирователи разрядного тока 5 и 6 формируют одновременно импульсы записи различной полярности. При считывании информации с запоминающего устройства на вход первого дифференциального усилителя 7 поступают сигнал Л/ и помеха П1, на вход второго дифференциального усилителя 8 - одновременно сигнал А2 и помеха П2. Если же на вход первого дифференциального усилителя 7 поступает сигнал A3 и помеха ПЗ, то на вход второго дифференциального усилителя 9 - одновременно сигнал А4 и помеха П4. Так как дифференциальные усилители однополярные, то при приходе па вход дифференциального усилителя разпополярных сигналов и помех на выходе дифференциального усилителя будет только сигнал. На входе одного стробирующего усилителя возникает только сигнал, на входе другого - помеха и сигвал. При этом сигнал строба (по его шине) поступит через схему 11 или 12 только на тот стробируюш,ий усилитель, па вход которого поступил только сигнал без помехи. Выбор схемы «И (через которую проходит сигнал строба) осуществляют сигналы, поступающие по кодовым щинам адреса на входы схем «И. Сигнал, выделенный одним из стробирующих усилителей, поступает через схему «ИЛИ на вход усилителя-формирователя 14.

Важнейшими технико-экономическими преимуществами использования предлагаемого устройства являются уменьшение помех на входе стробирующего усилителей, увеличение емкости устройства за счет уменьшения помех и упрощения дифференциальных усилителей путем исключения предварительного разбаланса.

Предмет изобретения

Запоминающее устройство, содержащее в каждом разряде формирователь разрядного тока записи, подключенный к разрядной обмотке магнитного накопителя и дифференци0 альнюму усилителю, стробирующий усилитель и усилитель-формирователь, отличающееся тем, что, с целью повышения помехоустойчивости устройства, в его .каждом .разряде введен дополнительный формирователь разрядного тока записи, подключенный к разрядной обмотке магнитного накопителя к дополнительному дифференциальному усилителю, дополнительный стробирующий усилитель и две схемы «И, первые входы которых соеди0 невы с шиной строба, а вторые входы схем «И - с соответствующими кодовыми сигналами адреса, выходы схем «И подключены ко входам соответствующих стробирующих усилителей, входы которых соединены с выходами соответствующих дифференцйвлътгых усилителей, а выходы стробирующих усилителей через схему «ИЛИ - со входом усилителя-формирователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ВРЕМЕННОЙ СЕЛЕКЦИИ | 1970 |

|

SU275128A1 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU392551A1 |

| Запоминающее устройство | 1980 |

|

SU873275A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU375676A1 |

| Запоминающее устройство системы 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1977 |

|

SU693438A1 |

| Полупостоянное запоминающее устройство | 1980 |

|

SU900314A1 |

| Запоминающее устройство | 1978 |

|

SU696543A1 |

| Устройство для записи и считывания информации в трансформаторных накопителях | 1980 |

|

SU942138A1 |

| Логическое запоминающее устройство | 1977 |

|

SU661609A1 |

| Запоминающее устройство | 1973 |

|

SU446108A1 |

Время

Авторы

Даты

1973-01-01—Публикация