- / Изобретение относится к области запоминающих устррйств. Одно из известных устройств имее в составе накопителя набор логических ячеек, которые отличаются от остальных ячеек накопителя более сложной прошивкой управляющих и выходных шин t1. Это требует не толь ко усложнения структуры накопителя запоминающего устройства, увеличени электроники управления накоплтелем, но и организации работы устройства по специальной програкане. Из известных устройств наиболее техническим решением к данному изобретению является логическое запоминающее устройство, содержащее регистр адреса, подключенный к дешифраторам, выходы которых чере адресные формирователи и адресные ключи записи и чтения соединены со входами накопителя, подключенного к разрядным формирователям записи и через усилители чтения соединенного с регистром слова, блок управления 2. Недостатком этого устройства явл ется низкая функциональная возможность, так как он может реализовать только два режима работы (Чтение с регенерацией , Запись с очисткой ) и выполнить только .свои клас.сические функции; запись информации в накопитель, её хра:нение и выдачу (чтение) информации из блЬка накопителя. Это; снижает также область применения устройства. ДРУГИМ недостатком устройства является неэффективное использование времени цикЛа работы устройства, так как в нем Исключается возможность чтения информации из одной ячейки накопителя и записи другой информации в ту же или любую другую ячейку накопителя за время одного цикла обращения к устройству, что снижает быстродействие устройства. Целью настоящего изобретения является расширение области применения и повышение быстродействия устройства. Поставленная цель достигается тем, что устройство содержит триггеры, блок формирования сброса и эле-. менты И и ИЛИ, причем первый выход блока управления подключен к первым входам первого и второго элементов И, выходы которых первый элемент ИЛИ соединены с разрешающими входами адресный ключей и с первым входом второго элемента ИЛИ, второй

выход блока управления подключен к первым входам третьего и четвертого элементов И, выходы которых через третий элемент ИЛИ соедин ы с разрешающими входами адресныхключей записи и со вторым входом второго элемента ИЛИ, выход которого подключен к разрешающим входам адресных формирователей, вторые входы пё рвЪгО и третьего элементов И подключены к единичному выходу первого триггера, -вторые входы второго и четвертого элементов И подключены к ёДйничному выходу второго триггера, третьи входы второго и четвертого элементов И подключены соответственно к третьему и четвертому выходам .блока управления, выходы второго и четвертого элементов И подключены через последовательно соединенные четвертый элемент ИЛИ и блок формирования сброса к первому входу пятого элемента ИЛИ, выход которого соединен с установочными входами регисров адреса и слова, второй вход пятого элемента ИЛИ соединен с пятым выходом блока управления и нулевыми входами триггеров, единичные входы которых соединены соответственно со входами блока управления.

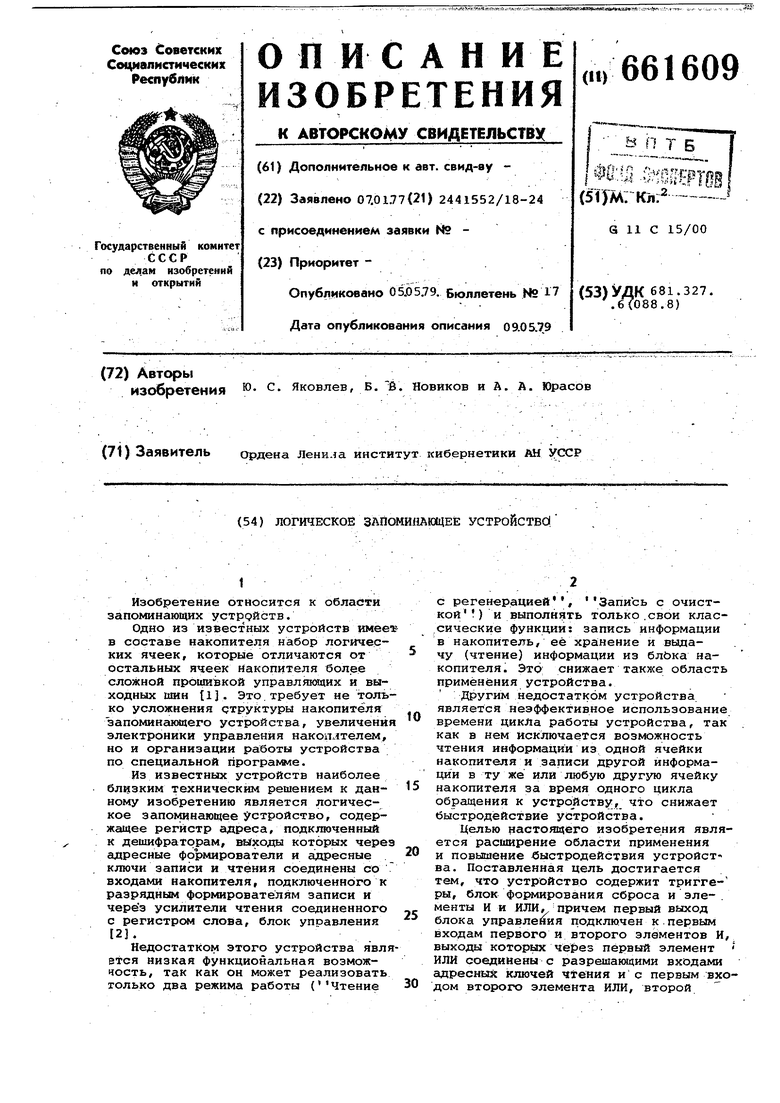

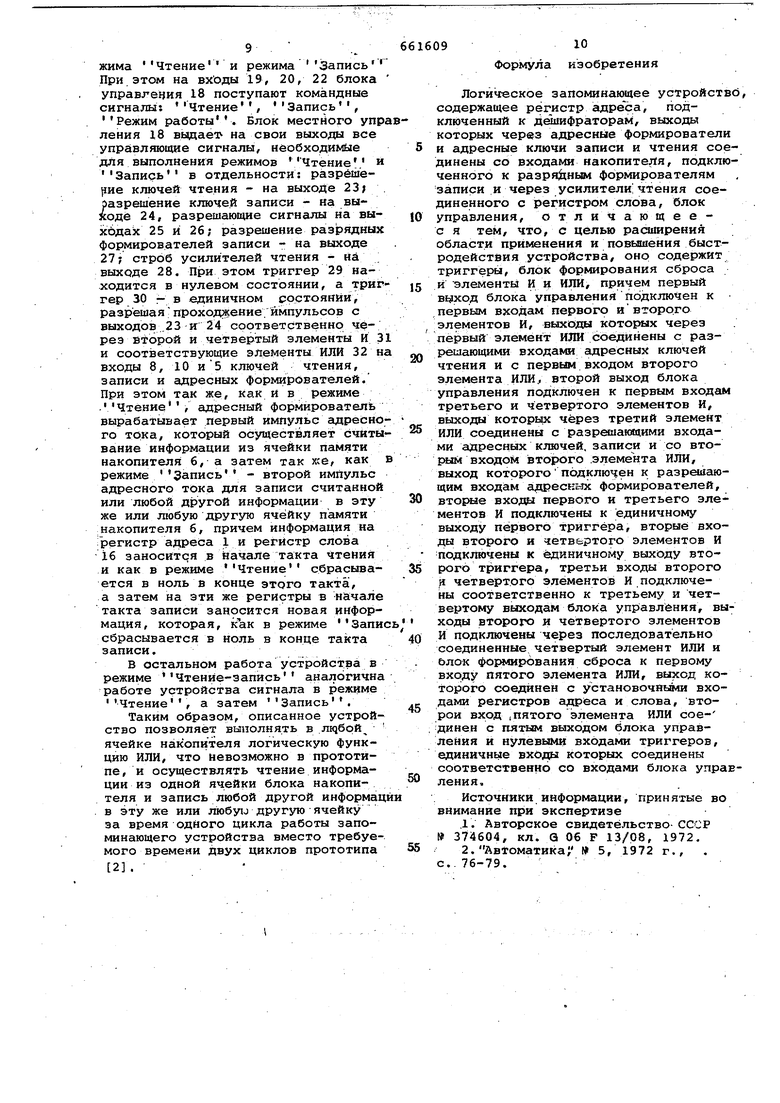

, Схема предложенного устройства, изображена на фиг. 1, на фиг. 2 приведена диаграмма его работы в различных режимах. Устройство содержит (см. фиг. 1) регистр адреса 1 со входом 2 установки в ноль, дешифратор 3,адресные формирователи разрешающим входом 5, накопител 6 на многоотверстных ферритовых платинах, адресные ключи чтения 7 с разрешающим входом 8, адресные ключи записи 9 с разрешающим входом 10, дешифратор 11, разрядные формирователи записи 12с разрешающим входом 13, усилители чтения 14 со входом стробирования 15, регистр слова 16-со входом 17 установки в ноль. Устройство содержит также блок управления 18 с командными входами чтения. 19, записи 20, обращения 21, разрешения 22 и с выходами 3-28.

Устройство содержит также триггер ,29 -для временного хранения командного, сигнала Обращение, триггер 30 для временного хранения командного сигнала Режим работы элементы И 31, элементы ИЛИ 32 и блок формирования сброса 33.

Первый выход 23 блока 18 подключен к первым входам первого и второго элементов И 31, выходы которы через первый элемент ИЛИ 32 соединены с разрешающими входами В ключей 7 и с первым входом второго элемента ИЛИ 32. Второй выход 24 блока 18 подключен к первым входам третьего и четвертого.элементов И 31, выходы которых через третий элмент ИЛИ 32 соединены с разрешающими входами 10 ключей 9 и со вторым входом второго элемента ИЛИ 32, выход которого подключен к разрешающим входам 5 формирователей 4. Вторые входы первого и третьего элементов И 31 подключены к единичному выходу первого триггера 29, вторые входы второго и четвертого элементов И подключены к единичному выходу второго триггера 30, третьи

входы второго и четвертого элементов

И 31 подключены соответственно к третьему 25 и четвертому 26 выходам блока 18. Выходы второго и четвертого элементов И 31 подключены через

последовательно соединенные четвертый элемент ИЛИ 32, б.лок 33 к первому входу пятого элемента ИЛИ 32, выход которого соединен с установочными входами регистров 1 и 16. Второй

0 вход пятого элемента ИЛИ 32 соединен с пятым выходом 34 блока 18 и нулевыми входами триггеров 29, 30, единичные входы которых соединены соответственно со входами 21 и 22

блока 18.

Устройство работает следующим образом. . , .

При обращении к устройству на k входы 19-22 блока управления- 18 поступают командные сигналь, определяющие режимы работы устройства: Чтение с регенерацией, Запись с ОЧИСТКОЙ , Чтение, Запись. Чтение-запись , /

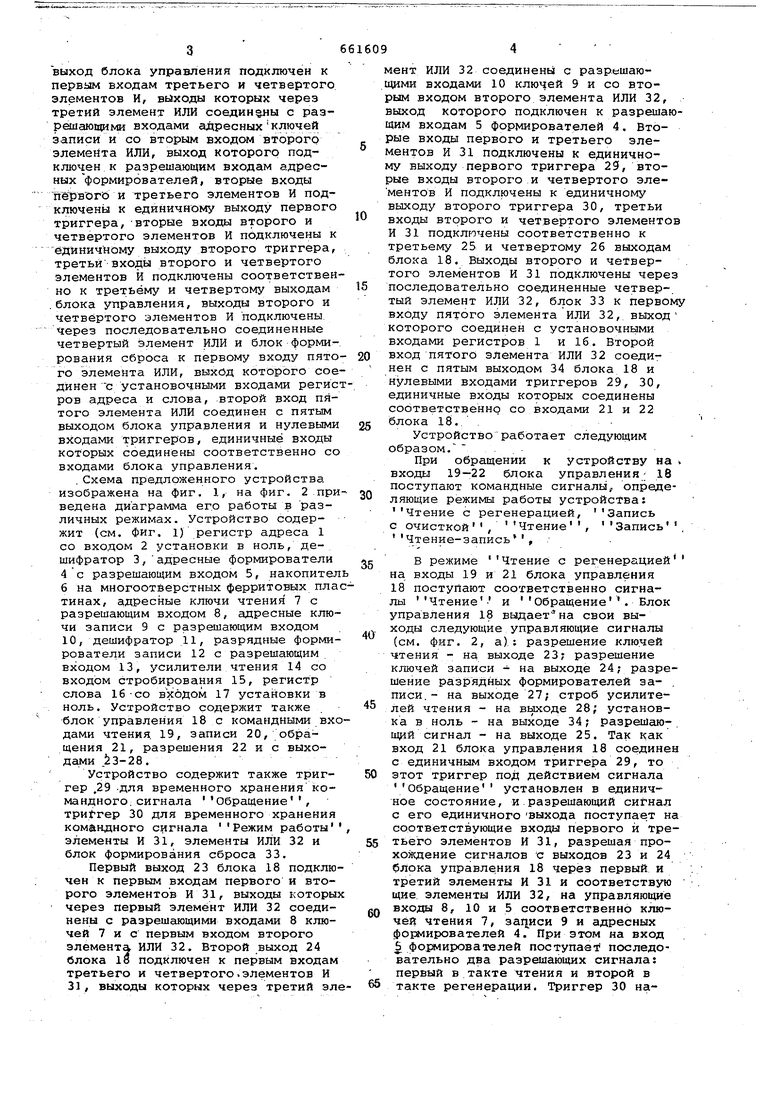

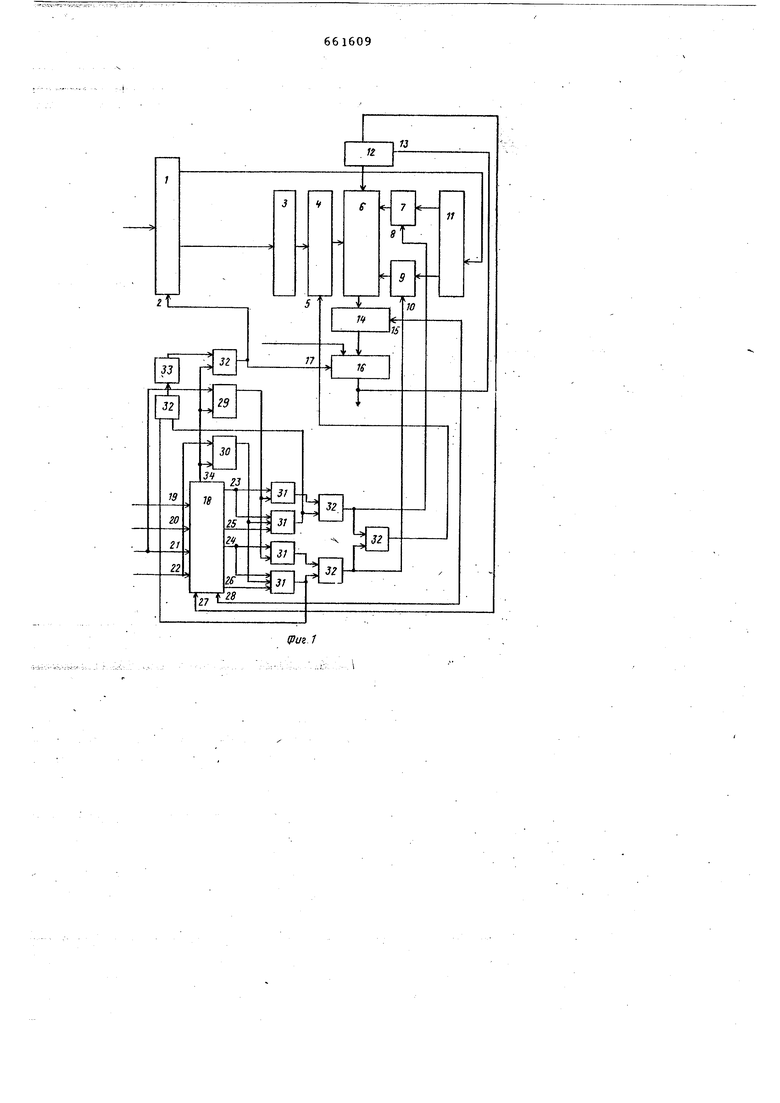

5 В режиме Чтение с регенерацией на входы 19 и 21 блока управления 18 поступают соответственно сигналы Чтение и Обращение . Блок управления 18 выдает на свои выходы следующие управляющие сигналы (см. фиг. 2, а) S разрешение клю.чей чтения - на выходе 23 разрешение ключей записи - на выходе 24; разрешение разрядных формирователей записи,- на выходе 27; строб усилителей чтения - на вькоде 28; установка в ноль - на выходе 34; разрешаю-. шдй сигнал - на выходе 25. Так как вход 21 блока управления 18 соединен с единичным входом триггера 29, то

50 этот триггер под действием сигнала Обращение установлен в единичное состояние, и.разрешающий сигнал с его единичного выхода nocTynaesT на соответствующие входы первого и третьего элементов И 31, разрешая прохождение сигналов С выходов 23 и 24 блока управле,ния 18 через первый и третий элементы И 31 и cooTBeTCTBsno щие, элементы ИЛИ 32, на управляющие

gQ входы 8, 10 и 5 соответственно ключей чтения 7, 9 и адресных формирователей 4. При этом на вход S формирователей поступает последовательно два разрешающих сигнала: первый в такте чтения и второй в

65 такте регенерации. Триггер 30 находится в нулевом состояньи, и потенциал с его единичного выхода запрещает прохождение сигналов через второй и четвертый элементы и 31. Одновременно с сигналом Обращение по кодовым шинам адреса на вход регистра адреса 1 поступает код адреса, который на нем запоминается. Ко адреса расшифровывается дешифраторами 3 И 11, каждый из которых на. одном из своих выходов вырабатывает сигнал запуска соответственно адресного формирователя 4, сигнал запуска соответствующего ключа чтения . 7 и одноименного ключа записи 9. Так.как на разрешающих входах 5, 8,10 этих ключей присутствуют разрешающие сигналы, то возбужденный адресный формирователь выдает на соответствующий вход накопителя 6 импульсы адресного тока чтения (первый) и записи (второй), а возбужденные ключи чтения и записи коммутируют в соответствующее время их прохождение через выбранную ячейку памяти накопителя 6. При этом в такте чтения под действием первого импульса адресного тока параметры элементов памяти выбранной ячейки памяти накопителя 6 изменяются, и на разрядных выходах накопителя 6 появляются выходные сигналы, которые при наличии импульса.строба на входе 15 усилителей чтения 14 преобразуются в усилителях чтения в стандартные сигналы слова. Это слово заносится на регистр слова 16 и с его выходов поступает на выходные шины устройства и на соответствую-щие входы разрядных формирователей записи 12.

В такте регенерации с выхода 27 блока управления 18 на вход 13 разрядных формирователей записи 12 поступает сигнал разрешения. Если в разряде выбранной ячейки накопител происходит регенерация информации О , то разрядный формирователь записи, соответствующий этому разряду, запускается и вырабатывает импульс разрядного тока записи, который компенсирует действие на элемент памяти выбранно.й ячейки памяти накопителя 6 адресного тока записи. При этом переключение элемента памяти не происходит. Если осуществля, то разрядется регенерация

ный формиро ватель записи не вырабатывает комп°енсирующего разрядного тока, и адресный ток записи (второй импульс адресного тока) перемагничивает элемент памяти в состояние . Как при регенерации ,

так и при регенерации

разрядный формирователь записи в такте регенерации вырабатывает дополнительный импульс тока установки, не совпадающий с действием адресного тока (этот импульс на фиг. 2 не показан).

переключающий элемент памяти из состояния

в состояние разрушенной

Информация на регистре слова 16 и на регистре адреса 1 сбрасывается в ноль импульсом установки в ноль, 5 который с выхода 34 блока управления 18 поступает на соответствующие входы 17 и 2 этих регистров через элемент ИЛИ 32.

В режиме Запись с очи,сткой

0 на входы 20 и 21 блока управления 18 поступают соответственно сигналы Запись и .Обращение . Блок управления 18 выдает на свои выходы следующие управляющие сигналы

5 (см. фиг. 2, б): разрешение ключей чтения - на выходе 23; разрешение ключей записи - на выходе 24; разрешение разрядных формирователей записи - на выходе 27; установка, в ноль - на выходе 34; разрешающий

сигнал - на выходе 26. Работа устройства в режиме Запись с очисткой аналогична работе устройства в режиме Чтение с регенерацией за исключением следующих осрбен нос5 теи. В такте чтения при реализации режима Запись с очисткой на вход 15 усилителей чтения 14 не поступает импульс строба, и информация, считанная из выбранной ячейки памяти

0 накопителя 6, не заносится на регистр слова 16 (теряется). При этом в такте записи на входных кодовых шинах слова выставляют код слова, который заносится на регистр слова

5 16 и с его выходов поступает на соответствующие входы разрядных формирователей записи 12, каждый из; разрядных формирователей которого заЬускается и вырабатывает разрядQ ный ток записи при записи О, и не вырабатывает тока записи , при записи ..

Информация на регистре слова 16 и на регистре адреса 1 сбрасывает ся в ноль так же, как и в режиме

5 IЧтение с регенерацией , импульсом установки в ноль.

В режиме Чтение на входы 19 и 22 блока управления 18 поступают соответственно сигналы Чтение и

0 Режим работы .. Блок управления 18 выдает на выходы следующие управляющие сигналы (см. фиг. 2, в): раз-, решение ключей чтения - на выходе 23, разрешение ключей записи - на выходе 24; строб усилителей чтения на выходе 28; разрешающий сигнал на выходе 25.

Так как вход 22 йлока управления 18 соединен с единичным входом тригQ гера 30, то .этот триггер под действием сигнала Режим работы установлен в единичное состояние , и разрешающий сигнал с его единичного выхода поступает на соответствующие входы второго и четвертого элементов

И 31, разрешая прохождение сигналов с выхода 23 блока управления 18 через (Второй элемент И 31 и соответст вующие элементы ИЛИ 32 на управляющи входы 8 и 5 соответственно ключей чтения 7 адресных формирователей 4 (первый импульс). При этом на выходе 26 блока управления 18 сигнал отсутствует, и поэтому на вход 10 ключей записи 9 разрешающего сигнала не поступает Исоответственно на входе 5 адресных формирователей отсутствует второй разрешающий сигнал - i . . - Триггер 29 находится в нулевом СОСТОЯНИИ, и потенциал с его единичного выхода запрещает прохождение си налов с вь1ходов 23 и 24 блока управ ления 18 через первый и третий элементы И 31. Одновременно с сигналом Режим работы по кодовым шинам адреса на вход регистра адреса 1 . поступает код адреса, который на не запоминается. Код адреса расщифровывается детйифраторами 3, 11, кажды из которых на одном из.своих выходов соответственно вырабатывает сиг нал запуска адресного формирователя блока 4, сигнал запуска соответству щего ключа чтения 7 и одноименно-, го ключа записи 9. Так как раЭ решаю щий сигнал присутствует на входе 8 ключей 7, а на входе 5 адресных формирователей 4 присутствует только первый разрешающий импульс, то возбужденный адресный формирователь выдает на соответствующий вХбд накопителя 6 -ТОЛЬКО импульс адресного тока чтения (первый), а возбужденны ключ.чтения 7 коммутирует его прохождение через выбранную ячейку, па мяти нак.-.пителя- б. При этом под Дей ствием адресного тока параметры эле MeHTQB памяти выбранной ячейки нако пителя б изменяются и на раэрядйых выходах накопителя 6 появляются выходные сигналы, которые при наличии импульса с троба на входе 15 усилите лей чтения 14 преобразуются в усили телях чтения в стандартные .сигналы слов а V Это слово заносит с я на регистр слова 16 и С его выходов пос тупает на выходные шины устройства и на соответствующие входа разрядных формирователей записи 12. .Информация на регистре слова 16 и регистре адреса 1 сбрасывается в Hojfe-импульсом установки в ноль, который формируется по длительност сразу же после окончания импульса адресного тока чтения блоком формирования сброса 33, на вход крто рой через элемант ИЛИ 32 поступает сигнал с выхода второго элемента И 31. В связи с отсутствием второго импульса содресного тока и разрешающего сигнала, на входе 13 разрядных формирователей записи 12 такт регенерации при рабрте ус трой;ства в реЧтениене выполняется. 8 В режиме Запись на выходы 0 и 22 блока управления 18 поступают Запись оответственно сигналы .Режим работы БЛОК местного правления 18 выдает на выходы слеующие управляющие сигналы (см. иг. 2, г): разрешение ключей чтенияна выходе 23, разрешение ключей заиси - на выходе 24, разрешающий сигнал - на выходе 26; разрешение разрядных формиройателей записи - на выходе 27. При этом триггер 30 так же, как И при выполнении режима Чтение4 установлен в единичное состояние, а триггер 29 - в нулевое. Однако в . отличие от режима Чтение в реЗаписьвместо разреша.кндего сигнала на выходе 23 блока управления 18 вырабатыв,ается сигнал на . выходе 26 .этого же блока, поэтому сигнал с выхода 24 блока управлеЕгия 18 через четвертый элемент И 31 и соответствующие элементы ИЛИ 32 поступает на разрешающие входы 10 и 5 соответственно ключей записи 9 и адресных формирователей 4. При этом адресный формирователь вырабатывает только второй импульс адресного тока (такт записи), ив тот же момент времени открывается соответствующий ключ записи, коммутирующий прохождение этого тока через выбранную ячейку памяти накопителя 6. Одновременно с сигналом разрешения ключей записи на входных кодовых шинах :слова выставляют код слова, который заносится на регистрслова 16 и с его выходов поступает на соответствующие входы блока разрядных формировате.пей Записи 12, каждый из разрядных формирователей которого запускается и вырабатывает разрядный ток записи при записи и не вырабатывает тока записи при записи . Информация на регистре слова 16 и на регистре адреса 1 сбрасывается в ноль импульсом установки вноль, который формируется по длительности сразу же после окончания импульса адресного тока записи блоком формирования сброса 33, на вход которой через элемент ИЛИ 32 поступает сигнал с выхода четвертого элемента И 31. В связи с отсутствием первого импульса адресного тока такт чтения при работе с устройства в режшле Запись не выполняется, что дает возможность осуществлять запись информации в любую ячейку накопителя без ее предварительной очистки. Если в выбранной ячейке накопителя находилось слово А и осуществляется запись в нее слова В, то после реализации режима Запись в этой ячейке образуется слово С, как результат выполнения логической функции ИЛИ над словами А, В. Режим Чтение-запись ( см. фиг. 2, д) является комбинацией режима Чтение и режима Запись При этом на входы 19, 20, 22 блока управления 18 поступают командные сигналы: Чтение , Запись, Режим работы . Блок местного уп ления 18 в1адает на свои выходы все управляющие сигналы, необходимые для выполнения режимов Чтение Запись в отдельности: разрёшерие ключей чтения - на выходе 23; разрешение ключей записи - на выходе 24, разрешающие сигналы на вы хода 25 и 26; разрешение разрядны фор|мирователей записи - на выходе 27; строб усилителей чтения - на выходе 28. При этом триггер 29 находится в нулевом состоянии, а три гер 30 - в единичном состоянии, разрешаяпроходщение, импульсов с выходов .23 и 24 соответственно через Второй и четвертый элементы И и соответствующие элементы ИЛИ 32 входы 8, 10 и 5 ключей чтения, записи и адресных формирователей. При этом так же, как и в режиме .Чтение адресный формирователь вырабатывает первый импульс адресно го тока, который осуществил нет считы вание информации из ячейки памяти накопителя 6, а затем так хсе, как режиме Запись - второй импульс адресного тока для записи считанной или любой другой информации в эту же или любую другую ячейку памяти накопителя 6, причем информация на регистр адреса 1 и регистр слова 16 заносится в начале такта чтения и как в режиме Чтение сбрасывается в ноль в конце этого такта, а затем на эти же регистры в начале такта записи заносится новая информация, которая, как в режиме Запи сбрасывается в ноль в конце такта записи. В остальном работа устройства в режиме Чтение-запись аналогична работе устройства сигнала в режиме Запись Чтение а затем Таким образом, описанное устройство позволяет выполнять в ячейке накопителя логическую функцию ИЛИ, что невозможно в прототипе , и осуществлять чтение информации из одной ячейки блока накопителя и запись любой другой информа в эту же или другую ячейку за время одного цикла работы запоминающего устройства вместо требуемого времени двух циклов прототипа 10 09 изобретения Формула Логическое запоминающее устройстве), содержащее регистр адреЪа, подключенный к ййиифраторам, выходы которых через адресные формирователи и адресные ключи записи и чтения соединены со входами накопителя, подключенного к разрядным формирователям записи и через усилители чтения соединенного с регистром слова, блок управления, отличающеес я тем/ что, с целью расширения области применения и повышения быстродействия устройства, оно содержит триггеры, блок формирования сброса и элементы И н ИЛИ, причем первый выход блока управления подключен к первым входам первого и второго элементов И, выходфы которых через первый элемент ИЛИ соедйНены с разрешающими входами адресных ключей чтения и с первым входом второго элемента ИЛИ., второй выход блока управления подключен к первым входам третьего и четвертого элементов И, выходы которых через третий элемент ИЛИ соединены с разрешающими входами адресных ключей, записи и со втоЕ лм входом второго .элемента ИЛИ, выход которого подключен к разрешающим входам адресных формирователей, входам первого и третьего элементов И подключены к единичному выходу первого Триггера, вторые входы второго и четвертого элементов И подключены к единичному выхзду второго триггера, третьи входы второго и четвертого элементов И подключены соответственно к третьему и четвертому выходам блока управления, выходы второго и четвертого элементов И подключены через последовательно соединенные четвертый элемент ИЛИ и ьлок формирования сброса к первому входу пятого элемента ИЛИ, выход которого соединен с установочньми входами регистров адреса и слова, второй вход (ПЯТОГО элемента ИЛИ соединен с пятью выходом блока управления и нулевыми входами триггеров, единичные входа которых соединены соответственно со входами блока управления, Источники информации, принятые во внимание при экспертизе .1. Авторское свидетельство- СССР 374604, кл. Q 06 F 13/08, 1972. 2. Автоматика; 5, 1972 г., с..76-79. :

„ Обращение

„ Режим ройоты

Чтение „Sanuck

Разрешение Срерни/яЧатеяя

Разрешение

WW CU/C/TC

fлfova7 о

Разрешение

зрешен1 juavas xjuavas f

Страд

о

Разрешение ни1)о1отеляпо

. cSpec

ечход opMupotamem

выход кпюча 7

выход клюпз

ток

ВыпадI у Вылад

юрнироеапеляп Р-J

И -

Разрядный

I ток

Выход усипшпелячч

Виход peeucmpoif Выход I petucm/ioJ

| название | год | авторы | номер документа |

|---|---|---|---|

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Буферное запоминающее устройство | 1989 |

|

SU1654875A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для обмена информацией | 1989 |

|

SU1695316A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Запоминающее устройство | 1983 |

|

SU1115105A1 |

| Запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1444898A1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1501160A1 |

| Устройство для ввода информации | 1989 |

|

SU1695314A1 |

Авторы

Даты

1979-05-05—Публикация

1977-01-07—Подача