Изобретение относится к области вычислительной техники и может быть использовано в ЗУ на магнитных элементах. Известно ЗУ с автономным контролем 1, содержащее накопитель, регистры адреса и числа, усилители счи тывания, схемы свертки по -модулям 2 и 3, схемы сравнения, схемы ИЛИ и.; схему формирования обратного кода, В устройстве- предусмотрена возможность обнаружения одиночных ошибок при -считывании:Числа из накопителя, а также контроль исправности адресных цепвй... - , : . Недостатками этого устройства являются /бол ыйие аппаратурные затраты и .не.возможность обнаружения кратных ошибок в считанном из накопителя числе, что снижает его надежность. Наиболее близким из известных по технической сущности к изобретению является ЗУ 2, содержащее накопитель с адреснЕлми и разрядными цепями, блок местного управления, регистры кодового слова и силы коррек тирующего кода, триггер операции, схему равенства кодов, блоки кодиро вания и декодирования, схему опреде ления кратности ошибок и блоки схем И и ИЛИ. За счет использования временной избыточности, и корректирующих кодо переменной силы это устройство способно обнаруживать очшбки любой кратности, но это достигается за счет значительных - аппаратурных затрат и усложнения устройства. Целью изобретения является упрощение устройства. Поставленная цель достигается тем, что 3 ЗУ f - cbдetэжaщeм накопитель на магнитных элементах, вход которого подключен.к первому выходу Формирователя импульсов, выходы накопителя соединены-с первыми входами первых элементов И, вторые входы которых соединены со BTOPEJM выходом формирователя импульсов, вторые и третьи элементы И, элементы ИЛИ и регистр, .первые входы вторых элементов И соединены с выходами накопителя на магнитных элементах, выходы первых элементов И подключены к одним из входов элементов ИЛИ, другие входы вторых элементов И соединены с третьим выходом формирователя импульсов, ныходы вторых элементов И соединены с

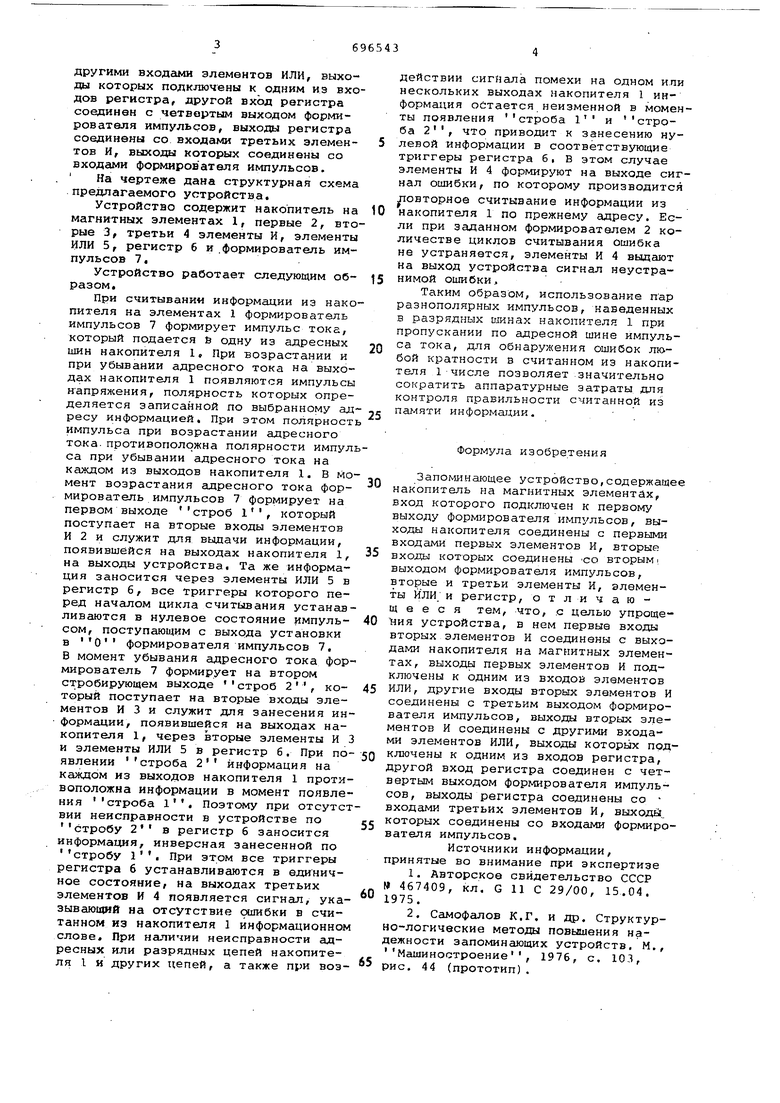

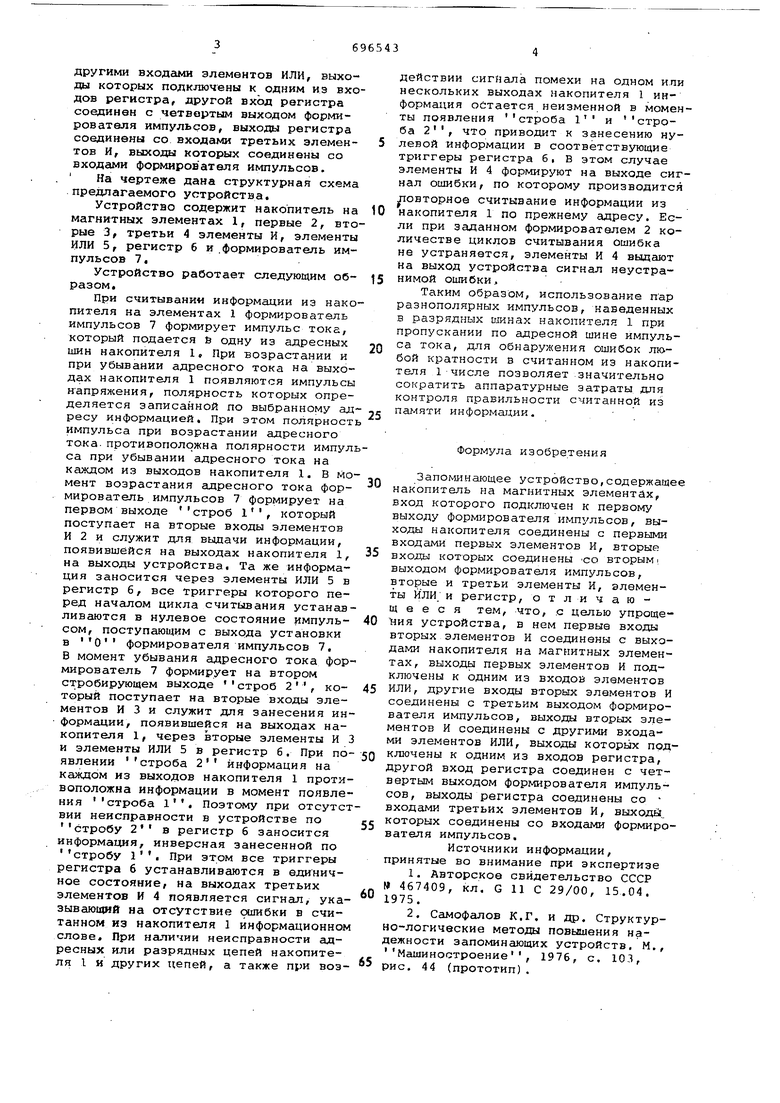

другими входгиъш элементов ИЛИ, выходы которых подключены к одним из входов регистра, другой вход регистра соединен с четвертым выходом формирователя импульсов, выходы регистра соединены со входами третьих элементов И, выходы которых соединены со входами формнрователя импульсов. На чертеже дана структурная схема предлагаемого устройства.

Устройство содержит накопитель на магнитных элементах 1, первые 2, вторые 3f третьи 4 элементы И, элементы ИЛИ 5, регистр б и .формирователь импульсов 7.

Устройство работает следующим образом.

При считывании информации из накопителя на элементах 1 формирователь импульсов 7 формирует импульс тока, который подается и одну из адресных шин накопителя 1, При возрастании и при убывании адресного тока на выходах накопителя 1 появляются импульсы напряжения, полярность которых определяется записанной по выбранному адресу информацией. При этом полярность импульса при возрастании адресного то-ка. противоположна полярности импульса при убывании адресного тока на каждом из выходов накопителя 1. В Момент возрастания адресного тока формирователь импульсов 7 формирует на первом выходе строб , который поступает на вторые входы элементов И 2 и служит для выдачи информации, появившейся на выходах накопителя 1, на выходы устройства. Та же информация заносится через элементы ИЛИ 5 в регистр б, все триггеры которого перед началом цикла считывания устанавливаются в нулевое состояние импульсом, поступающим с выхода установки в О формирователя импульсов 7, В момент убывания адресного тока формирователь 7 формирует на втором стробирующем выходе строб 2, который поступает на вторые входы элементов И 3 и служит для занесения информации, появившейся на выходах накопителя 1, через вторые элементы И 3 и элементы ИЛИ 5 в регистр 6. При появлении строба 2 информация на каждом из выходов накопителя 1 противоположна информации в момент появления строба 1. Поэтому при отсутствии неисправности в устройстве по стробу в регистр 6 заносится информация, инверсная занесенной по стробу 1. При этом все триггеры регистра 6 устанавливаются в единичное состояние, на выходах третьих элементов И 4 появляется сигнал, указывающий на отсутствие сшибки в считанном из накопителя 1 информационном слове. При наличии неисправности адресных или разрядных цепей накопителя 1 и других 11епей, а также при воздействии сигнала помехи на одном или нескольких выходах накопителя 1 информация остается неизменной в моменты появления строба 1

строба 2, что приводит к занесению нулевой информации в соответствующие триггеры регистра 6, В этом случае элементы И 4 формируют на выходе сигнал ошибки, по которому производится

ловторное считывание информации из накопителя 1 по прежнему адресу. Если при заданном формирователем 2 количестве циклов считывания ошибка не устраняется, элементы И 4 выдают на выход устройства сигнал неустранимой ошибки.

Таким образом, использование пар разнополярных импульсов, наведенных в разрядных минах накопителя 1 при пропускании по адресной шине импульса тока, для обнаружения ошибок лю.бой кратности в считанном из накопителя 1 числе позволяет значительно сократить аппаратурные затраты для контроля правильности считанной из naf-iHTH информации.

Формула изобретения

Заподминающее устройство,содержаще накопитель на магнитных элементйх, вход которого подключен к первому выходу формирователя импульсов, выходы накопителя соединены с первыми входами первых элементов И, вторые входы которых соединены СО вторым выходом формирователя импульсов, вторые и третьи элементы И, элементы ИЛИ и регистр, отличающееся тем, что, с целью упрощения устройства, в нем первые входы вторых элементов И соединены с выходами накопителя на магнитных элементах, выходы первых элементов И подключены к одним из входов элементов ИЛИ, другие входы вторых элементов И соединены с третьим выходом формирователя импульсов, выходы вторых элементов И соединены с другими входами элементов ИЛИ, выходы которых подключены к одним из входов регистра, другой вход регистра соединен с четвертым выходом формирователя импульсов, выходы регистра соединены со входами третьих элементов И, выходи. которых соединены со входами формирователя импульсов.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 467409, кл. G 11 С 29/00, 15.04. 1975.

2.Самофалов К.Г, и др. Структурно-логические методы повышения надежности запоминающих устройств, М., Машиностроение, 1976, с. 103, рис. 44 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции ошибок в информации | 1986 |

|

SU1372365A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Запоминающее устройство | 1980 |

|

SU873275A1 |

| Запоминающее устройство | 1978 |

|

SU696542A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Запоминающее устройство системы 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1977 |

|

SU693438A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Запоминающее устройство | 1985 |

|

SU1259336A2 |

| Запоминающее устройство с исправлением ошибок | 1980 |

|

SU955207A1 |

| Запоминающее устройство с самоконтролем | 1988 |

|

SU1522292A1 |

Авторы

Даты

1979-11-05—Публикация

1978-05-15—Подача