1

Изобретение относится к области запоминающих устройств.

Известно запоминающее устройство, содержащее накопитель с подключенными к нему формирователями токов считывания и записи и двухкаскадными дифференциальными усилителями считывания, в которых выход первого каскада соединен с первым входом второго каскада, выход каждого из усилителей подключен к входу соответствующей схемы стробирования, связанной с пороговой схемой, а между первым и вторым входами второго каскада усилителя включена линия задержки.

Однако в известном устройстве при введении дополнительных разрядных щин уменьщаются полезная площадь матриц и количество разрядов в числе, при этом уменьшается вдвое количество запоминающих элементов, обслуживаемых одним усилителем считывания; кроме того, в разрядных щинах возникают помехи, наводимые цепями токов считывания.

Предлагаемое устройство отличается от известного тем, что оно содержит две дополнительные линии задержки в каждом разряде, вход первой из которых соединен с щиной считывания и с одним входом соответствующего формирователя тока считывания, а выход - с другим входом этого формирователя и с управляющим входом схемы стробирования.

вторая дополнительная линия задержки включена между выходом первого каскада и вторым входом второго каскада дифференциального усилителя считывания.

Это,позволяет увеличить емкость и помехоустойчивость устройства.

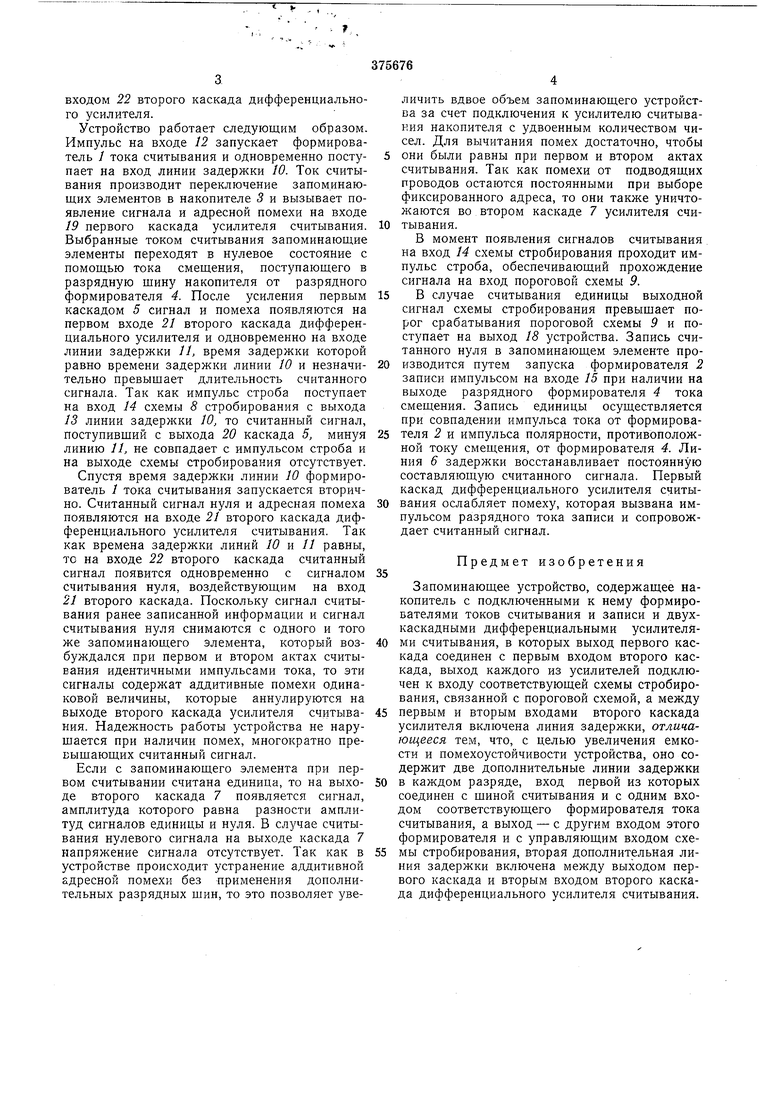

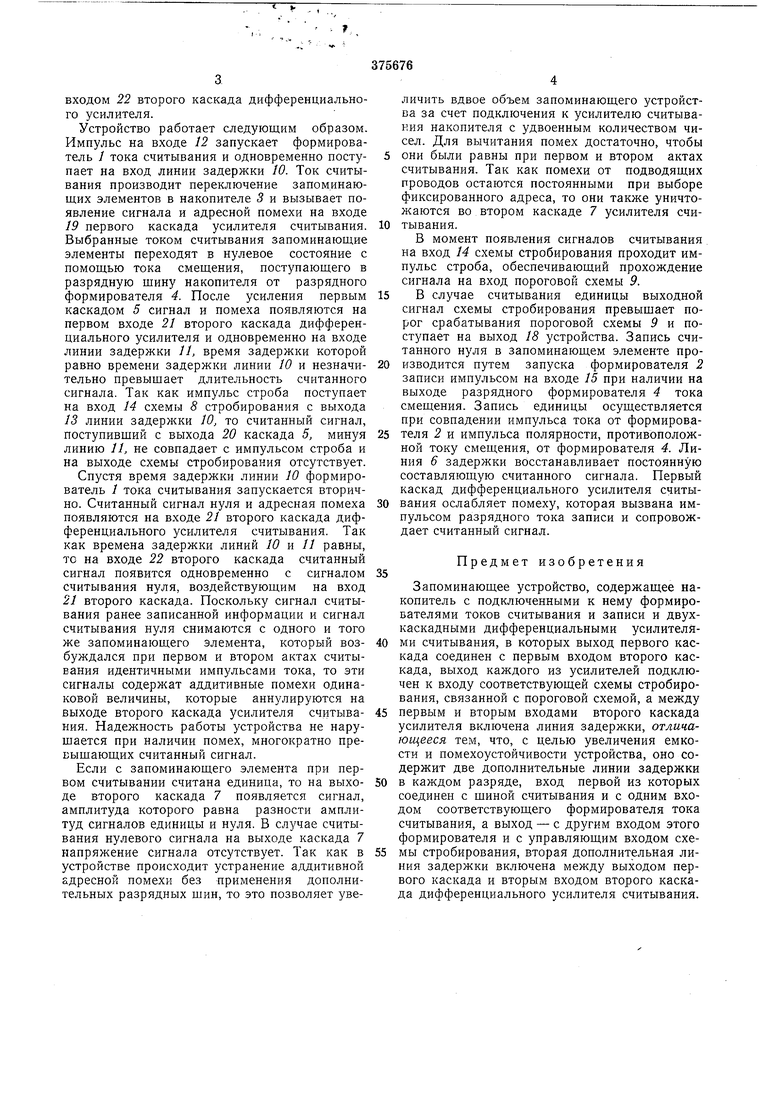

На чертеже изображена блок-схема запоминающего устройства.

Устройство содержит формирователь / тока

считывания, формирователь 2 тока записи, накопитель 3, разрядный формирователь 4, первый каскад 5 дифференциального усилителя считывания, линию б задержки, второй каскад 7 дифференциального усилителя считывания, схему 8 стробирования, пороговую схему 9, первую дополнительную линию W задержки и вторую дополнительную линию 11 задержки. Вход 12 линии 10 задержки соединен с входом формирователя / тока считывания,

а ее выход 13 - с входом 14 схемы 8 стробирования. Вход 15 является входом формирователя 2 тока записи. Управляющие импульсы поступают на входы 16 и 17 разрядного формирователя 4, вход 17 связан с выходом 18

пороговой схемы 9. Входы 19 первого каскада дифференциального усилителя соединены с выходами разрядного формирователя 4, а его выход 20 соединен с первым входом 21 второго каскада дифференциального усилителя.

Выход линии задержки 11 соединен с вторым

входом 22 второго каскада дифференциального усилителя.

Устройство работает следующим образом. Импульс на входе 12 запускает формирователь / тока считывания и одновременно поступает на вход линии задержки 10. Ток считывания производит переключение запоминающих элементов в накопителе 3 и вызывает появление сигнала и адресной помехи на входе 19 первого каскада усилителя считывания. Выбранные током считывания запоминающие элементы переходят в нулевое состояние с помощью тока смещения, поступающего в разрядную щину накопителя от разрядного формирователя 4. После усиления первым каскадом 5 сигнал и помеха появляются на первом входе 21 второго каскада дифференциального усилителя и одновременно на входе линии задержки 11, время задержки которой равно времени задержки линии 10 и незначительно превыщает длительность считанного сигнала. Так как импульс строба поступает на вход 14 схемы 8 стробирования с выхода 13 линии задержки 10, то считанный сигнал, поступивщий с выхода 20 каскада 5, минуя линию //, не совпадает с импульсом строба и на выходе схемы стробирования отсутствует.

Спустя время задержки линии 10 формирователь 1 тока считывания запускается вторично. Считанный сигнал нуля и адресная помеха появляются на входе 21 второго каскада дифференциального усилителя считывания. Так как времена задержки линий 10 и 11 равны, то на входе 22 второго каскада считанный сигнал появится одновременно с сигналом считывания нуля, воздействующим на вход 21 второго каскада. Поскольку сигнал считывания ранее записанной информации и сигнал считывания нуля снимаются с одного и того же запоминающего элемента, который возбуждался при первом и втором актах считывания идентичными импульсами тока, то эти сигналы содержат аддитивные помехи одинаковой величины, которые аннулируются на выходе второго каскада усилителя считывания. Надежность работы устройства не нарущается при наличии помех, многократно преБыщающих считанный сигнал.

Если с запоминающего элемента при первом считывании считана единица, то на выходе второго каскада 7 появляется сигнал, амплитуда которого равна разности амплитуд сигналов единицы и нуля. В случае считывания нулевого сигнала на выходе каскада 7 напряжение сигнала отсутствует. Так как в устройстве происходит устранение аддитивной адресной помехи без применения дополнительных разрядных щин, то это позволяет увеличить вдвое объем запоминающего устройства за счет подключения к усилителю считывания накопителя с удвоенным количеством чисел. Для вычитания помех достаточно, чтобы они были равны при первом и втором актах считывания. Так как помехи от подводящих проводов остаются постоянными при выборе фиксированного адреса, то они также уничтожаются во втором каскаде 7 усилителя считывания.

В момент появления сигналов считывания на вход 14 схемы стробирования проходит импульс строба, обеспечивающий прохождение сигнала на вход пороговой схемы 9.

В случае считывания единицы выходной сигнал схемы стробирования превыщает порог срабатывания пороговой схемы 9 и поступает на выход 18 устройства. Запись считанного нуля в запоминающем элементе производится путем запуска формирователя 2 записи импульсом на входе 15 при наличии на выходе разрядного формирователя 4 тока смещения. Запись единицы осуществляется при совпадении импульса тока от формирователя 2 и импульса полярности, противоположной току смещения, от формирователя 4. Линия 6 задержки восстанавливает постоянную составляющую считанного сигнала. Первый каскад дифференциального усилителя считывания ослабляет помеху, которая вызвана импульсом разрядного тока записи и сопровождает считанный сигнал.

Предмет изобретения

Запоминающее устройство, содержащее накопитель с подключенными к нему формирователями токов считывания и записи и двухкаскадными дифференциальными усилителями считывания, в которых выход первого каскада соединен с первым входом второго каскада, выход каждого из усилителей подключен к входу соответствующей схемы стробирования, связанной с пороговой схемой, а между

первым и вторым входами второго каскада усилителя включена линия задержки, отличающееся тем, что, с целью увеличения емкости и помехоустойчивости устройства, оно содержит две дополнительные линии задержки

в каждом разряде, вход первой из которых соединен с щиной считывания и с одним входом соответствующего формирователя тока считывания, а выход - с другим входом этого формирователя и с управляющим входом схемы стробирования, вторая дополнительная линия задержки включена между выходом первого каскада и вторым входом второго каскада дифференциального усилителя считывания.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU392551A1 |

| Запоминающее устройство | 1980 |

|

SU873275A1 |

| УСИЛИТЕЛЬ СЧИТЫВАНИЯ | 1973 |

|

SU374656A1 |

| Устройство для считывания информации из накопителя | 1980 |

|

SU864334A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU378948A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Запоминающее устройство | 1981 |

|

SU982093A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU299871A1 |

| Полупостоянное запоминающее устройство | 1978 |

|

SU765875A1 |

Авторы

Даты

1973-01-01—Публикация