1

Изобретение относится к области цифровой вычислительной техники.

Известно устройство для формирования контрольного разряда двоичного счетчика, содержащее дешифратор, дизъюнктивный элемент и триггер контрольного разряда.

В этом устройстве значение контрольного разряда, являющееся дополнением количества единиц числа, находящегося в счетчике в данном такте до нечетного (четного), формируется на основе анализа изменения содержимого нечетных разрядов счетчика. При этом быстродействие снижается, так как минимальный период следования импульсов счета должен быть равен сумме времени срабатывания самого счетчика, времени срабатывания схемы управления триггером контрольного разряда и времени срабатывания триггера контрольного разряда.

В предлагаемом устройстве формирование контрольного разряда совмещено во времени с процессом распространения переносов в счетчике. Вместо дешифраторов, определяющих такт изменения состояния разрядов счетчика, формирование значения контрольного разряда в данном такте обеспечивается на основе анализа содержимого счетчика в предыдущем такте.

Это позволяет существенно сократить время формирования значения контрольного разряда.

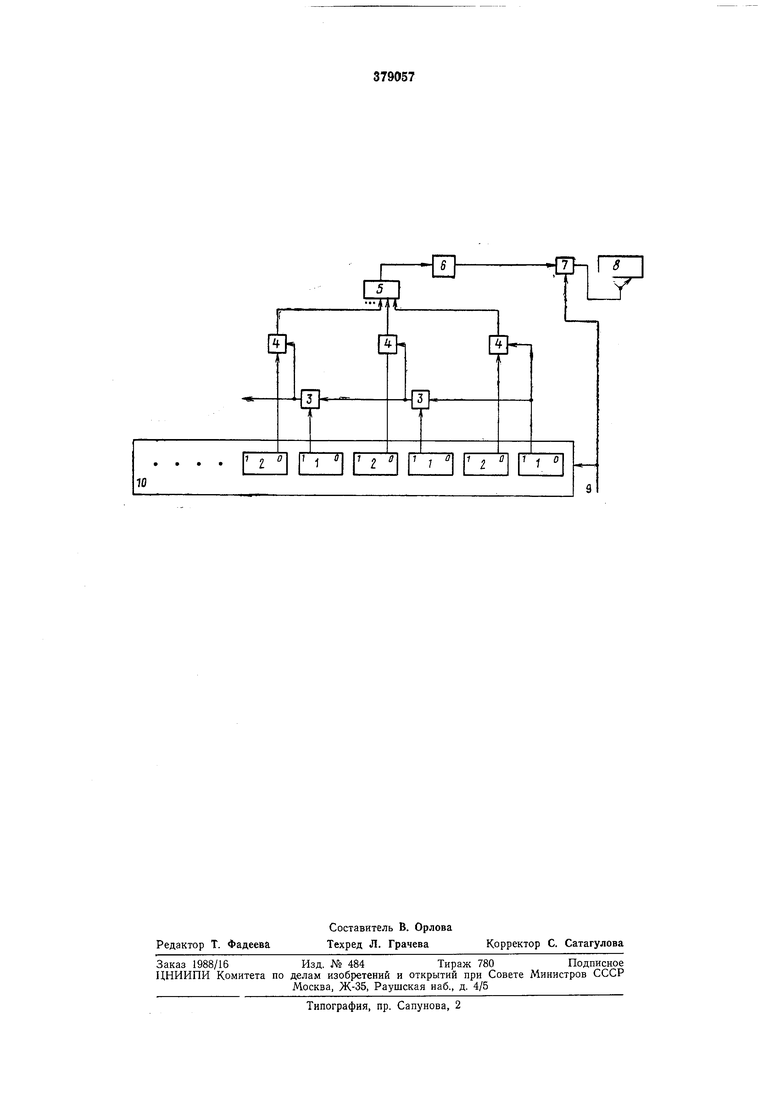

На чертеже изображена схема предлагаемого устройства.

Оно содержит триггеры 1 нечетных разрядов счетчика, триггеры 2 четных разрядов счетчика, схемы «И 3 нечетных разрядов, схемы «И 4 четных разрядов, схему «ИЛИ 5, схему «НЕ 6, управляющую схему «И 7, триггер 8 контрольного разряда, шину 9 подачи импульсов счета и счетчик 10.

Единичные выходы триггеров 1, кроме триггера первого разряда, соединены с входами схем «И 3, другие входы которых, кроме схемы «И 3 третьего разряда, связаны с выходом предыдущей схемы «И 3, другой вход

схемы «И 3 третьего разряда - с единичным выходом триггера первого разряда. Нулевые выходы триггеров 2 соединены с входами схем «И 4, другие входы которых, кроме схемы «И 4 второго разряда, подключены к

выходу схемы «И 3 триггера предыдущего нечетного разряда, другой вход схемы «И 4 второго разряда связан с единичным выходом триггера первого разряда. Входы схемы «ИЛИ 5 соединены с выходами схем «И 4,

а ее выход через схему «НЕ 6 - с входом схемы «И 7, другой вход которой связан с щиной импульсов счета. Выход управляющей схемы «И 7 соединен со счетным входом триггера 8 контрольного разряда.

В исходном состоянии значение контрольного разряда устанавливается таким, чтобы

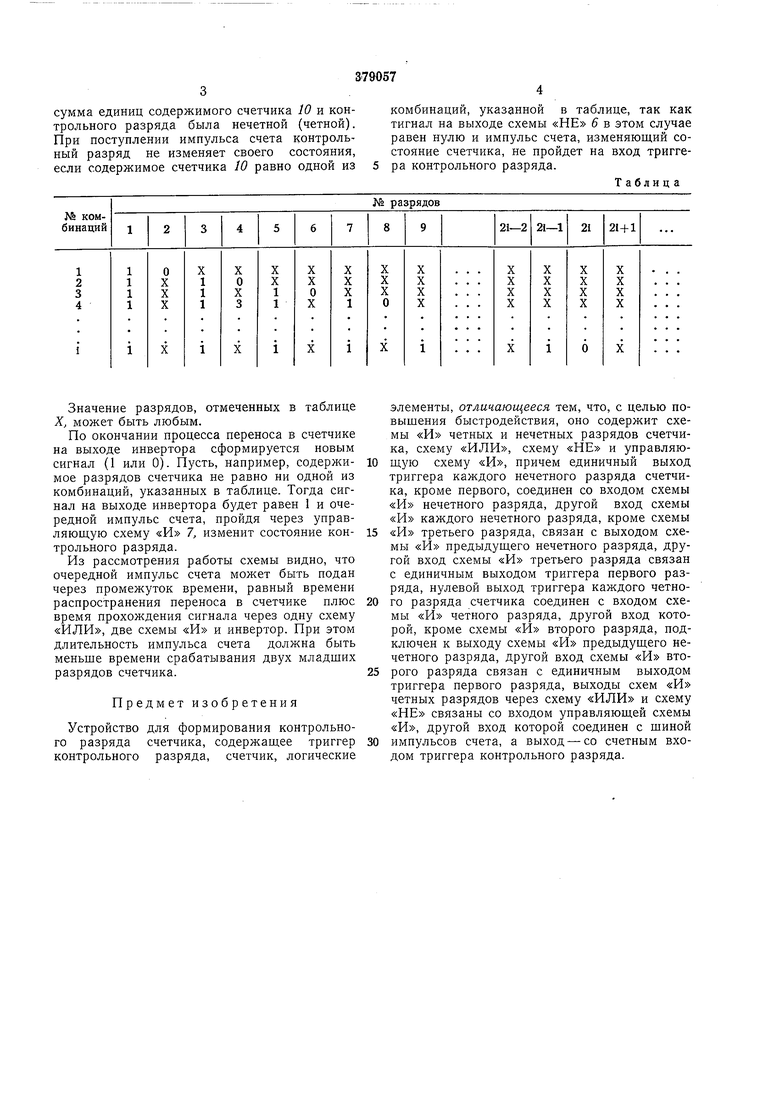

сумма единиц содержимого счетчика 10 и контрольного разряда была нечетной (четной). При поступлении импульса счета контрольный разряд не изменяет своего состояния, если содержимое счетчика 10 равно одной из

комбинаций, указанной в таблице, так как тигнал на выходе схемы «НЕ 6 в этом случае равен нулю и импульс счета, изменяющий состояние счетчика, не пройдет на вход триггера контрольного разряда.

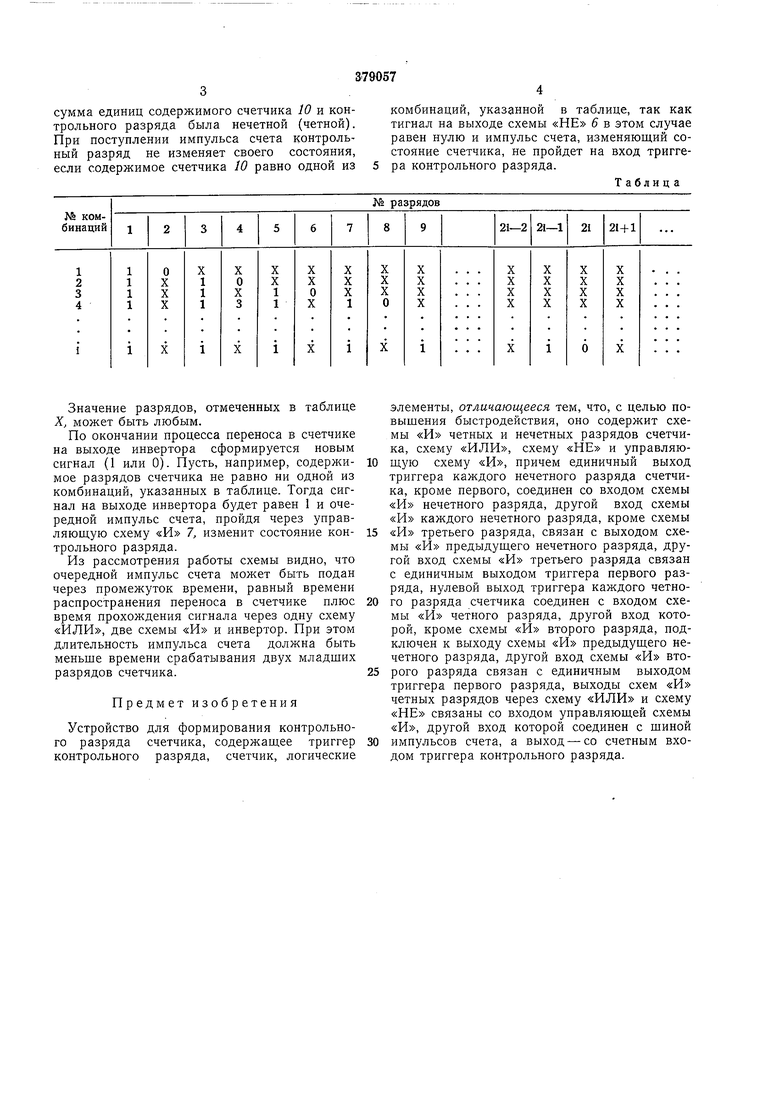

Таблица

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВОИЧНЫЙ СЧЕТЧИК ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ | 1969 |

|

SU249793A1 |

| Устройство для контроля параллельного кода на четность | 1987 |

|

SU1413632A1 |

| УСТРОЙСТВО для ИНТЕГРИРОВАНИЯ ФУНКЦИЙ в ДВОИЧНО-ДЕСЯТИЧНОМ ЦИКЛИЧЕСКОМ КОДЕ | 1967 |

|

SU203321A1 |

| Устройство формирования контрольного разряда счетчика | 1982 |

|

SU1027828A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Уравновешивающая схема для аналогоцифрового преобразователя поразрядного уравновешивания | 1972 |

|

SU444319A1 |

| Устройство для управления реконфигурацией резервированной вычислительной системы | 1991 |

|

SU1837296A1 |

| Устройство для управления шаговым двигателем с дроблением шага | 1981 |

|

SU964951A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1536388A1 |

| Устройство для тренировки памяти обучаемого | 1989 |

|

SU1683050A1 |

Значение разрядов, отмеченных в таблице X, может быть любым.

По окончании процесса переноса в счетчике на выходе инвертора сформируется новым сигнал (1 или 0). Пусть, например, содержимое разрядов счетчика не равно ни одной из комбинаций, указанных в таблице. Тогда сигнал на выходе инвертора будет равен 1 и очередной импульс счета, пройдя через управляющую схему «И 7, изменит состояние контрольного разряда.

Из рассмотрения работы схемы видно, что очередной импульс счета может быть подан через промежуток времени, равный времени распространения переноса в счетчике плюс время прохождения сигнала через одну схему «ИЛИ, две схемы «И и инвертор. При этом длительность импульса счета должна быть меньще времени срабатывания двух младщих разрядов счетчика.

Предмет изобретения

Устройство для формирования контрольного разряда счетчика, содержащее триггер контрольного разряда, счетчик, логические

элементы, отличающееся тем, что, с целью повышения быстродействия, оно содержит схемы «И четных и нечетных разрядов счетчика, схему «ИЛИ, схему «НЕ и управляющую схему «И, причем единичный выход триггера каждого нечетного разряда счетчика, кроме первого, соединен со входом схемы «И нечетного разряда, другой вход схемы «И каждого нечетного разряда, кроме схемы «И третьего разряда, связан с выходом схемы «И предыдущего нечетного разряда, другой вход схемы «И третьего разряда связан с единичным выходом триггера первого разряда, нулевой выход триггера каждого четного разряда счетчика соединен с входом схемы «И четного разряда, другой вход которой, кроме схемы «И второго разряда, подключен к выходу схемы «И предыдущего нечетного разряда, другой вход схемы «И второго разряда связан с единичным выходом триггера первого разряда, выходы схем «И четных разрядов через схему «ИЛИ и схему «НЕ связаны со входом управляющей схемы «И, другой вход которой соединен с щиной импульсов счета, а выход - со счетным входом триггера контрольного разряда.

Авторы

Даты

1973-01-01—Публикация