1

Изобретение относится к цифровым отсчетным устройствам,

Известны цифровые отсчетные устройства, содержащие позиционный кодовый датчик, выход которого непосредственно, а вход через источник импульсов опроса лОдключенЫ к схемам ввода и записи; сумматор, входы которого через весо-вой преобразователь подключены к. схеме ввода, а выходы соединены со входами блока регистрации результата, н логический блок управления с кнопкой записи, кнопками режимов работы сумматора, схемой начальной установки, триггерами управления, схемой «ИЛИ, схемой разрешения тактовых импульсов, схемами выделения конДОН первой и второй пачек импульсов, схемами получения обратного и дополнительного кодов и схемой обращения.

В известных устройствах начало отсчета связано с нулевым положением позиционного датчика.

Предлагаемое устройство отличается от известных тем, что оно содержит схему разрешения записи, схему опроса, распределитель тактов н блок памяти, выход которого соединеп со входом весового преобразователя, а входы подключены к выходу схемы начальной установки, к выходу схемы опроса и к выходу схемы записи, присоединенной одним из входов к выходу схемы разрешения записи;

2

входы схемы разрешения записи соединены с кнопкой записи логического блока управления и с выходом схемы выделения конца второй пачки импульсов; входы схемы опроса подключены к выходу распределителя тактов, к нулевому выходу первого триггера управления и к кнопке режимов работы сумматора, соединенной с первым запрещающими входами схем получения обратного и дополнительного кодов и схемы обращения; вторые запрещающие входы схемы обращения и схемы получения дополнительного кода подключены через кнопки режимов работы сумматора к одному из входов устройства; резрешающие входы схем нолучения обратного и Дополнительного кодов и разрешающий вход схемы обращения coe.uiiienbi соответственно с выходами схем выделения концов первой и второй пачек импульсов; выход схемы получения дополнительного кода непосредственно, а выходы схем обращения и нолучения обратного кода через схему «ИЛИ нодключены к входам су.мматора.

Это позволяет упростить отсчет измеряемых величин от нронзвольно выбранного начального отклонения кодового датчика.

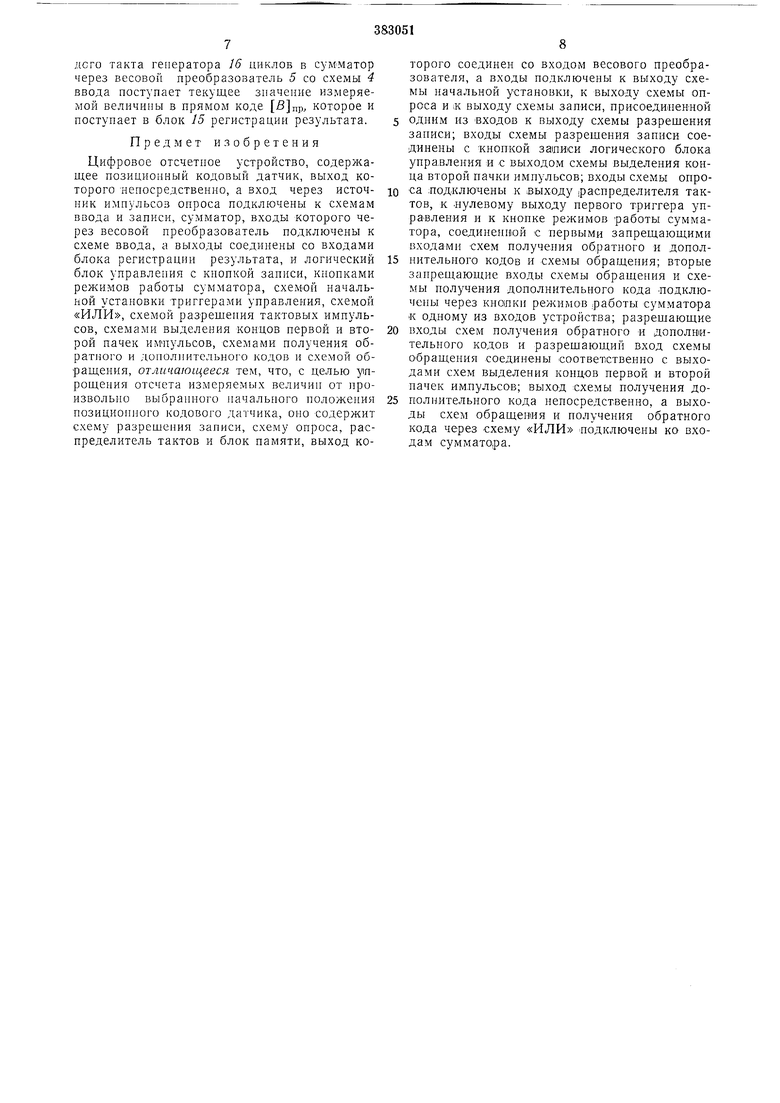

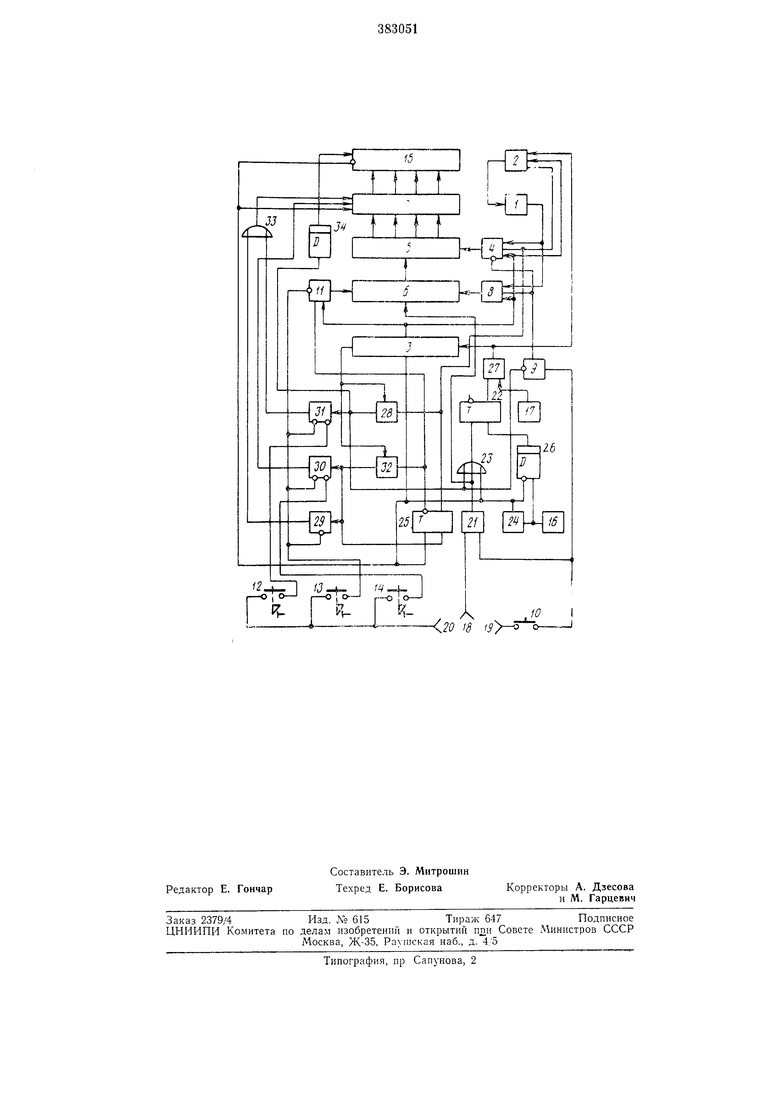

На чертеже изображена схема устройства.

Устройство состоит из позиционного кодового датчика 7, источника 2 импульсов опроса позиционного кодового датчика, формирующего на выходе при наличии подготовок на входах по тактам с выхода распределителя S тактов импульсы поразрядного опроса позиционного кодового датчика; схемы ввода 4, весового преобразователя 5, осуществляющего поразрядное преобразование двоичного кода измеряемой величины, поступающего с позиционного кодового датчика / или с выхода блока памяти 6, в параллельный двоичный код и ввод этого параллельного двоичного кода в соответствующие разряды сумматора 7. Разрядность этого сумматора определяется пределами измерения и точностью воспроизведения измеряемой величины.

В cyMiMaTOpe 7 вычисляется абсолютное значение разности между текущим значением измеряемой величины, снятым с позиционного кодового датчика /, и значением, считанным с блока памяти 6, где хранится код измеряемой величины, снятой с позиционного кодового датчика в момент получения произвольного начала отсчета. Запись кода в блок памяти 6 осуществляется через схему 8 записи, подготавливаемую схемой 9 разрещения записи, которая запускается на времЯ одного цикла кнопкой записи 10, по тактам с распределителя 3 тактов, а опрос запоминающего устройства без разрушения хранимой инфор.лшции производится схемой 11 опроса во время каждого последующего цикла опроса при соответствующих подготовках па входе схемы 11 опроса.

В устройстве при определении абсолютной разности двух значений измеряемой величины

С ,

где С-абсолютное значение разности;

В - текущее значение измеряемой величины (уменьщаемое); А - значение измеряемой величины, записапное в запоминающем устройстве (вычитаемое),

В зависимости от значений А и Б используется режим работы сумматора 7 в дололнительиом, так и в обратном коде.

При В в сумматоре 7 вычисляется сумма в дополнительном коде:

121доп ,

где - значение суммы ,в допол:нительном коде;

- дополнительный код вычитаемого; - прямой код уменьщаемого.

Абсолютное значение разности в этом случае получается непосредственно после получения суммы в дополнительном коде, т. е.

С-Идоп,

При Л В в сумматоре 7 вычисляется сумма в обратном .коде

-обрат - JoapaT г

где 2 обрат - значение суммы в обратном

коде;

/1 обрат - обратный код вычитаемого; - прямой код уменьшаемого.

у бсолютпое значение разности в этом случае получается после обраще11ия обратного кода полученной суммы, т. е.

- ( обрат о6ращ

где (2 обрат)оиращ -обращенное значение

суммы, получепное в обратном коде. В точке произвольно выбранного начала отсчета Л Z3 и при дпух указанных режимах работы сумматора 7 будет получено пулевое значение разности.

При Л О начало отсчета совпадает с пулевым положением познционного кодового

датчика и в сумматоре 7 будет записано текущее значение измеряемо) величины.

Переключение режимов работы сумматора 7 осуществляется кнопками 12, 13 и 14 с зависимой фиксацией. При включенной кнопке

12 в сумматоре 7 вычисляется абсолютное значение разности в дополнительном коде, при включенной кнопке 14 - в обратном коде, а при включенной кнопке 13 в сумматоре 7 будет записано текущее значение измеряемой

величины.

Следует указать, что при несоответствии действительного соотношения между Л и В выбранному включенной кнопкой 12 или 14, в сумматоре 7 будет получено не значение

абсолютной разности, а ее дополнение до полной емкости сумматора 7.

Значение абсолютной разности после окончания работы сумматора 7 выводится в блок 15 регистрации результата, в качестве коториго могут быть индикаторные лампы, цифропечатаюцдее устройство, телетайп, устройство

ввода в вычислительную машину, устройство

вывода на различного рода пакопнтели и т. д,

Работа всего устройства задается тактами

генератора 16 циклов, генератора 17 тактов и логической схемой управления.

Иа вход 18 подается сигнал включения питающих напряжений, но входу 19 поступает потенциал разрещения, а по входу 20 - потепциал запрета.

Устройство работает следующим образом. При включении устройства в сеть по входу 18 сигналом включения питающих напряжений запускается схема 21 начальпой установкк, импульсом с выхода которой производится установка в «О блока памяти 6 и триггера управления 22 через схему 23 «ИЛИ.

При включении кнонки записи W запускается схе.ма 2} начальной установки и схема 9

разрещепия записи. При этом на время ближайшего такта генератора 16 циклов разрешена запись в блок памяти 6 через схему 8 записи текущего значения измеряемой величины, поступающей с познционного кодового

датч1 ка 1, и запрещена схема ввода 4.

Началом такта генератора 16 циклов запускается схема 24 установки «О, сигналом с выхода которой устанавливается в «О распределитель 3 тактов, триггер управления 25, сумматор 7, запрещается работа блока 15 регистрации результата, через схему 23 «ИЛИ подтверждается нулевое состояние триггера правления 22.

Импульсом со схемы 26 задержки иа время установки «О устанавливается в «1 триггер управления 22, нодготавливая схему 27 разрешения тактовых импульсов. Тактовые импульсы 1енератора 17 тактов через схему 27 разрешения тактовых импульсов начинают поступать па распределитель 3 тактов.

Запись текундего значения измеряемой величины в блок памяти 6 производится поразрядно через схему 8 записи при соответствующих тактах распределителя 3 тактов во время второй пачки тактовых импульсов.

Импульсом со схемы 28 выделения конца второй пачки тактовых импульсов снимается подготовка со схемы 9 разрешения заниси до с.1едующего включения кнопки 10. Этим же импульсом устанавливается в «О через схему 23 «ИЛИ триггер управления 22, снимая подютовку со схемы 27 разрешения тактовых имп,льсов.

При включенной кнопке 12 разрешены схемы 29 получения обратного кода, схема 30 получения дополнительного кода и занпещена схема 31 обращения. Началом каждого такта генератора 16 циклов, начиная со второго, т. е. после записн текущего значения измеряемой величины иа момепт получения пронзвольио выбранного начала отсчета в блок намяти 6, запускается 2т установки «О и схема 26 задержки на время установки «О.

Импульсом со схемы 26 задержки на время установки «О устанавливается в «1 триггер управления 22, подготавливая схему 27 разрешения тактовых импульсов, и тактовые импульсы генератора 17 тактов подаются иа распределитель 3 тактов.

Ири выбранных тактах первой пачки тактовых импульсов на выходе распределителя 3 тактов через подготовленную первым триггером управления 25 схему )/ опроса производится поразрядный опрос без разрушения хранимой информации запомииающего устройства 6 и запись считанного прямого кода через весовой преобразователь 5 в сумматор 7. И.мпульсом со схемы 32 выделе1;ня конца первой пачки тактовых импульсов залускается схема 29 получения обратного Ko;ia, сигналами с выхода которой через .схему 33 ИЛИ прямой код .4,-гг„ записаиньи в сумматоре 7, переводится в обратный |.4,,, схема 30 получения дополнительного кода. сигналом: с выхода которой обратный код вычитаемого Л обрат переводится в дополнительный . Кроме того, имнульсом го схемы 32 выделения конца цервой пачки тактовых импульсов устанавливается в «1 триггер управления 25, под.готавлцвая .схему 4 ввода, схему 28 выделения конца второй пачки тактовых импульсов н источник 2 импульсов опроса позпнноииого датчнка.

Во время второй пачки тактовых импульсов при выбранных тактах поразрядно в сумматор 7 через весовой преобразователь 5 со схемы 4 ввода прпбавляется прямой код . поступаюндий с позиционного кодового датчика /. После сложения в сумматоре 7 будет получена сумлш

1-1лоп Ь l-ojnpi

которая равна абсолютной разности С. Имнульсом со схемы 28 выделе.щя конца второй

пачки тактовых импульсов запускается схема 34 задержки па время возможного обрангения при другом режиме работы сумматора 7 п через схему 23 «ИЛИ устанавливается в «О триггер управлення 22, сннмая подготовку со

схемы 27 разрешения тактовых импульсов.

Импульсом со схемы 34 задержки на время обращения разрешается работа блока 15 регнстрац1:и результата до конца такта reisepaтора 16 циклов. С началом следуюн1,его такта

генератора 16 циклов последовательность работы устройства повторяется.

При включенной кнопке 14 запрещена схема 30 получения дополнительного кода, .разрешены схема 29 получения обратного кода п

схе.ма 31 обращения.

Прн опросе блока памяти 6 схема работает аналогично. После записи прямого кода вычитаемого через весовой преобразователь 5 в сумматор 7 пмпульсом со схемы 32

выделення конца нервой пачки тактовых импульсов запускается схема 29 получения обрйтного кода, сигналами с KOTOpoii через схему 33 «ИЛИ пря.мой код вычитаемого Л,,,,, записан1 ый в сумматоре 7, переводится в обратный Л обрат.

Во время второй пачки тактовых импульсов в сумматоре 7 будет получена сумма в обратном коде

|-1обрат 1Л обрат +

Как уже указывалось, для получения значеппя абсолютной разности в этом случае требуется операция обращения по,тучепной суммы. Поэтому импульсом со схемы 28 выделення конца BTOpoii пачки тактовых пмпульсов зацускается схема 5/ обраицм.ия, С1;гналамн с которой через схему 33 «ИЛИ производится обращение кода , полученной в сумматоре 7.

После обрангсния пмпульсом со схемы 34 задержки на Г)ремя работы схемы 31 обранСпмя разгешается до KOinia )го такта ге ;ератора 16 циклов работа блока рсгнстрацин результата.

Ппн включенной кнопке 13 занрен,ена схеv.-л 11 опроса, схема 30 получения дополпительного кода, схема 29 получения обратного кода, схема 31 обрашения.

По тактам второй пачкн тактовых импульсов с распределителя 3 тактов во время каждсго такта генератора 16 циклов в сум матор через весовой преобразователь 5 со схемы 4 ввода поступает текущее значение измеряемой величины в прямом коде , которое и поступает в блок 15 регистрации результата.

Предмет изобретения

Цифровое отсчетпое устройство, содержащее позиционный кодовый датчик, выход которого непосредственно, а вход через источник импульсов опроса подключены к схемам ввода и записи, сумматор, входы которого через весовой преобразователь подключены к схеме ввода, а выходы соединены со входами блока регистрации результата, и логический блок управления с кнопкой записи, кнопками режимов работы сумматора, схемой начальной установки триггерами управления, схемой «ИЛИ, схемой разрешения тактовых импульсов, схемами выделения концов первой и второй пачек импульсов, схемами получения обратного и дополнительного кодов и схемой обращения, отличающееся тем, что, с целью упрощения отсчета измеряемых величин от произвольно выбранного начального положения позиционного кодового датчика, оно содержит схему разрешения записи, схему опроса, распределитель тактов и блок памяти, выход которого соединен со входом весового преобразователя, а входы подключены к выходу схемы начальной установки, к выходу схемы опроса и iK выходу схемы записи, присоединенной одним из ВХОД01В к выходу схемы разрешения записи; входы схемы разрешения записи соединены с кнопкой записи логического блока управления и с выходом схемы выделения конца второй пачки импульсов; входы схемы опроса лод-ключены к :Быходу |распределителя тактов, к -пулевому выходу первого триггера упра-вления и к кнопке режимов работы сумматора, соединенной с первыми запрещающими входами схем получения обратного и дополнительного кодов и схемы обращения; вторые запрещающие входы схемы обращепия и схемы получения дополнительного кода лодключены через кноики режимов .работы сумматора « одному из входов устройства; разрешающие

входы схем получения обратного и дополнительного кодов и разрещающий вход схемы обращения соединены соответственно с выходами схем выделения концов нервой и второй начек имлульсов; выход схемы получения дополнительного кода непосредственно, а выходы схем обращевия и получения обратного кода через схему «ИЛИ подключены ко входам сумматора.

2 4 W-Ь -4f-oT&-J ...-. I fc j R- I t

/ ./g

/,9 o

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЦВМ и накопителя информации | 1985 |

|

SU1265780A1 |

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

| УСТРОЙСТВО для ТЕЛЕИЗМЕРЕНИЯ | 1972 |

|

SU337799A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| СПОСОБ СЛЕЖЕНИЯ ЗА ПЕРЕМЕЩЕНИЕМ ПРОТЯЖЕННОГО ОБЪЕКТА | 1992 |

|

RU2078352C1 |

| АНАЛИЗАТОР ДЛЯ ОПРЕДЕЛЕНИЯ УСТОЙЧИВОСТИ ФАЗИРУЮЩИХ УСТРОЙСТВ С ДИСКРЕТНЫМ УПРАВЛЕНИЕМ | 1968 |

|

SU211151A1 |

| Устройство мажоритарного декодирования | 1985 |

|

SU1249708A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1987 |

|

SU1462492A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Способ измерения частоты следования импульсов | 1988 |

|

SU1594483A1 |

Даты

1973-01-01—Публикация