1

Изобретение относится к вычнслительной технике.

Известна схема формирования стробирующих импульсов для магнитных запоминающих устройств (ЗУ), в которой для формирования стробирующего сигнала используется импульс со стробируюп1,его разряда накопителя информации, образованного двумя дифференниально включеиными элементами памяти. В одном из указанных элементов записана «1, во втором - «О. Сигнал, снимаемый со стробирующего разряда, представляет собой результат амплитудного суммирования полезного сигнала и «помехи. Этот сигнал непосредственно подается на вход усилителя считывания для стробирования и способствует устойчиво1му выделению нолезиого си-гпала на фоне «номех, обусловленных неидеальностью характеристик элементов памяти магнитного накопителя информации.

Однако в магнитных ЗУ действуют номехн, являющиеся следствием таких факторов, как паразитные емкости монтажа, индуктивность проводов и др. Эти факторы зависят от конструкции накопителя, характеристик отдельных компонентов ЗУ и характера переходных процессов в нем при заниси и считывания информации. Такие помехи носят, как правило, характер затухаюи;его колебательного процесса, имеют зиачительную амплутуду (соизмеримую с сигналом «1) и по времени своего затухания могут превзо1 1ти длительность импульса «1.

Цель изобретення - повысить надежность работы нредлагаемой схемы в щироком температурном- диапазоне.

Это достигается введением логической цоночки, содержащей схему «НЕ и схему «11, причем выход «О элементов стробнрующего

разряда соединен со входом схемы «ИЕ, выход которой подключен на нервый вход схемы «И. Второй вход последней соединен с выходом «1 стробирующего разряда, а выход схемы «И подключен ко входу «запрета

усилителя считывания.

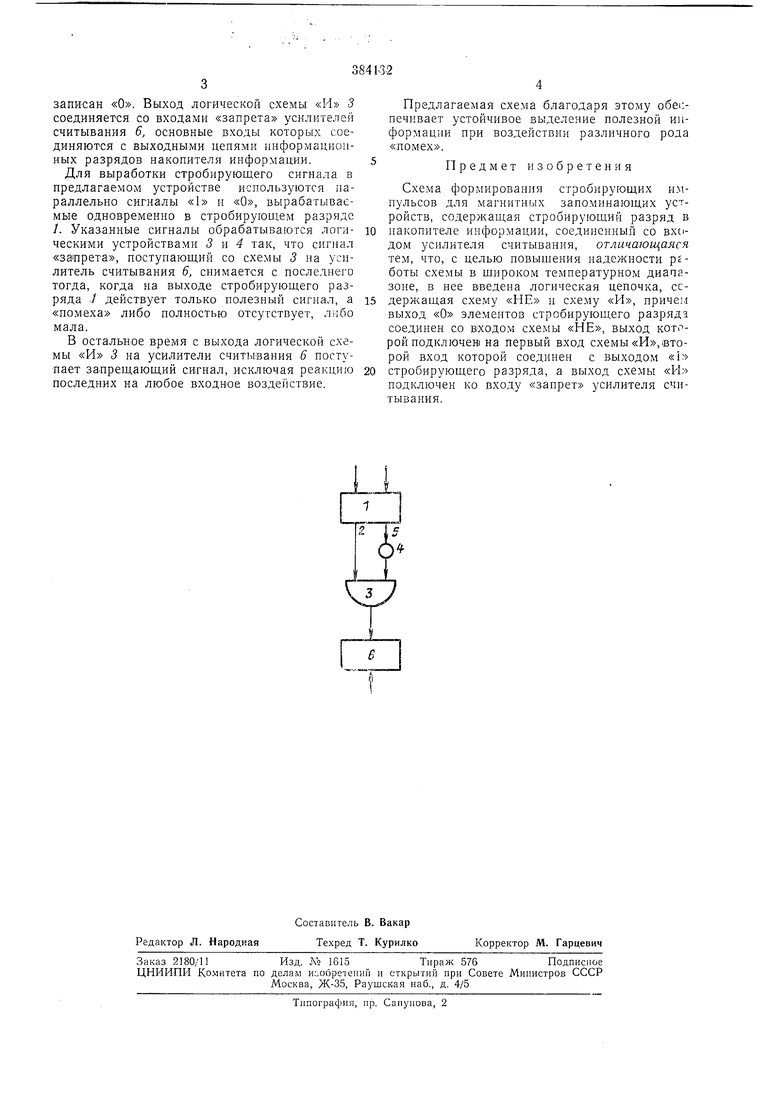

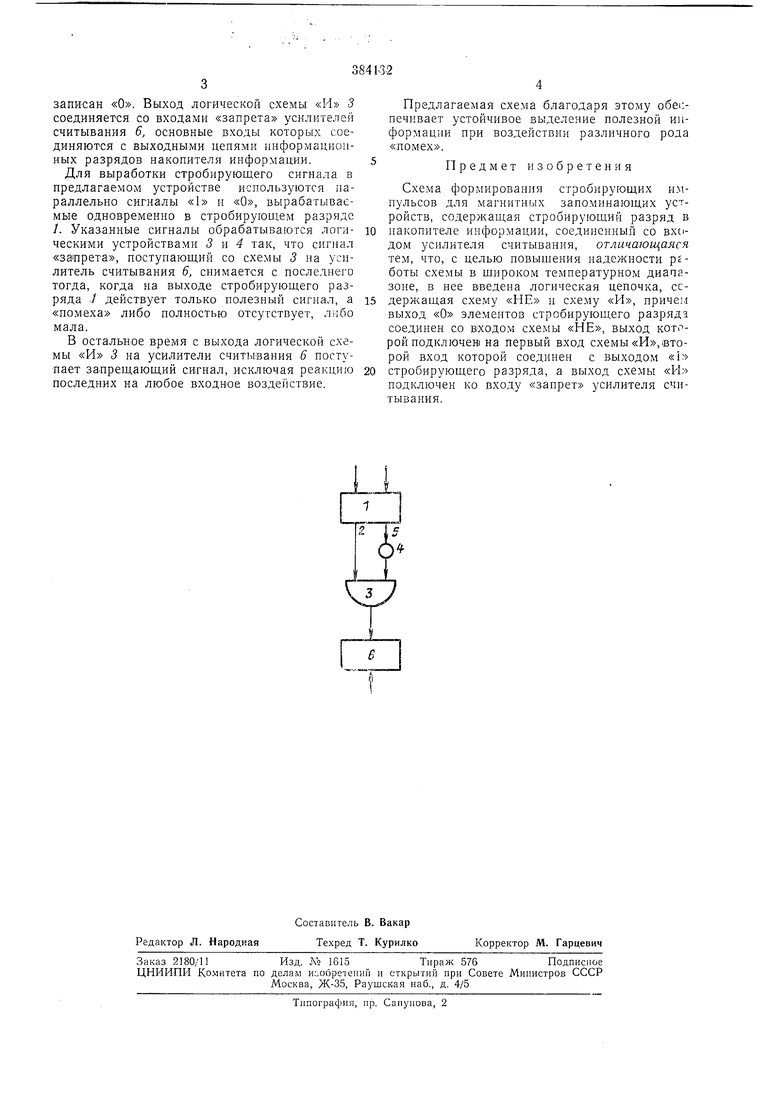

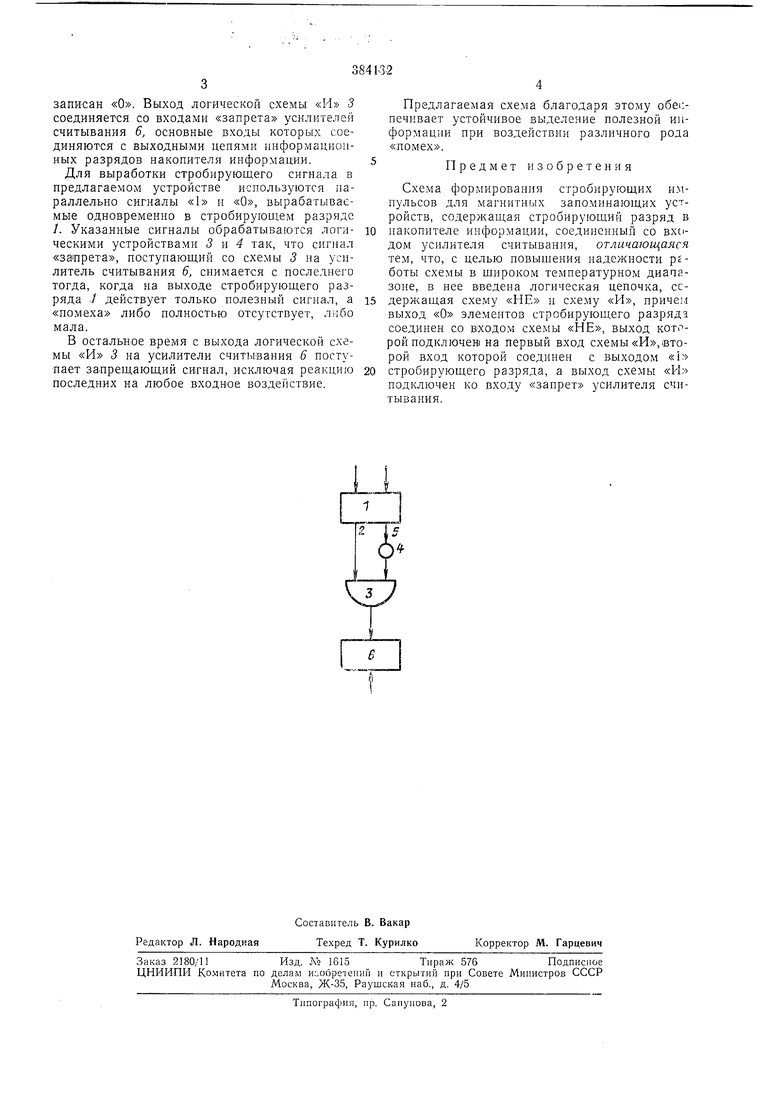

На чертеже представлена предлагаемая схема. Она содержит специальный стробирующий разряд /, входящий в магнитный наконитель информации и образованный парой элементов памяти, «запись информации в когэрые производится ио дифференциально включенной обмотке. «Онрос элементов стробирующего разряда происходит одновременно с информациониыми. Выходная обмотка элемента стробирующего «разряда, в котором занисана «1, по шине 2 подключается к одному входу логической схемы «И 3. Второй вход последней через логическую схему «НЕ 4 НО щине 5 соедиияется с выходом второго

элемента стробнрующего разряда, в которо.м

записан «О. Выход логической схемы «И 3 соединяется со входами «запрета усилителей считывания 6, основные входы которых соединяются с выходными цепями информационных разрядов накопителя информации.

Для выработки стробирующего сигнала в предлагаемом устройстве используются параллельно сигналы «1 и «О, вырабатываемые одновременно в стробирующем разряде /. Указанные сигналы обрабатываЕОтся логическими устройствами 3 и 4 так, что сигнал «запрета, поступающий со схемы 3 на усилитель считывания 6, снимается с последнего тогда, когда на выходе стробирующего разряда ./ действует только полезный сигнал, а «помеха либо полностью отсутствует, либо мала.

В остальное время с выхода логической схемы «И 3 на усилители считывания 6 постунает запрещающий сигнал, исключая реакцию последних на любое входное воздействие.

Предлагаемая схема благодаря этому o6ei;печнвает устойчивое выделение полезной информации при воздействии различного рода «помех.

Предмет изобретения

Схема формирования стробирующих нмпульсов для магнитнг 1х запоминающих устройств, содержащая стробирующий разряд в накопителе информации, соединенный со Bxciдом усилителя считывания, отличающаяся тем, что, с целью повышения надежности ргботы схемы в широком температурном диапазоне, в нее введена логическая цепочка, ссдержащая схему «НЕ и схему «И, причем выход «О элементов стробирующего разряда соединен со входом схемы «НЕ, выход которой подключен на первый вход схемы «И, второй вход которой соединен с выходом «Ь стробирующего разряда, а выход схемы «И подключен ко входу «запрет усилителя считывания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1980 |

|

SU934554A1 |

| Логическое запоминающее устройство | 1972 |

|

SU442512A1 |

| Запоминающее устройство | 1974 |

|

SU487417A1 |

| УСТРОЙСТВО для ВРЕМЕННОЙ СЕЛЕКЦИИ | 1970 |

|

SU275128A1 |

| Устройство для записи и считывания информации в трансформаторных накопителях | 1980 |

|

SU942138A1 |

| Запоминающее устройство с резервированием | 1986 |

|

SU1417042A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ТИПА ЗД | 1971 |

|

SU427380A1 |

| Запоминающее устройство | 1979 |

|

SU809350A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1795521A1 |

Авторы

Даты

1973-01-01—Публикация