il

Изобретение относится к вычислительной технике.

Известно ЗУ, содержащее накопитель, выходы которого соединены со входами усилителей воспроизведения, выходы которых подключены через усилители стробирования к первым входам регистра числа, вторые входы которого соединены с одними из выходов блока управления. Другие выходы блока управления соединены со входами дешифратора адреса, выходы которого соединены с первыми входами логических элементов «И, а их выходы через формирователи импульсов записи и считывания соединены со входами накопителя.

Принцип действия устройства основан на ограничении импульсов опроса (записи) после окончания перемагничивания запоминающих элементов, которое определяется по нарастанию тока опроса (записи) после окончания процесса перемагничивания.

Однако такое устройство не может быть использовано при построении устройств, в которых нагрузка на формирователи токов считывания и записи зависит от хранящейся и записываемой информации (например, ЗУ, работающие по принципу совпадения полутоков систем ЗД, 2,БД, 2Д, с одним сердечником на разряд), так как в зависимости от информации меняется момент ограничения импульсов считывания и записи, в результате чего некоторые запоминающие элементы могут оказаться ненереключенными. Кроме того, по нарастанию тока момент

окончания перемагничивания не может быть точно определен, что ограничивает быстродействие ЗУ.

Целью изобретения является повыщение быстродействия ЗУ и расщирение области их

применения.

Эта цель достигается тем, что ЗУ содержит триггер, дополнительный усилитель воспроизведения, вход которого соединен с выходом накопителя, выход подключен к одному

из входов триггера, другой вход которого соединен с третьим выходом блока управления, а выход триггера соединен с другими входами логических элементов «И.

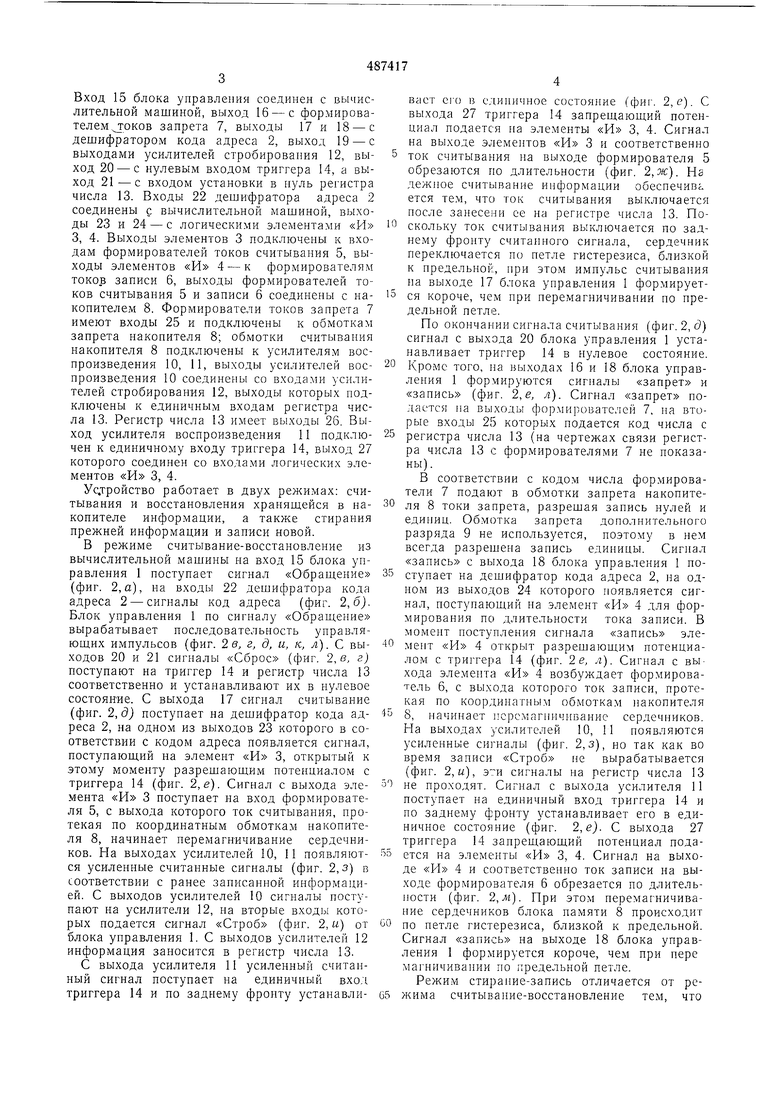

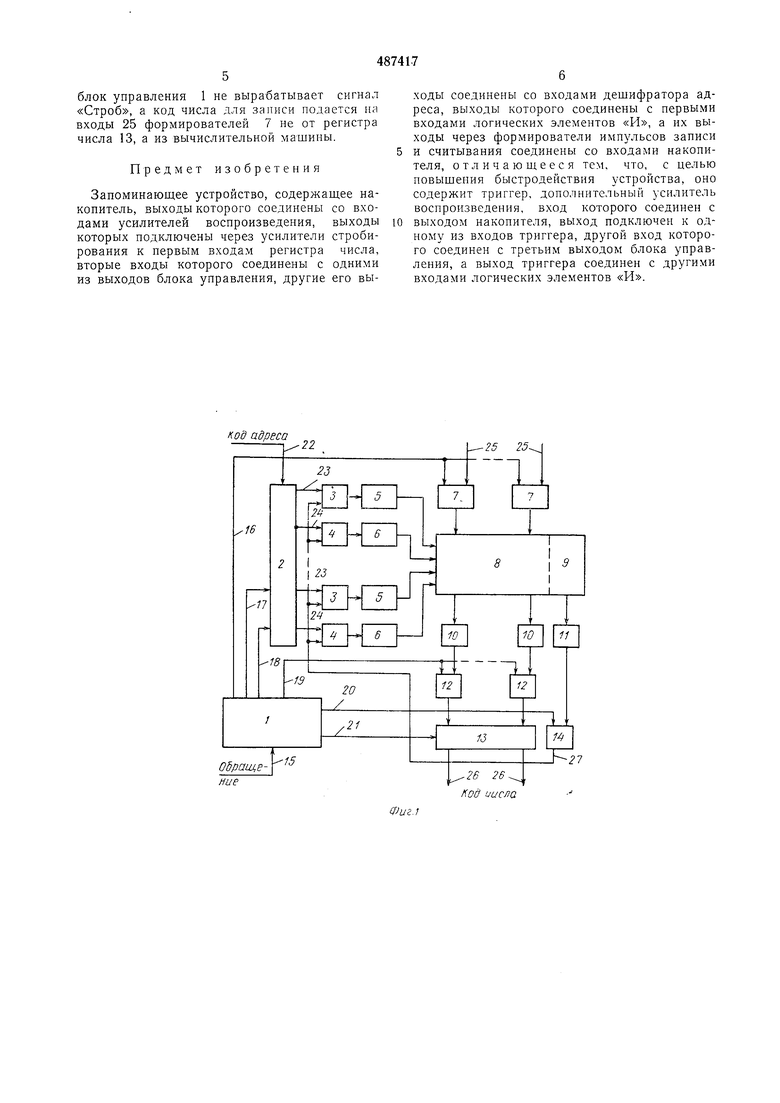

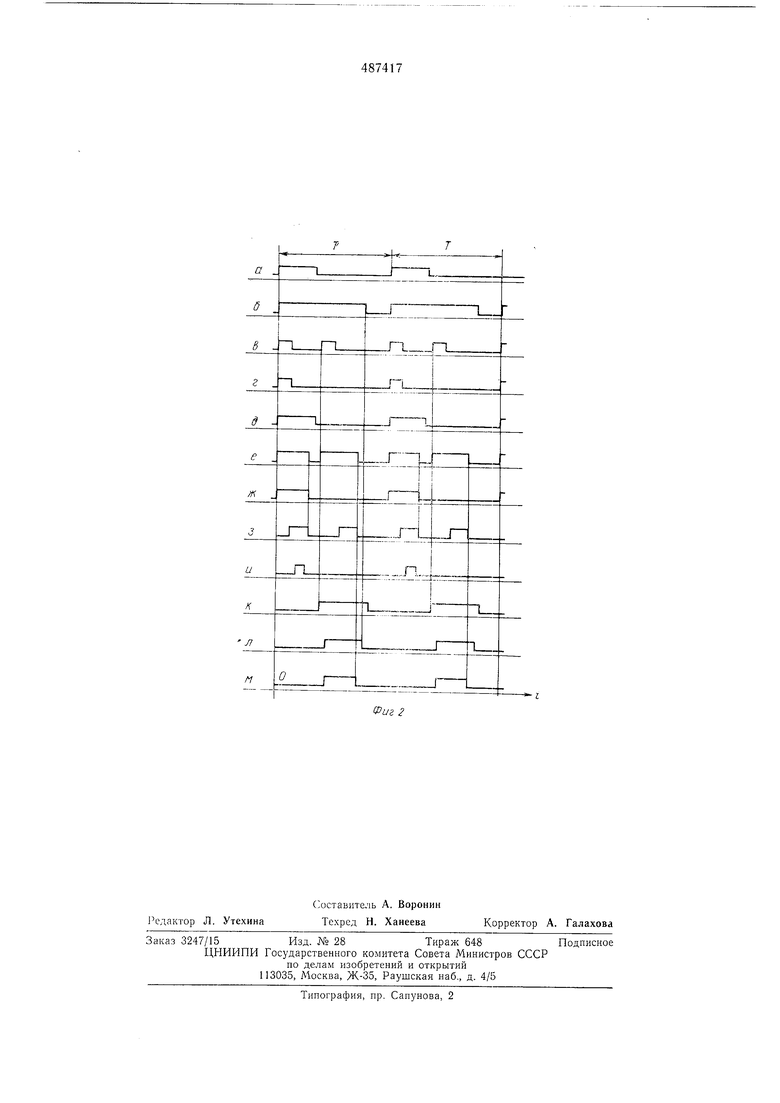

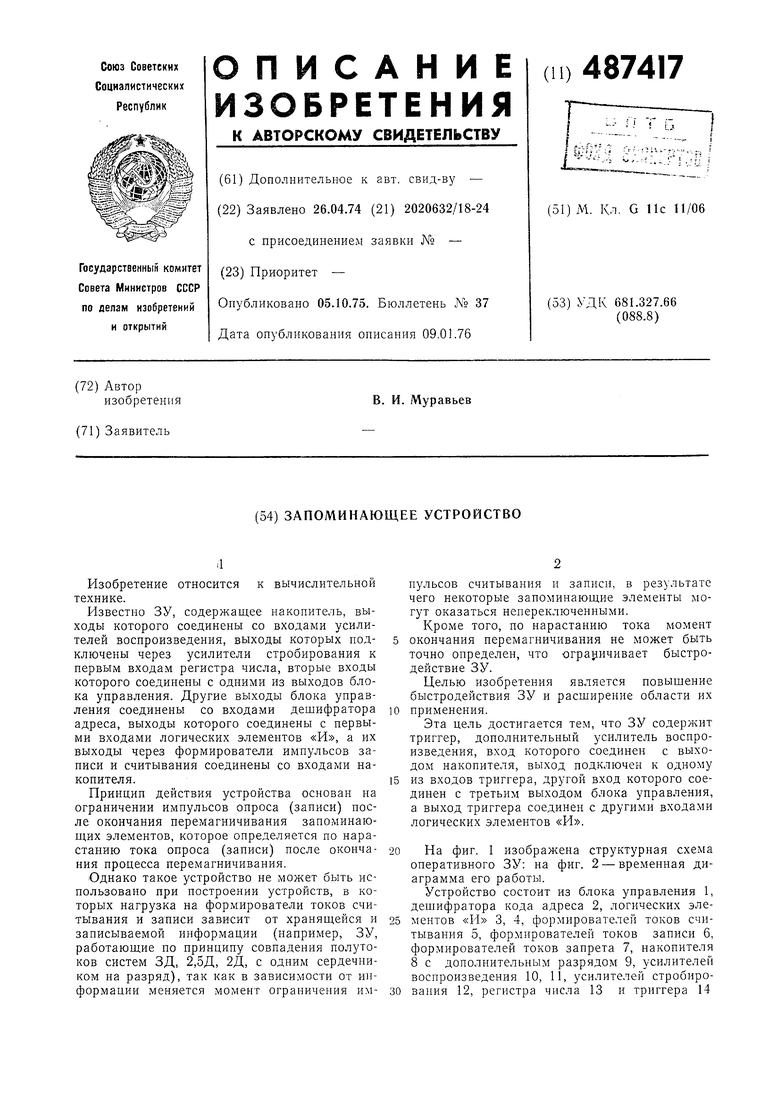

На фиг. 1 изображена структурная схема оперативного ЗУ: на фиг. 2 - временная диаграмма его работы.

Устройство состоит из блока управления 1, дешифратора кода адреса 2, логических элементов «И 3, 4, формирователей токов считывания 5, формирователей токов записи 6, формирователей токов запрета 7, накопителя 8 с дополнительным разрядом 9, усилителей воспроизведения 10, 11, усилителей стробирования 12, регистра числа 13 и триггера 14

Вход 15 блока управления соединен с вычислительной машиной, выход 16 - с формирователем .гоков запрета 7, выходы 17 и 18 - с дешифратором кода адреса 2, выход 19 - с выходами усилителей стробировапия 12, выход 20 - с нулевым входом триггера 14, а выход 21 - с входом установки в нуль регистра числа 13. Входы 22 дешифратора адреса 2 соединены с вычислительной машиной, выходы 23 и 24 - с логическими элементами «И 3, 4. Выходы элементов 3 подключены к входам формирователей токов считывания 5, выходы элементов «И 4 - к формирователям токов записи 6, выходы формирователей токов считывания 5 и заниси 6 соединены с наконителем 8. Формирователи токов запрета 7 имеют входы 25 и подключены к обмоткам запрета накопителя 8; обмотки считывания накопителя 8 подключены к усилителям воспроизведения 10, 11, выходы усилителей воспроизведения 10 соединены со входами усилителей стробирования 12, выходы которых подключены к единичным входам регистра числа 13. Регистр чнсла 13 имеет выходы 26. Выход усилителя воспроизведения 11 подключен к единичному входу триггера 14, выход 27 которого соединен со входами логических элементов «И 3, 4.

Устройство работает в двух режимах: считывания и восстановления храняш,ейся в накопителе информации, а также стирания прежней информации и записи новой.

В режиме считывание-восстановление из вычислительной машины на вход 15 блока управления 1 поступает сигнал «Обращение (фиг. 2, а), на входы 22 дешифратора кода адреса 2 - сигналы код адреса (фиг. 2,6). Блок управления 1 по сигналу «Обраш,епие вырабатывает последовательность управляюшнх импульсов (фиг. 2 в, г, д, и, к, л). С выходов 20 и 21 сигналы «Сброс (фиг. 2,0, г) поступают на триггер 14 и регистр числа 13 соответственно и устанавливают их в нулевое состояние. С выхода 17 сигнал считывание (фиг. 2,д) постунает на дешифратор кода адреса 2, на одном из выходов 23 которого в соответствии с кодом адреса появляется сигнал, поступающий на элемент «И 3, открытый к этому моменту разрешающим потенциалом с триггера 14 (фиг. 2,е). Сигнал с выхода элемента «И 3 поступает на вход формирователя 5, с выхода которого ток считывания, протекая по координатным обмоткам накопителя 8, начинает перемагничивание сердечников. На выходах усилителей 10, 11 появляются усиленные считанные сигналы (фиг. 2,з) в соответствии с ранее записанной информацией. С выходов усилителей 10 сигналы поступают на усилители 12, на вторые входы которых подается сигнал «Строб (фиг. 2, и) от блока управления 1. С выходов усилителей 12 информация заносится в регистр числа 13.

С выхода усилителя 11 усиленный считанный сигнал поступает на единичный вход триггера 14 и по заднему фронту устанавливает его в единичное состояние (фиг . 2, (). С выхода 27 триггера 14 запрещающий потенциал подается на элементы «И 3, 4. Сигнал на выходе элементов «И 3 и соответственно ток считывания на выходе формирователя 5 обрезаются но длительности (фиг. 2,ж). Нг дежное считыванне информации обеспечив ется тем, что ток считывания выключается после занесенн се на регистре числа 13. Поскольку ток считывания выключается по заднему фронту считанного сигнала, сердечник переключается по петле гистерезиса, близкой к предельпой, при этом импульс считывания на выходе 17 блока управления 1 формируется короче, чем при перемагничивании по предельной петле.

По окончании сигнала считывания (фиг. 2, d) сигнал с выхода 20 блока управления 1 устанавливает триггер 14 в нулевое состояние. Кроме того, на выходах 16 и 18 блока управления 1 формируются сигналы «запрет и «запись (фиг. 2,е, л). Сигнал «запрет подается на выходы формирователей 7, на вторые входы 25 которых нодается код числа с регистра числа 13 (на чертежах связи регистра числа 13 с формирователями 7 не показаны).

В соответствии с кодом числа формирователи 7 подают в обмотки запрета накопителя 8 токи запрета, разрешая запись нулей и единиц. Обмотка запрета дополнительЕюго разряда 9 не используется, поэтому в нем всегда разрещена занись единицы. Сигнал «запись с выхода 18 блока управления 1 поступает на дешифратор кода адреса 2, на одном из выходов 24 которого появляется сигнал, поступающий на элемент «И 4 для формирования по длительности тока записи. В момент поступления сигнала «запись элемент «И 4 открыт разрешаюшим потенциалом с триггера 14 (фиг. 2 е, л). Сигнал с выхода элемента «И 4 возбуждает формирователь 6, с выхода которого ток записи, протекая по координатным обмотка.м накопителя 8, начинает псрсмагннчивание сердечников. На выходах усилителей 10, 11 появляются усиленные сигналы (фиг. 2,з), но так как во время записи «Строб не вырабатывается (фиг. 2, и), эти сигналы на регистр числа 13 не проходят. Сигнал с выхода усилителя 11 поступает на единичный вход триггера 14 и по заднему фронту устанавливает его в единичное состояние (фиг. 2,е). С выхода 27 триггера 14 запрещающий потенциал нодается на элементы «И 3, 4. Сигнал на выходе «И 4 н соответственно ток записи на выходе формирователя 6 обрезается по длительности (фиг. 2,м). При этом перемагничивание сердечников блока памяти 8 происходит по петле гистерезиса, близкой к предельной. Сигнал «занись на выходе 18 блока управления 1 формируется короче, чем при пере магничивании по предельной петле.

Режим стирание-запись отличается от режима считывание-восстановление тем, что

блок управления 1 не вырабатывает сигнал «Строб, а код числа для записи подается иа входы 25 формирователей 7 не от регистра числа 13, а из вычислительной машины.

Предмет изобретения

Запоминающее устройство, содержащее накопитель, выходы которого соединены со входами усилителей воспроизведения, выходы которых подключены через усилители стробирования к первым входам регистра числа, вторые входы которого соединены с одними из выходов блока управления, другие его выходы соединены со входами дешифратора адреса, выходы которого соединены с первыми входами логических элементов «И, а их выходы через формирователи импульсов записи и считывания соединены со входами накопителя, отличающееся тем. что, с целью повышения быстродействия устройства, оно содержит триггер, дополнительный усилитель воспроизведения, вход которого соединен с выходом накопителя, выход подключен к одному из входов триггера, другой вход которого с оединен с третьим выходом блока управления, а выход триггера соединен с другими входами логических элементов «И.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ТИПА ЗД | 1971 |

|

SU427380A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВОФШД | 1973 |

|

SU429466A1 |

| Полупостоянное запоминающее устройство | 1980 |

|

SU900314A1 |

| ЛОГИЧЕСКОЕ ПОЛНОТОЧНОВ ЗАПОМИНАЮЩЕЕ L'rifc :ИГ УСТРОЙСТВОI.™™———- | 1973 |

|

SU374658A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| Запоминающее устройство | 1980 |

|

SU928409A1 |

| Магнитное оперативное запоминающее устройство | 1981 |

|

SU980161A1 |

| Запоминающее устройство с автономным контролем | 1975 |

|

SU690567A1 |

| ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1973 |

|

SU393741A1 |

| Запоминающее устройство | 1978 |

|

SU799001A1 |

2

26 26 Код иисла

п

Авторы

Даты

1975-10-05—Публикация

1974-04-26—Подача