1

Изобретение относится к специализированным вычислительным устройствам, предназначенным для исследования множественных корреляционных свойств случайных процессов и для моделирования различных корреляционных дискриминаторов.

Известны Корреляторы, содержащие оперативное заооминающее устройство, регистры, нуль-оргаиы, схемы умножения и схемы усреднения. К недостаткам известных устройств следует отнести ряд ограничений, связанных с диапазоном изменения задержки (аргумента корреляционной функции) и с аппаратурным усложнением при необходимости вычисления корреляционных моментов в произвольных комбинациях.

В иредложенном корреляторе эти недостатки устранены за счет того, что коррелятор содержит наборное поле, выходы которого соединены со .входами логических блоков умножения, а его входы подключены к -первому регистру, к выхода1М нуль-органов и к выходам логических блоков умножения. Второй регистр соединен с нечетными разрядными входами, с нуль-органами, а четными - с выходами предыдущих .разрядов оперативного запоминающего устройства (ОЗУ).

Принцип работы системы запаздывания, примененный в описываемом корреляторе, состоит в задерл ке за счет времени обхода

заданного количества К слов оа-мяти. Так, значение, записанное в разряд слова, считывается через К тактов, а вместо него записывается новое значение, так как задержка считайного значения относительно текущего равняется К интервалам квантования. Если считанное из разряда значение сразу же записывать в другой разряд этого слова, то считыва1емые из этого разряда значения

будут соответствовать задержке продесса на 2К интервалов квантования и т. д. Таким образом обеспечивается возможность выбора щага задержки равным произвольному числу интервалов квантования. При этом интервал

квантования равен циклу обращения к памяти z(Af z). При числе разрядов запоминающего устройства / можно обеспечить задержки группы одновременно опрашиваемых процессов, при этом суммарное число задерм е-к

всех .процессов группы равно /.

Для организации задержек Р групп .процессов необходимо за время между последовательными отсчетами процессов (производить обращение к Р словам ОЗУ. Задержки каждой группы процессов нолучаются за счет обхода соответствующих массивов слов, которые между собой не пересекаются. Интервал квантования процессов в этом случае увеличивается в Р раз (Д PZ) , а щаг задержки

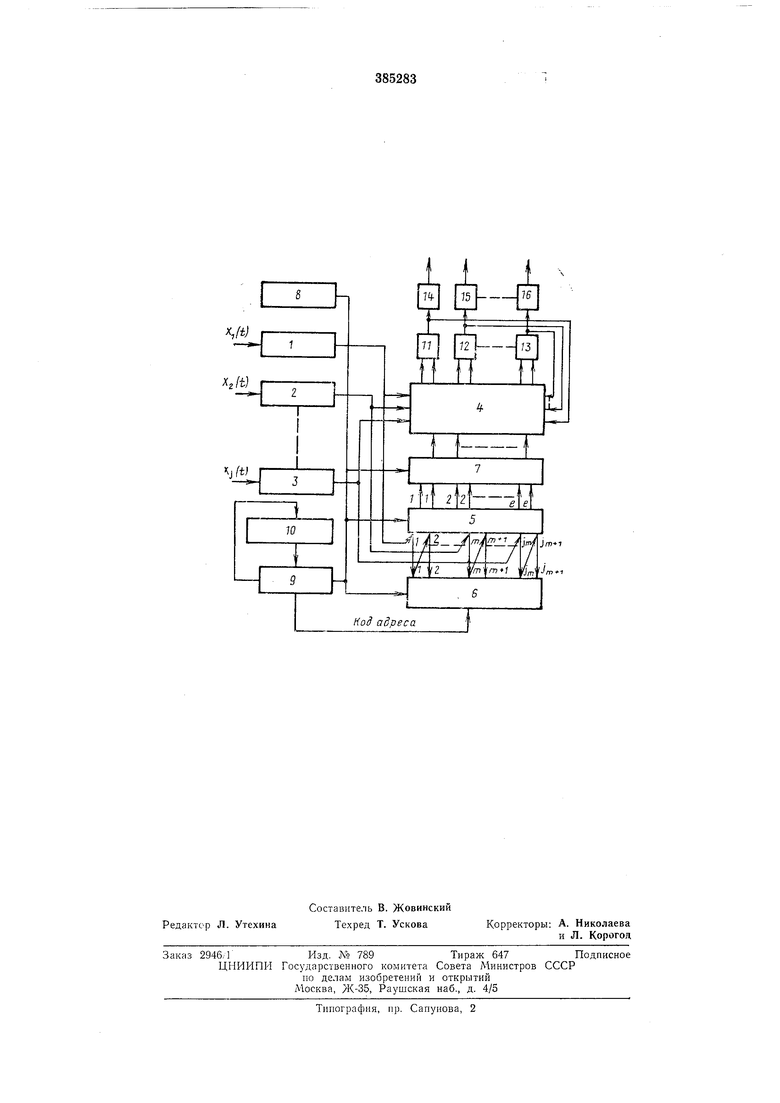

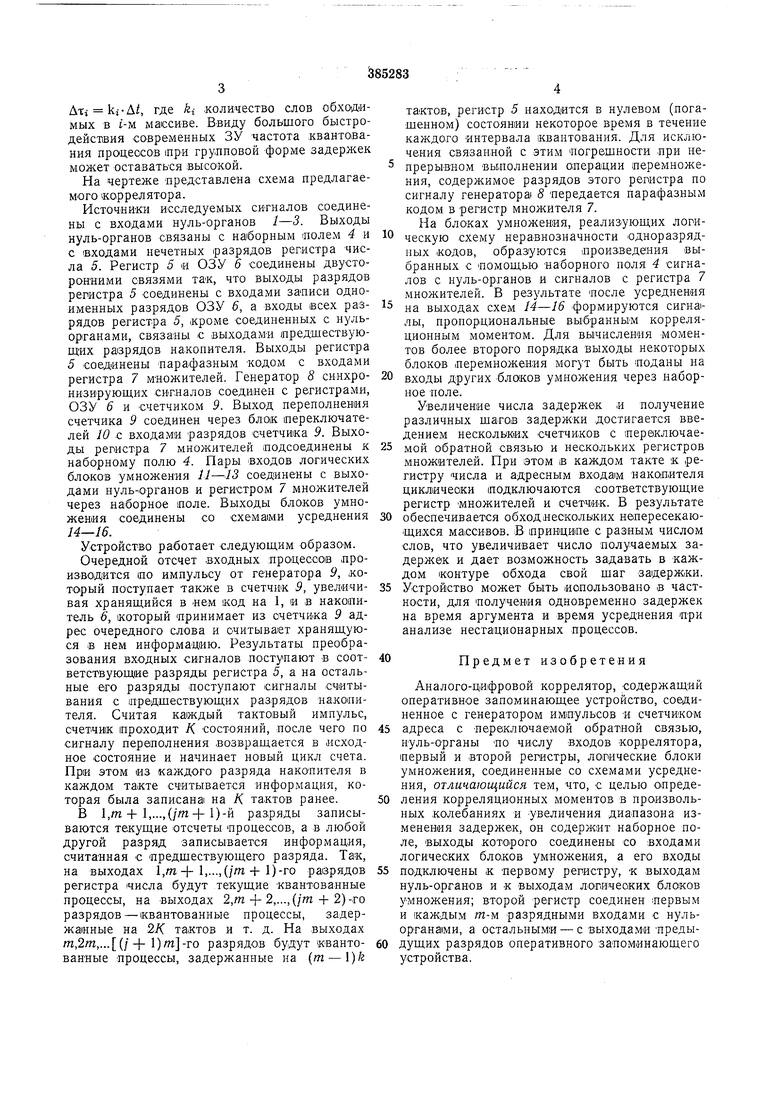

для каждой f-й группы процессов равен Ati kj-Af, где ki количество слов обходимых в t-M массиве. Ввиду большото быстродействия современных ЗУ частота .квантования процессов три групповой форме задержек может оставаться высокой. На чертеже представлена схема предлагаемого коррелятора. Источники исследуемых сигналов соединены с входами нуль-органов 1-3. Выходы нуль-органов связаны с наборным полем 4 и с входами нечетных разрядов регистра числа 5. Регистр 5 и ОЗУ 6 соединены двусторонними связями так, что выходы разрядов регистра 5 соединены с входами записи одноименных разрядов ОЗУ 5, а входы всех разрядов регистра 5, кроме соединенных с нульорганами, связаны с выходами предшествующих разрядов накопителя. Выходы регистра 5 -соединены парафазным кодом с входами регистра 7 множителей. Генератор 8 синхронизирующих сигналов соединен с регистрами, ОЗУ 6 и счетчиком 9. Выход переполнения счетчика 9 соединен через блок переключателей 10 с входами разрядов счетчика 9. Выходы регистра 7 множителей подсоединены к наборному полю 4. Пары входов логических блоков умножения 11-13 соединены с выходами нуль-органов и регистром 7 множителей через наборное поле. Выходы блоков умножения соединены со схемами усреднения 14-16. Устройство работает следующим образом. Очередной отсчет входных процессов производится по импульсу от генератора 9, который поступает также в счетчик 9, увеличивая хранящийся в «ем код на 1, и в накопитель 6, который Принимает из счетчика 9 адрес очередного слова и считывает хранящуюся в нем информацию. Результаты преобразования входных сигналов поступают в соответствующие разряды регистра 5, а на остальные его разряды поступают сигналы считывания с предшествующих разрядов накопителя. Считая каждый тактовый импульс, счетчик проходит К. состояний, после чего по сигналу переполнения возвращается в исходное состояние и начинает новый цикл счета. При этом из каждого разряда накопителя в каждом такте считывается информация, которая была записана на /С тактов ранее. В 1,т + 1,...,()-й разряды записываются текущие отсчеты процессов, а в любой другой разряд записывается информация, считанная с предшествующего разряда. Так, на выходах 1,от + 1,.,(// +1)-го ра 3рядов регистра числа будут текущие квантованные процессы, на выходах 2,т-f 2,...,(/т + 2)-го разрядов - квантованные процессы, задержанные на 2К. тактов и т. д. На выходах m,2m,...(/+1) разрядов будут квантованные процессы, задержанные на (т -1)/г тактов, регистр 5 находится в нулевом (погашенном) состоянии некоторое время в течение каждого интервала квантования. Для исключения связанной с этим погрешности при непрерывном выполнении ошерации перемножения, содержимое разрядов этого репистра по сигналу генератора 8 передается парафазным кодом в регистр множителя 7. На блоках умножения, реализующих логическую схему неравнозначности одноразряди х кодов, образуются лроизведения выбранных с ПОМОЩЬЮ наборного поля 4 сигналов с нуль-органов и сигналов с регистра 7 множителей. В результате после усреднения а выходах схем 14-16 формируются сигна: гц,, пропорциональные выбранным корреляционным моментом. Для вычисления моментов более второго порядка выходы некоторых блоков перемножения могут быть поданы на входы других -блоков умножения через наборцое поле. Увеличение числа задержек и получение различных шагов задержки достигается введением нескольких счетчиков с переключаемой обратной связью и нескольких регистров множителей. При этом в каждом такте к регистру числа и адресным входам накопителя циклически подключаются соответствующие регистр множителей и счетчик. В результате обеспечивается обходпескольких непересекающихся массивов. iB принципе с разным числом слов, что увеличивает число получаемых задержек и дает возможность задавать в каждом контуре обхода свой шаг задержки. Устройствоможет быть .использовано вчастности, для получения одновременно задержек на время аргумента и время усреднения при анализе нестационарных процессов. Предмет изобретения Аналого-цифровой коррелятор, содержащий оперативное запоминающее устройство, соеднненное с генератором импульсов и счетчиком адреса с переключаемой обратной связью, нуль-органы по числу входов коррелятора, первый и вторОЙ регистры, логические блоки умножения, соединенные со схемами усреднения, отличающийся тем, что, с целью определения корреляционных моментов в произвольных колебаниях и увеличения диапазона изменения задержек, он содержит наборное поле, выходы которого соединены со входами логических блоков умножения, а его входы подключены к первому регистру, к выходам нуль-органов и к выходам логических блоков умножения; второй регистр соединен первым и каждым т-м разрядными входами с нульрганами, а остальными - с выходами предыущих разрядов оперативного запоминающего стройства.

x,/i;

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой коррелятор | 1976 |

|

SU610117A1 |

| Многоканальный коррелятор | 1974 |

|

SU552613A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1983 |

|

SU1840196A1 |

| Цифровой знаковый коррелометр | 1980 |

|

SU962975A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2006936C1 |

| Высокочастотный коррелометр | 1976 |

|

SU647689A1 |

| Коррелометр | 1980 |

|

SU881762A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| КОРРЕЛЯЦИОННЫЙ АНАЛИЗАТОР | 2002 |

|

RU2227321C2 |

| Перестраиваемый цифровой фильтр с программируемой структурой | 2016 |

|

RU2631976C2 |

Даты

1973-01-01—Публикация