1

Изобретение относится к вычислительной технике и предназначено для .использования в цифровых вычислительных машинах, в частности, в тракте кода операции, в адресной части запоминающих устройств.

Известно устройство для контроля дешифратора, содержащее контролируемый и дублирующий дешифраторы, одноименные выходы которых объединяются с помощью группы схем «ИЛИ и с помощью группы схем «И. Такое устройство корректирует ошибку, когда у одного из дешифраторов не возбуждается ни одна из шин или когда у одного из дешифраторов вместе с избранной выходной шиной возбуждается одна «еизбранная.

Предлагаемое устройство отличается от известного тем, что в него, в целях повышения корректирующей способности, введены две схемы контроля (например, на базе суммирующего трансформатора), триггер, схема «И, группа схем «И и группа схем «ИЛИ, причем основная группа схем 5:ИЛИ соединена со входами первой схемы контроля и дополнительной группы схем «И. Выход первой схемы контроля соединен с единичным входом триггера и с управляющим входом схемы «И, другой вход которой соединен с выходом второй схемы контроля. Выходы основной группы схем «И соединены со входами второй схемы контроля и с первыми входами дополнительной группы схем «ИЛИ. Вторые входы последней соединены с выходами дополнительной группы схем «И, управляющий вход которой соединен с выходом триггера.

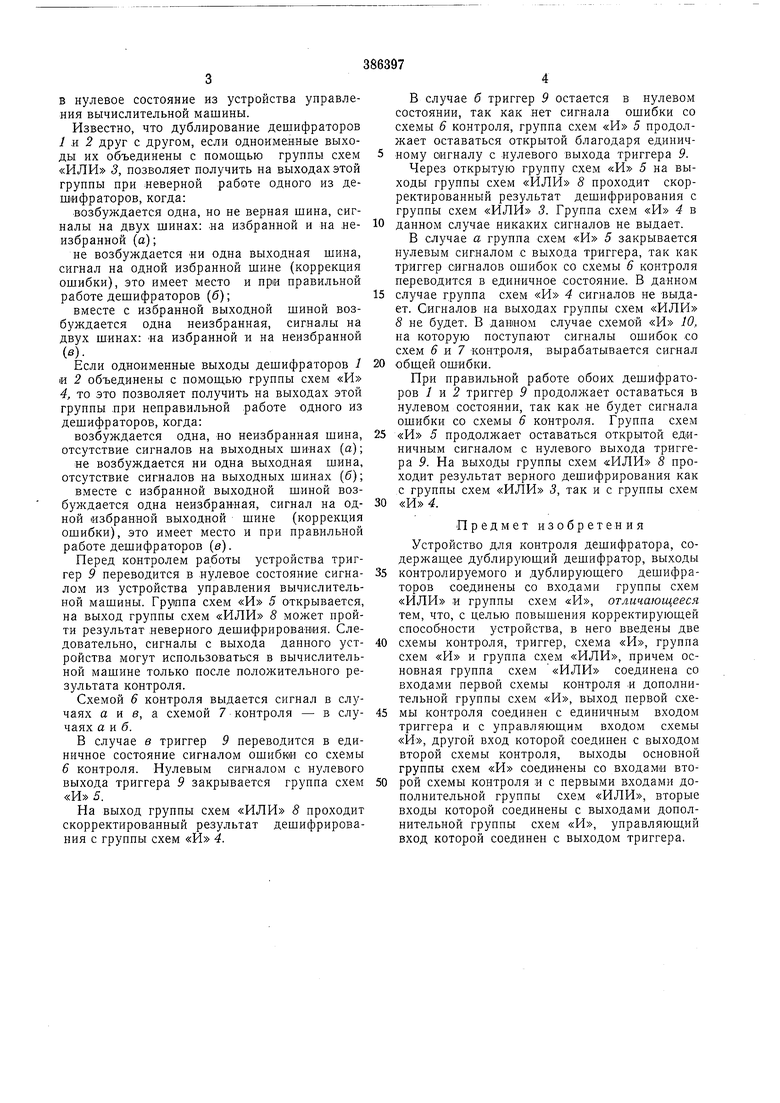

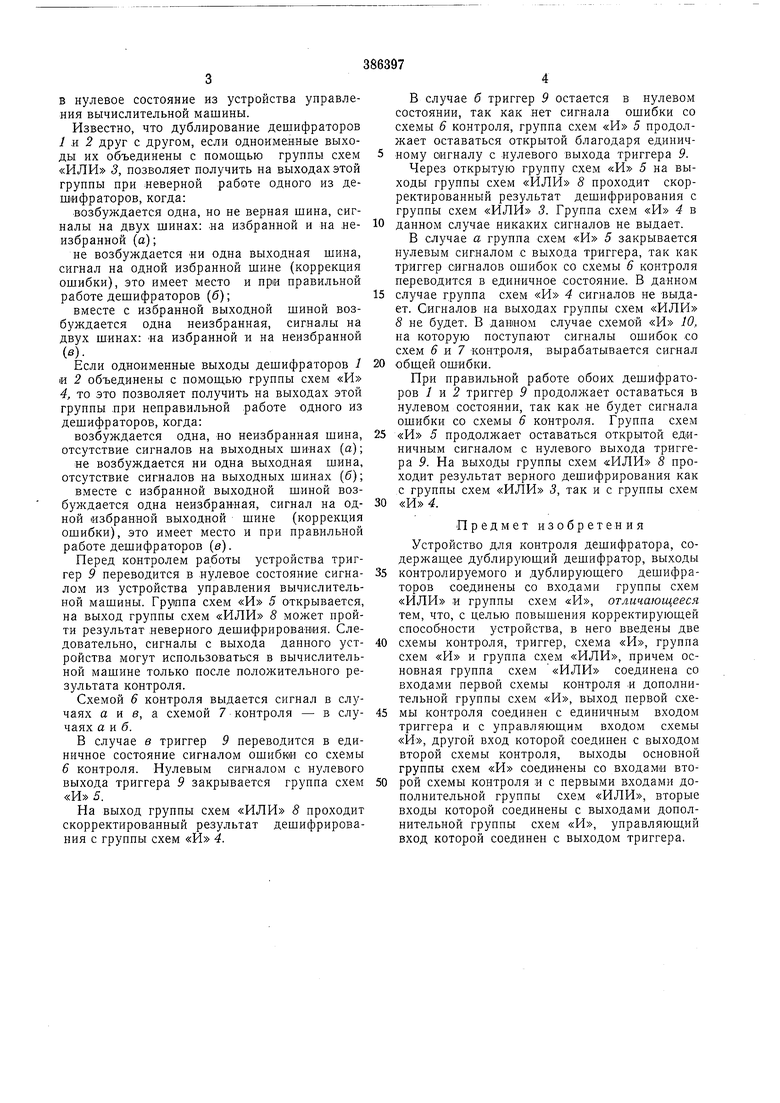

Блок-схема устройства для контроля дешифратора показала на чертеже.

Устройство содержит контролируемый / и дублирующий 2 дешифраторы, группу схем «ИЛИ 3, две группы схем «И 4 и 5, две схемы 5 и 7 контроля (например, на базе суммирующего трансформатора), группу схем «ИЛИ 8, триггер 9 и схему «И 10.

Дещифраторы / и 2 дублируют друг друга, одноименные выходы первого ,и второго дешифраторов связаны со входами группы схем «ИЛИ 5 и группы схем «И 4. Выходы группы схем «ИЛИ 3 связаны со входами группы схем «И 5 « схемы 6 контроля, а выходы группы схем «И 4 - со входами схемы 7 контроля и с первыми входами группы схем «ИЛИ 8, со вторыми входами которых соединены выходами группы схем «И 5. Управляющие входы группы схем «И 5 соединены с нулевым выходом триггера 9. Единичный вход триггера соединен с выходом схемы 6 контроля. Выходы схем 6 и 7 контроля связаны со входами схемы «И 10. С нулевым входом триггера 9 соединена шина перевода его

в нулевое состояние из устройства управления вычислительной машины.

Известно, что дублирование дешифраторов 1 а. 2 друг с другом, если одноименные выходы их объединены с помошью группы схем «ИЛИ 3, позволяет получить на выходах этой группы при неверной работе одного из дешифраторов, когда:

возбуждается одна, но не верная шина, сигналы на двух шинах: .на избранной и на .неизбранной (а);

не возбуждается «и одна выходная шина, сигнал на одной избранной ши.не (коррекция ошибки), это имеет место и при правильной работе дешифраторов (б);

вместе с избранной выходной шиной возбуждается одна неизбранная, сигналы на двух шинах: «а избранной и на неизбранной

(е).

Если одноименные выходы дешифраторов 1 и 2 объединены с помош,ью группы схем «И 4, то это позволяет получить на выходах этой группы .при неправильной работе одного из дешифраторов, когда:

возбуждается одна, но неизбранная шина, отсутствие сигналов на выходных ши-нах (а);

не возбуждается ни одна выходная шина, отсутствие сигналов на выходных шинах (б);

вместе с избранной выходной шиной возбуждается одна неизбранная, сигнал на одной избранной выходной шине (коррекция ошибки), это имеет место и при правильной работе дешифрато.ров (в.

Перед контролем работы устройства триггер 9 переводится в нулевое состояние сигналом из устройства управления вычислительной машины. Группа схем «И 5 открывается, на выход группы схем «ИЛИ 8 может пройти результат неверного дешифрирования. Следовательно, сигналы с выхода данного устройства могут использоваться в вычислительной машине только после положительного результата контроля.

Схемой 6 контроля выдается сигнал в случаях а и в, а схемой 7 контроля - в случаях а к б.

В случае в триггер 9 переводится в единичное состояние сигналом ошибки со схемы 6 контроля. Нулевым сигналом с нулевого выхода триггера 9 закрывается группа схем «И 5.

На выход группы схем «ИЛИ 8 проходит скорректированный результат дешифрирования с группы схем «И 4.

В случае б триггер 9 остается в нулевом состоянии, так как нет сигнала ошибки со схемы 6 контроля, группа схем «И 5 продолжает оставаться открытой благодаря единичному оигналу с нулевого выхода триггера 9.

Через открытую группу схем «И 5 на выходы группы схем «ИЛИ 8 проходит скорректированный результат дешифрирования с группы схем «ИЛИ 3. Группа схем «И 4 в

данном случае никаких сигналов не выдает.

В случае а группа схем «И 5 закрывается нулевым сигналом с выхода триггера, так как триггер сигналов ошибок со схемы 6 контроля переводится в единичное состояние. В данном

случае группа схем «И 4 сигналов не выдает. Сигналов на выходах группы схем «ИЛИ 8 не будет. В данном случае схемой «И 10, на которую поступают сигналы ошибок .со схем 5 и 7 контроля, вырабатывается сигнал

.общей ошибки.

При правильной работе обоих дешифраторов 1 н 2 триггер 9 продолжает оставаться в нулевом состоянии, так как не будет сигнала ошибки со схемы 6 контроля. Группа схем

«И 5 продолжает оставаться открытой единичным сигналом с нулевого выхода триггера 9. На выходы группы схем «ИЛИ 8 проходит результат верного дешифрирования как с группы схем «ИЛИ 3, так и с группы схем

«И 4.

Предмет изобретения

Устройство для контроля дешифратора, содержащее дублируюший дешифратор, выходы

контролируемого и дублирующего дешифраторов соединены со входами группы схем «ИЛИ и группы схем «И, отличающееся тем, что, с целью повышения корректирующей способности устройства, в него введены две

схемы ко.нтроля, триггер, схема «И, группа схем «И и группа схем «ИЛИ, причем основная группа схем «ИЛИ соединена со входами первой схемы контроля .и дополнительной группы схем «И, выход первой схемы контроля соединен с единичным входом триггера и с управляющим входом схемы «И, другой вход которой соединен с выходом второй схемы контроля, выходы основной группы схем «И соединены со входами второй схемы контроля и с первыми входами дополнительной группы схем «ИЛИ, вторые входы которой соединены с выходами дополнительной группы схем «И, управляющий вход которой соединен с выходом триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОЛЬЦЕВОЙ ДЕШИФРАТОР | 1972 |

|

SU342298A1 |

| Устройство для контроля дешифратора | 1979 |

|

SU811262A1 |

| Дешифратор с коррекцией ошибок | 1981 |

|

SU1012262A1 |

| Дублированная вычислительная система | 1990 |

|

SU1783528A1 |

| Устройство для исследования путей в графах | 1981 |

|

SU1005066A2 |

| Шифратор-дешифратор позиционного @ -импульсного кода | 1982 |

|

SU1069158A1 |

| Устройство для диагностирования многоканальных резервированных систем | 1984 |

|

SU1172096A1 |

| Устройство для регистрации расписаний | 1979 |

|

SU855668A1 |

| Устройство для сопряжения электронных вычислительных машин | 1981 |

|

SU1013938A1 |

| Устройство для контроля и коррекции информации | 1980 |

|

SU940160A1 |

Авторы

Даты

1973-01-01—Публикация