1

Изобретение относится к вычислительной технике и может быть использовано в генераторах расписаний при решении практических задач теории расписаний для выполнения следующи с функций: регистрация номеров операций в такой последовательности, в какой их вырабатывает генератор; блокировка номера операции, повторно поступающего на вход устройства в течение цикла выработки одного расписания; проверка того, все ли номера операций поступают из генератора и зарегистрированы; по окончании регистрации всех номеров операций, т.е. при сформировании одного из возможных расписаний, запоминание сформированного расписания и подготовка к циклу выработки следующего расписания.

Известно устройство для регистрации расписаний, позволяющее моделировать частные задачи теории распи7 саний, представленные в виде сетевых графов 1 .

Однако данное устройство построено на аналоговых элементах, обладает недостаточным быстродействием,надежностью и не обеспечивает выполнение приведенных выше функций.

Наиболее близким к предлагаемому является устройство для регистрации расписаний, содержащее матричную панель, два регистра, блок сравнения, квммутирующие элементы, дешифратор, а также элементы И и ИЛИ 2.

Однако данное устройство предназначено для отображения кривых, задаваемых значениями ординат, и не мо10жет выполнять перечисленные функции с достаточной степенью точности.

Цель изобретения - повышение точности устройства.

Поставленная цель достигается тем,

15 что в устройство для регистрации расписаний, содержащее регистр сдвига, разрядные выходы которого соединены с разрядными входами регистра памяти соответственно дешифратор, входы

20 которого соединены с выходами группы элементов И соответственно, первые входы которых являйтся входами устройства, введен коммутатор, шифратор, триггер и счетчик, выход которого сое25динен с разрядными входами регистра сдвига и с единичным входом триггера, выход которого соединен со вторыми входами элементов И группы, а нулевой вход счетчика является входом Сброс устройства и объединен со

30

входом К01«1мутатора, группа входов которого подключена к группе выходов дешифратора соответственно, а группа выходов коммутатора соответстпонно соединена со счетным входом счетчика и с группой входов шифратора соответственно, выход которого 7оединен с информационным входом регистра сдвига, причем коммутатор содержит группу триггеров и группу элементов И, первые входы которых являются группой входов коммутатора, а вторые входы элементов И группы соединены с нулевыми выходами триггеров группы соответственно, единичные входы которых соединены с выходами элементов И группы соответственно, вход коммутатора подключен к нулевым входам тригтеров группы, единичные выходы которых являются группой выходов коммутатора.

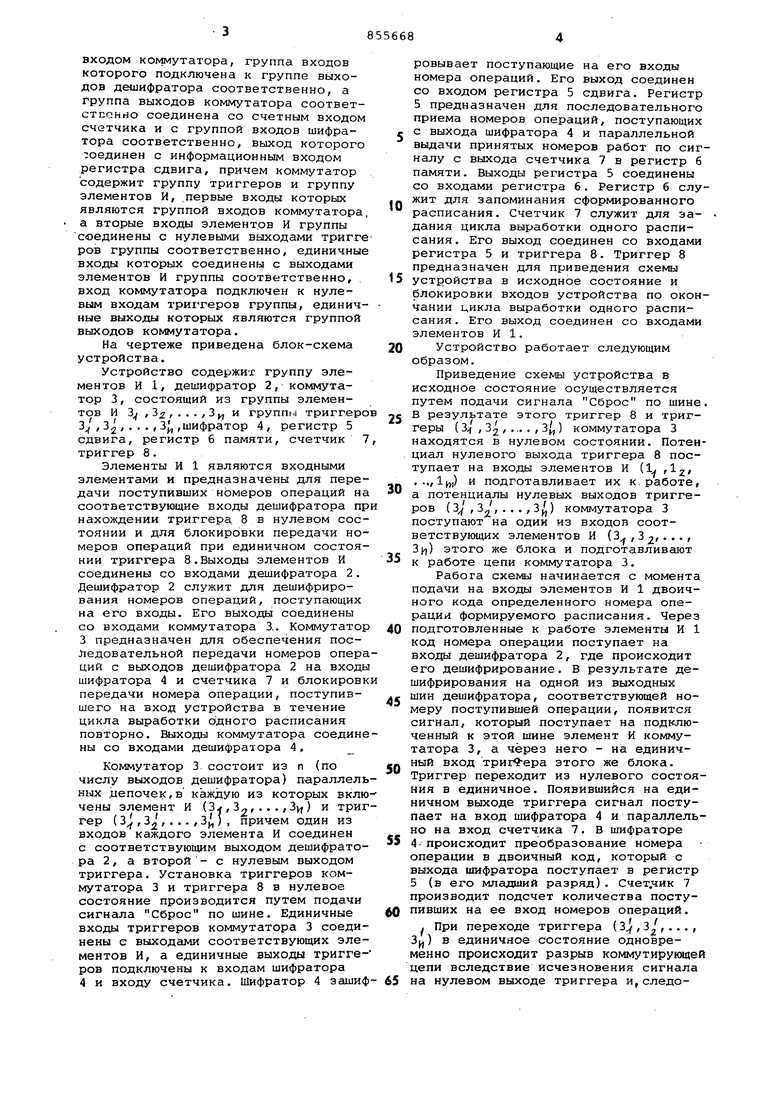

На чертеже приведена блок-схема устройства.

Устройство содержит группу элементов И 1, дешифратор 2, коммутатор 3, состоящий из группы элементов И 3 , 3 , . . . / 3 и rpynnt.i триггеро , 3 ,..., 3,,шифратор 4, регистр 5 сдвига, регистр 6 памяти, счетчик 7 триггер 8.

Элементы И 1 являются входными элементами и предназначены для передачи поступивших номеров операций на соответствующие входы дешифратора пр нахождении триггера. 8 в нулевом состоянии и для блокировки передачи номеров операций при единичном состоянии триггера 8.Выходы элементов И соединены со входами дешифратора 2. Дешифратор 2 служит для дешифрирования номеров операций, поступающих на его входы. Его выходы соединены со входами коммутатора 3.. Коммутатор

3предназначен для обеспечения последовательной передачи номеров операций с выходов дешифратора 2 на входы шифратора 4 и счетчика 7 и блокировк передачи номера операции, поступившего на вход устройства в течение цикла выработки с(дного расписания повторно. Выходы коммутатора соединены со входами дешифратора 4,

Коммутатор 3 состоит из п (по числу выходов дешифратора) п-араллельных .цепочек,в каждую из которых включены элемент И (3 , 3, Зу) и триггер (3 ,3,. .. ,3|1,) , причем один из входов каждого элемента И соединен с соответствующим выходом дешифратора 2 , а второй - с нулевым выходом триггера. Установка триггеров коммутатора 3 и триггера 8 в нулевое состояние производится путем подачи сигнала Сброс по шине. Единичные входы триггеров коммутатора 3 соединены с выходами соответствующих элементов И, а единичные выходы триггеров подключены к входам шифратора

4и входу счетчика. Шифратор 4 зашифровывает поступающие на его входы номера операций. Его выход соединен со входом регистра 5 сдвига. Регистр 5 предназначен для последовательного приема номеров операций, поступающих с выхода шифратора 4 и параллельной выдачи принятых номеров работ по сигналу с выхода счетчика 7 в регистр б памяти. Выходы регистра 5 соединены со входами регистра 6. Регистр 6 служит для запоминания сформированного расписания. Счетчик 7 служит для заДания цикла выработки одного расписания. Его выход соединен со входами регистра 5 и триггера 8. Триггер 8 предназначен для приведения схемы устройства в исходное состояние и блокировки входов устройства по окончании иикла выработки одного расписания. Его выход соединен со входами элементов И 1.

Устройство работает следующим образом.

Приведение схемы устройства в исходное состояние осуществляется путем подачи сигнала Сброс по шине В результате этого триггер 8 и триггеры (3-/ , 32 , ... . , 3|,) коммутатора 3 находятся в нулевом состоянии. Потенциал нулевого выхода триггера 8 поступает на входы элементов И (i. ,12.1 ..., 1|) и подготавливает их к работе, а потенциалы нулевых выходов триггеров Oj ,3,, . , , , коммутатора 3 поступают на один из входов соответствующих элементов И (3-,32, 3ji) этого же блока и подготавливают к работе цепи коммутатора 3.

Работа начинается с момента подачи на входы элементов И 1 двоичного кода определенного номера операции формируемого расписания. Через подготовленные к работе элементы И 1 код номера операции поступает на входы дешифратора 2, где происходит его дешифрирование. В результате дешифрирования на одной из выходных шин дешифратора, соответствующей номеру поступившей операции, появится сигнал, который поступает на подключенный к этой шине элемент И коммутатора 3, а через него - на единичный вход триггера этого же блока. Триггер переходит из нулевого состояния в единичное. Появившийся на единичном выходе триггера сигнал поступает на вход шифратора 4 и параллельно на вход счетчика 7. В шифраторе

4происходит преобразование нЬмера операции в двоичный код, который с выхода шифратора поступает в регистр

5(в его младший разряд) . Счет.чик 7 производит подсчет количества поступивших на ее вход номеров операций.

, При переходе триггера (3 ,, . . . , 3) в единичное состояние одновременно происходит разрыв коммутирующей цепи вследствие исчезновения сигнала на нулевом выходе триггера и,следовательно, отключения соответствующег элемента И коммутатора 3. Этим обес печивается блокировка номера операции, повторно поступающего на вход устройства в течение цикла выработки одного расписания. При поступлении на входы устройства кодов последующих номеров операций работа устройства аналогична описанной на предьвдущем шаге. При этом счетчик 7 производит контроль того, все ли номера операций поступают из генератора и зарегистрированы, а в регистре 5 происходит накопление номеров операций в поряд ке их поступления (путем сдвига), т.е. формирование одного из возможных расписаний. По окончании регистрации всех номеров операций, т.е. при сформиро вании одного из возможных расписаний счетчик 7 вырабатывает сигнал, который переводит триггер 8 в единичнс е состояние, чем отключает входы устройства из дальнейшей работы. Этим же сигналом производится передача сформированного расписания из регистра 5 в регистр 6, где оно может храниться необходимое время, а регистр 5 подготовлен для регистр ции следующего расписания. Подачей сигнала Сброс по шине устройство подготовлено к циклу вы работки следующего расписания. Эффект заключается в разработке новог устройства,являющегося ОСНОВНЕЛМ зле ментом рандомизированного генератор расписаний и позволяющего выполнять регистрацию номеров операций в последовательности выработки их генера тором: блокировку номеров .операций, повторно поступающих на вход устройства в течение цикла выработки одного расписания; проверку поступления и регистрацию Btex номеров операций, выработанных генератором; запоминание сформированного расписа ния и подготовку к циклу выработки следующего расписания. Формула изобретения 1. Устройство для регистрации расписаний, содержащее регистр сдви ; разрядные выходы которого соединены с разрядными входами регисара памяти, соответственно,дешифратор, входы которого соединены с выходами группы элементов И соответственно, первые входы которых являются входами устройства, отличающееся тем, что, с целью повышения точности устройства, оно содержит коммутатор , шифратор , триггер и счетчик, выход которого соединен с разрядными входами регистра сдвига и с единичным входом триггера, выход которого соединен со вторыми входами элементов И группы, а нулевой вход счетчика является входом Сброс устройства и объединен со входом коммутатора, группа входов которого подключена к группе выходов дешифратора соответственно, а группа выходов коммутатора соединена со счетным входом счетчика и с группой входов шифратора соответственно, выход которого соединен с информационным входом регистра сдвига. 2. Устройство по П.1, о т л ичающееся тем, что коммутатор содержит группу триггеров и группу элементов И, первые входы которых являются группой входов коммутатора, а вторые входы элементов И группы соединены с нулевыми выxdnaMK триггеров группы соответственно, единичные входы которых соединены с выходами элементов И группы соответственно, вход коммутатора подключен к нулевым входам т нггеров группы, единичные выходы которых являются группой выходов коммутатора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР по заявке 461461/18-24, кл. G 06 G Т/122, 1977. 2.Авторское свидетельство СССР 2690783, кл. G 06 К 15/18, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1992 |

|

RU2032938C1 |

| Устройство для формирования тестовой последовательности | 1984 |

|

SU1218389A1 |

| МОДУЛЬНОЕ УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2112269C1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1251086A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1986 |

|

SU1363224A1 |

| Делительное устройство | 1983 |

|

SU1176324A1 |

| Устройство для сдвига информации | 1981 |

|

SU1014031A1 |

| Устройство для формирования тестов | 1986 |

|

SU1336013A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1305687A1 |

Авторы

Даты

1981-08-15—Публикация

1979-12-14—Подача