1

Изобретение относится к устройствам автоматики, телемеханики и вычислительной техники и может быть использовано для непрерывного контроля и коррекции работы различных типов дешифраторов.

Известно устройство для контроля дешифратора 1, содержаш,ее дублируюш;ий дешифратор, группу схем нечетности по количеству выходов контролируемого и дублируюш,его дешифраторов, элементы ИЛИ, И. Недостатком устройства является отсутствие коррекции результатов дешифрирования при отказах (сбоях) контролируемого дешифратора.

Иаиболее близким по технической сущности к изобретению является устройство для контроля дешифратора 2, содержаш,ее дублируюш,ий дешифратор, два блока элементов ИЛИ, два блока элементов И, два блока контроля, триггер и элемент И.

К недостаткам известного устройства следует отнести отсутствие коррекции результатов дешифрирования, когда на выходе контролируемого дешифратора возбуждается одна, но не требуемая шина, а также схемную избыточность, заключающуюся в необходимости построения двух специальных блоков контроля.

Целью изобретения является повышение корректирующей способности и упрощение устройства.

Эта цель достигается тем, что устройство для контроля дешифратора, содерж:ащее блок контроля, дублирующий дешифратор, два блока элементов И, блок элементов ИЛИ, причем группа входов дублирующего дешифратора является группой

входов устройства, выход дублирующего дешифратора соединен с информационным входом первого блока элементов И, выход которого соединен с первым входом блока элементов ИЛИ и первым входом блока

контроля, выход второго блока элементов И соединен со вторым в.ходом блока элементов ИЛИ, выход которого является информационным выходом устройства, содержит также третий блок элементов И, а блок

контроля содержит элементы И, ИЕ, ИЛИ, ИЛИ-НЕ, исключающее ИЛИ-НЕ. Выход первого элемента ИЛИ соединен с первым входом элемента И, с разрешающим входом третьего блока элементов И и через

элемент НЕ - с управляющим входом первого блока элементов И. Выход элемента исключающее ИЛИ-НЕ соединен с первым входом второго элемента ИЛИ, выход которого является выходом сбоя устройства. Выход элемента ИЛИ-НЕ соединен со

вторым входом элемента И и запрещающим входом третьего блока элементов И, выход которого соединен с третьим входом блока элементов ИЛИ. Выход дублирующего дешифратора соединен с уиравляющим входом второго блока элементов И, информ«ационным входом третьего блока элементов И и входом третьего элемента Р1ЛИ, выход которого соединен с третьим входом элемента И. Выход элемента И соединен со вторым входом второго элемента ИЛИ, третий вход которого является первым входом блока контроля. Информационный вход второго блока элементов И, вход первого элемента ИЛИ и вход элемента исключающее ИЛИ-ИЕ соединены с выходом контролируемого дешифратора. Выход второго блока элементов И соединен со входом элемента ИЛИ-ИЕ.

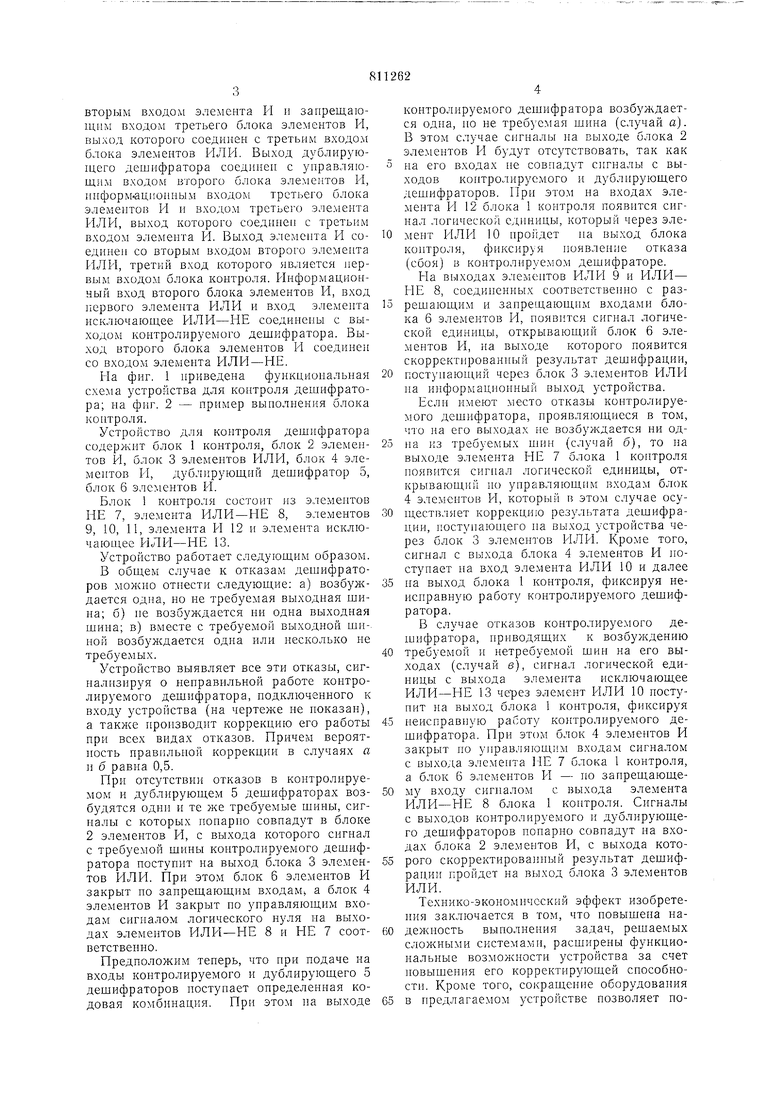

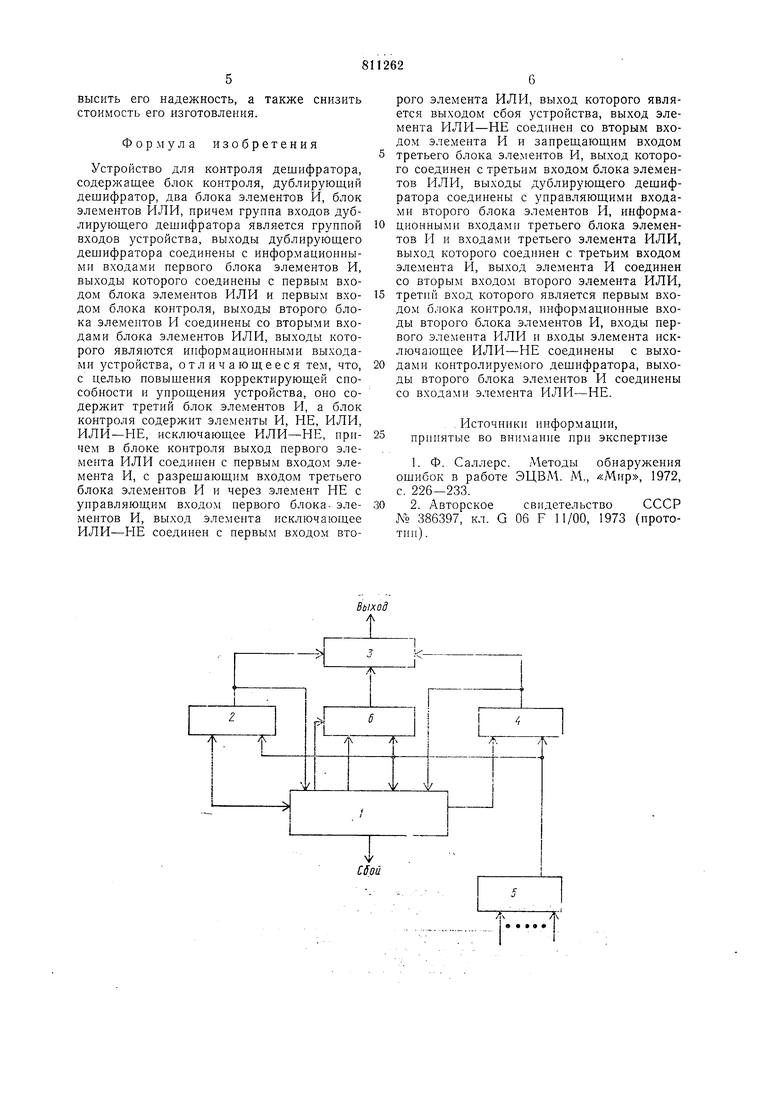

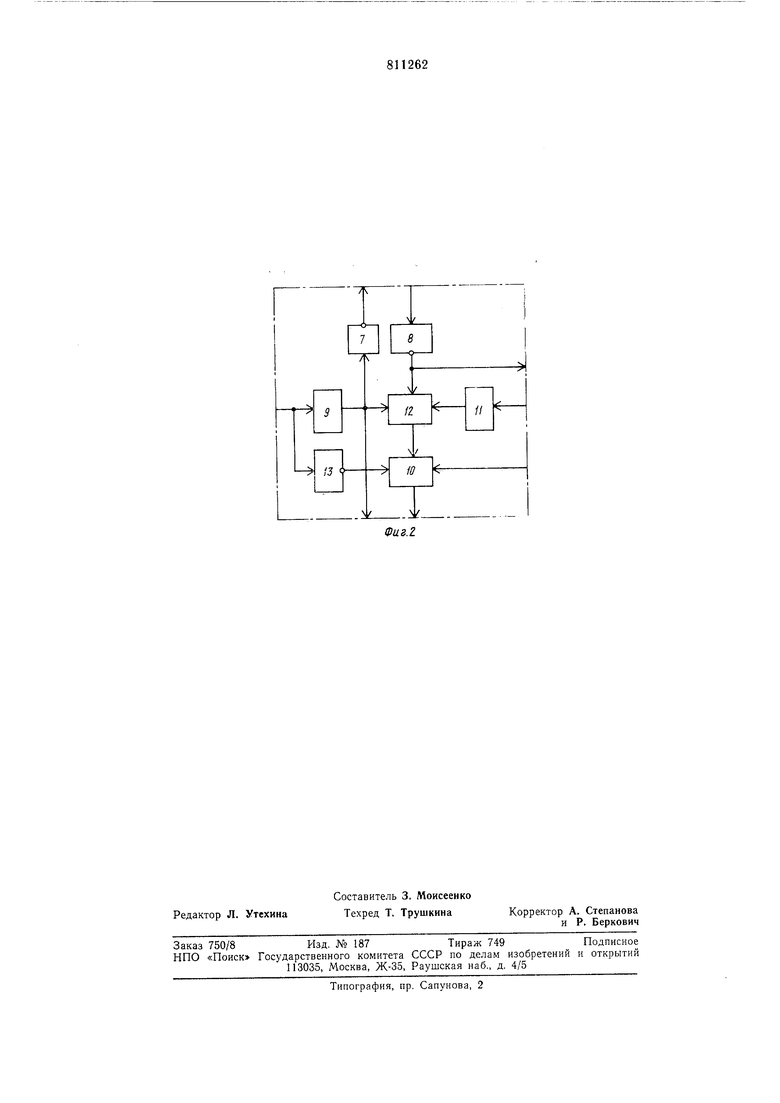

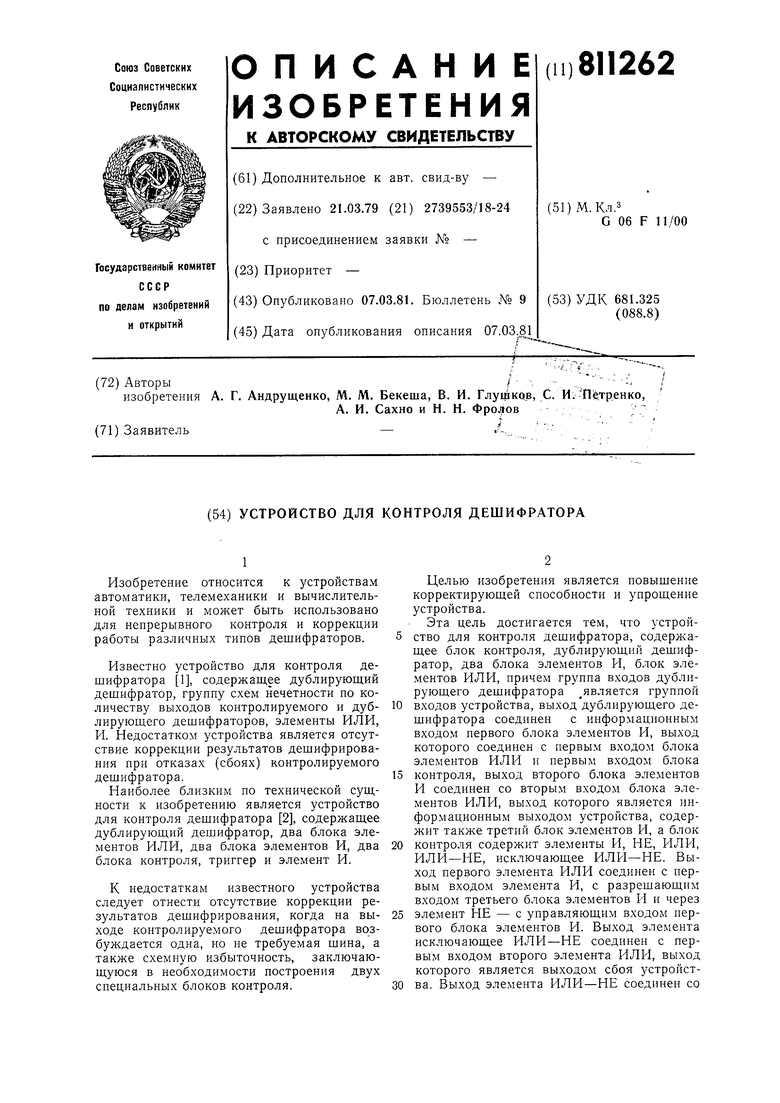

На фиг. 1 приведена функциональная схема устройства для контроля дещифратора; на фиг. 2 - нрнмер выполнения блока контроля.

Устройство для контроля дешифратора содержит блок 1 контроля, блок 2 элементов И, блок 3 элементов ИЛИ, блок 4 элементов И, дублирующий дешифратор 5, блок 6 элементов И.

Блок 1 контроля состоит из элементов НЕ 7, элемента ИЛИ-НЕ 8, элементов 9, 10, II, элемента И 12 и элемента исключающее ИЛИ-НЕ 13.

Устройство работает следующим образом.

В общем случае к отказам дешифраторов можно отнести следующие: а) возбуждается одна, но не требуемая выходная щина; б) не возбуждается ни одна выходная шина; в) вместе с требуемой выходной ши-, ной возбуждается одна или несколько не требуемых.

Устройство выявляет все эти отказы, сигнализируя о неправильной работе контролируемого дешифратора, подключенного к входу устройства (на чертеже не показан), а такл- е производит коррекцию его работы при всех видах отказов. Причем вероятность правильной коррекции в случаях а и б равна 0,5.

При отсутствии отказов в контролируемом и дублирующем 5 дешифраторах возбудятся одни и те же требуемые шнны, сигналы с которых попарно совпадут в блоке 2 элементов И, с выхода которого сигнал с требуемой шины контролируемого дешифратора поступит на выход блока 3 элементов ИЛИ. При этом блок 6 элементов И закрыт по запрещающим входам а блок 4 элементов И закрыт по управляющим входам сигналом логического нуля на выходах элементов ИЛИ-НЕ 8 и НЕ 7 соответственно.

Предположим теперь, что при подаче на входы контролируемого и дублирующего 5 дешифраторов поступает определенная кодовая комбинация. При этом на выходе

контролируемого дешифратора возбуждается одна, но не требуемая шина (случай а). В этом случае сигналы на выходе блока 2 эле.ментов И будут отсутствовать, так как на его входах не совпадут сигналы с выходов контролируемого и дублирующего дешифраторов. При этом на входах элемента И 12 блока 1 контроля появится сигнал логической единицы, который через элемент ИЛИ 10 пройдет на выход блока контроля, фиксируя ноявление отказа (сбоя) в контролируемом дешифраторе.

На выходах элементов ИЛР1 9 и ИЛИ-- НЕ 8, соединенных соответственно с разрешающим и запрещающим входами блока 6 элементов И, появится сигнал логической единицы, открывающий блок 6 элементов И, на выходе которого появится скорректированный результат дешифрации,

поступающий через блок 3 элементов ИЛИ на информационный выход устройства.

Если имеют место отказы контролируемого дешифратора, проявляющиеся в том, что на его выходах не возбуждается ни одна из требуемых шин (случай б), то на выходе элемента НЕ 7 блока 1 контроля появится сигнал логической единицы, открывающий по управляющим входам блок 4 элементов И, который в этом случае осуществляет коррекцию результата дещифрации, поступающего на выход устройства через блок 3 элементов ИЛИ. Кроме того, сигнал с выхода блока 4 элементов И ноступает на вход элемента ИЛИ 10 и далее

на выход блока 1 контроля, фиксируя неисправную работу контролируемого дешифратора.

В случае отказов контролируемого дешифратора, приводящих к возбуждению

требуемой и нетребуемой шин на его выходах (случай в), сигнал логической единицы с выхода элемента исключающее ИЛИ-НЕ 13 через элемент ИЛИ 10 поступит на выход блока 1 контроля, фиксируя

неисправную работу контролируемого дешифратора. При этом блок 4 элементов И закрыт по управляющим входам сигналом с выхода элемента НЕ 7 блока 1 контроля, а блок 6 элементов И - по запрещающему входу сигналом с выхода элемента ИЛИ-НЕ 8 блока 1 контроля. Сигналы с выходов контролируемого и дублирующего дешифраторов попарно совпадут на входах блока 2 элементов И, с выхода которого скорректированный результат дешифрации пройдет на выход блока 3 элементов ИЛИ.

Технико-экономический эффект изобретения заключается в том, что повышена надежность выполнения задач, рещаемых сложными системами, расширены функциональные возможности устройства за счет повышения его корректирующей способности. Кроме того, сокращение оборудования

в предлагаемом устройстве позволяет повысить его надежность, а также снизить стоимость его изготовления.

Формула изобретения

Устройство для контроля дешифратора, содержащее блок контроля, дублирующий дещифратор, два блока элементов И, блок элементов ИЛИ, причем группа входов дублирующего дешифратора является группой входов устройства, выходы дублирующего дещифратора соединены с информационными входами первого блока элементов И, выходы которого соединены с первым входом блока элементов ИЛИ и первым входом блока контроля, выходы второго блока элементов И соединены со вторыми входами блока элементов ИЛИ, выходы которого являются информационными выходами устройства, отличающееся тем, что, с целью повышения корректирующей способности и упрощения устройства, оно содержит третий блок элементов И, а блок контроля содержит элементы И, НЕ, ИЛИ, ИЛИ-НЕ, исключающее ИЛИ-НЕ, причем в блоке контроля выход первого элемента ИЛИ соединен с первым входом элемента И, с разрещающим входом третьего блока элементов И и через элемент НЕ с управляющим входом первого блока- элементов И, выход элемента исключающее ИЛИ-НЕ соединен с первым входом второго элемента ИЛИ, выход которого является выходом сбоя устройства, выход элемента ИЛИ-НЕ соединен со вторым входом элемента И и запрещающим входом

третьего блока элементов И, выход которого соединен с третьим входом блока элементов ИЛИ, выходы дублирующего дешифратора соединены с управляющими входами второго блока элементов И, информационными входами третьего блока элементов И и входами третьего элемента ИЛИ, выход которого соединен с третьим входом элемента И, выход элемента И соединен со вторым входом второго элемента ИЛИ,

третий вход которого является первым входом блока контроля, информационные входы второго блока элементов И, входы первого элемента ИЛИ и входы элемента исключающее ИЛИ-НЕ соединены с выходами контролируемого дещифратора, выходы второго блока элементов И соединены со входами элемента ИЛИ-НЕ.

. Источники информации, принятые во внимание при экспертизе

1.Ф. Саллерс. Методы обнаружения ошибок в работе ЭЦВМ. М., «Мир, 1972, с. 226-233.

2.Авторское свидетельство СССР 386397, кл. G 06 Е 11/00, 1973 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля дешифраторов | 1985 |

|

SU1298924A1 |

| Устройство для контроля дешифратора | 1982 |

|

SU1024923A1 |

| Устройство для контроля дешифратора | 1980 |

|

SU918948A1 |

| Устройство для контроля цифровых объектов | 1982 |

|

SU1072048A1 |

| Устройство для контроля дешифраторов | 1986 |

|

SU1339899A1 |

| Устройство для контроля счетчика | 1980 |

|

SU884148A1 |

| «ь^г^СОЮЗНАЯ | 1973 |

|

SU386397A1 |

| Устройство опроса и контроля длядАТчиКОВ СОСТОяНия Об'ЕКТОВ | 1979 |

|

SU849155A1 |

| Запоминающее устройство с автономным контролем | 1972 |

|

SU439020A1 |

| Устройство для контроля системы телемеханики с решающей обратной связью | 1981 |

|

SU1029208A1 |

Авторы

Даты

1981-03-07—Публикация

1979-03-21—Подача