(Б) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И КОРРЕКЦИИ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор ввода-вывода с коррек-циЕй ОшибОК | 1979 |

|

SU849221A1 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

| Устройство для обнаружения и коррекции ошибок | 1990 |

|

SU1783583A1 |

| Устройство для контроля блоков обнаружения и коррекции ошибок,работающих с кодом Хэмминга | 1982 |

|

SU1072050A1 |

| Устройство для контроля цифровых данных | 1985 |

|

SU1381718A1 |

| Запоминающее устройство | 1987 |

|

SU1481865A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1249590A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| Запоминающее устройство | 1981 |

|

SU1014042A1 |

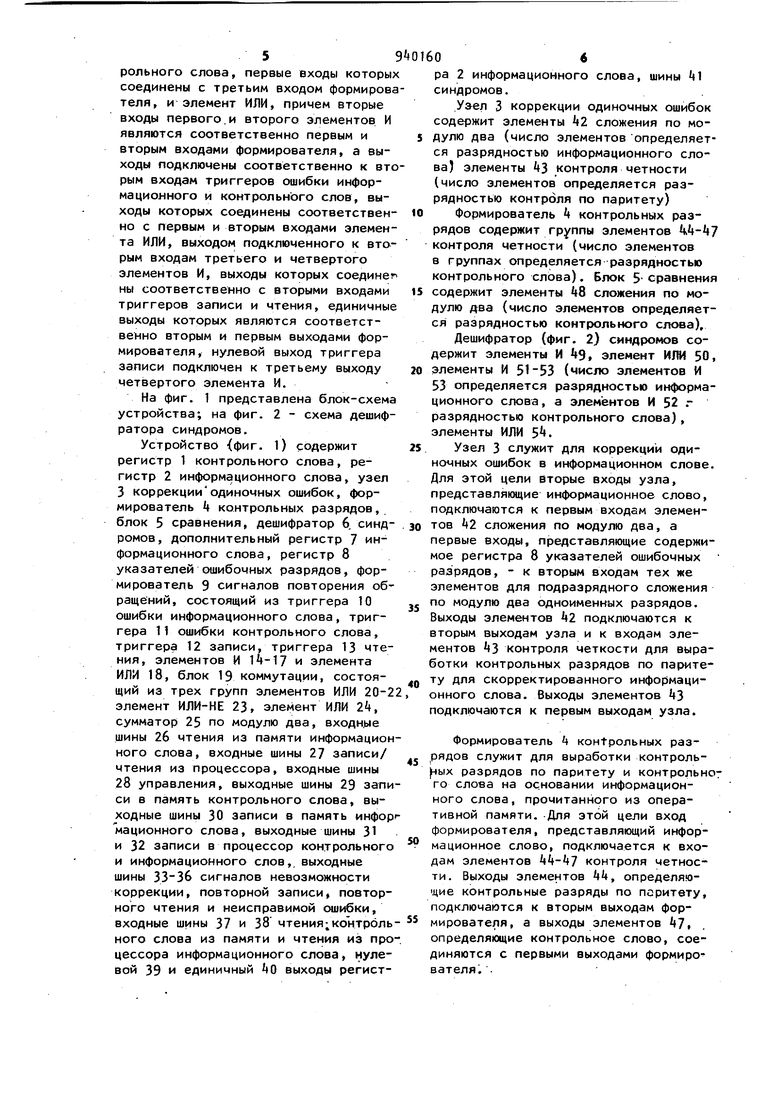

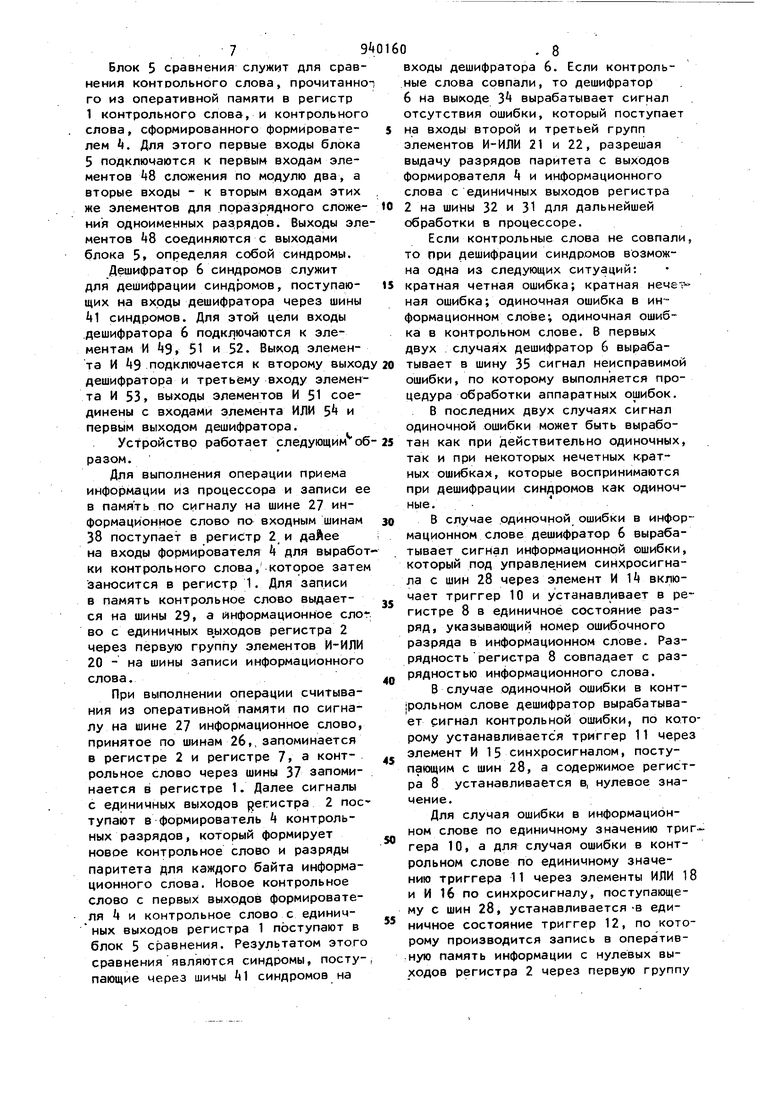

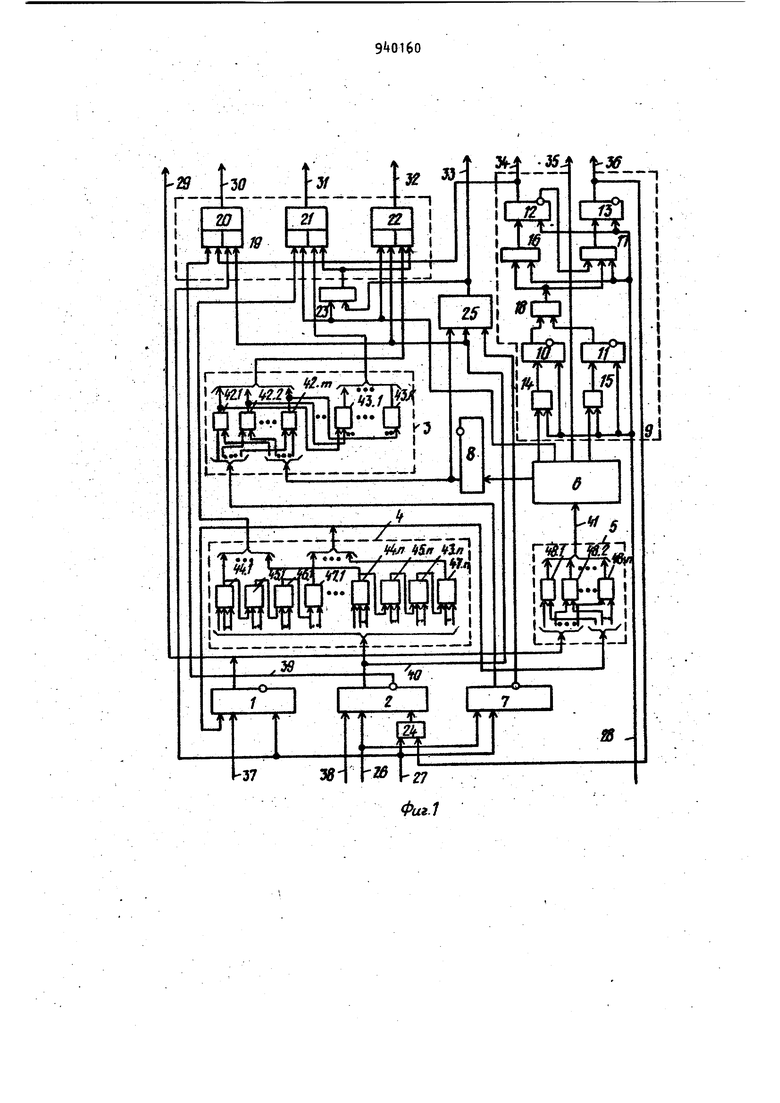

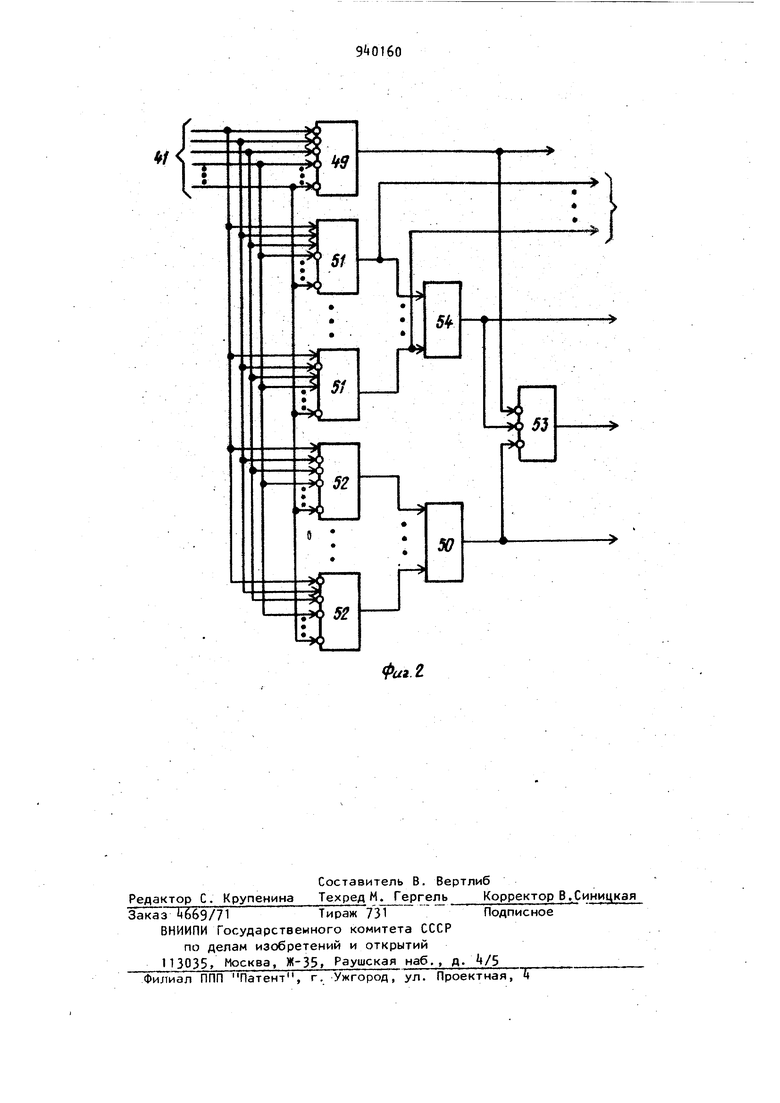

Изобретение относится к вымисли тельной технике и может быть исполь,зовамо в системах обработки информации. Известны устройства дляобнаружения ошибок в системах обработки, построенные на основе использования ко да Хэмминга, содержащие регистр конт рольного слова, регистр информационного слова, генератор контрольных разрядов, блок сравнения, дешифратор синдромов и корректор, связанные между собой информационными и управляющими шинами Р J. Недостатком указанных устройств является неспособность отличать одиночную ошибку от некоторых нечетных кратных ошибок, которые имеют синдромы, одинаковые, с одиночными ошибками. Это ведет к тому, что указанные нечетные кратные ошибки корректируются устройством как одиночные, и неверно скорректированная ии; формация поступает в процессор для продояжени:я операции. Наиболее близким к предлагаемому является устройство для обнаружения ошибок системы обработки данных, содержащее регистр контрольного слова, регистр информационного слова, генератор контрольных разрядов, блок сравнения, дешифратор синдромов, первые и вторые выходы которого подключены к контрольным шинам процессора и информационным, шинам процессора соответственно:, первый вход корректора подключен к первому амходу дешифратора синдромов, входы которого через шины синдромов подключены к выходам блока сравнения, первые входы которого соединены с единичными выходами регистра ,онтрольного слова, а вторые входы - с первыми выходами генератора контроль, ных разрядов, которые также заведены на третьи входы регистра контрольного слоёа, первые и вторые входы 39 которого подключены соответственно к шинам мтения контрольного слова и шинам записи-чтении, которые также подключены к второму входу регистра информационного слова, первые и третьи входы которого подключены к.шинам чтения информационного слова и входным шинам процессора соответственно, а единичный выход - к входу генератора контрольных разрядов и шинам записи информационного слова, а выход .регистра контрольного слова подключен к шинам записи контрольного слова Yj . Недостаток известного устройства состоит в ниакой достоверности efo работы, что обусловлено возможностью ложной коррекции кратных нечетных ошибок в информации, воспринимаемых как одиночные ошибки. Цель изобретения - повышение достоверности работы устройства. I Поставленная цель достигается тем что в устройство, содержащее регистр контрольного слова, первый и второй входы которого подключены соответственно к входным шинам чтения контрольного слова из памяти и входной шине записи/чтения из процессора устройства, выход - к шинам записи в- память контрольного слова устройства и первому входу бло ка сравнения, а третий вход - к второму входу блока сравнения и первому выходу формирователя контрольных разрядов, вход которого подключен к единичному выходу регистра информационного слова, первым и вторым входами соединенного соответственно с входными шинами чтения из процессора информационного слова и входными шинами чтения из памяти информационного слова, узел коррекции одиночных ошибок и дешифратор синдромов, соединенный входом с выходом блока срав нения, введены регистр указателей ошибочных разрядов, дополнительный регистр информационного слова, блок коммутации, сумматор по модулю два, формирователь сигналов повторения обращений, .элемент ИЛИ и элемент ИЛИ-НЕ, причем первый выход дешифратора синдромов через регистр указателей ошибочных разрядов подключен к первому входу узла коррекции одиночных ошибок, первый и второй выход которого соединены соответственно с первым и вторым входами блока ком0мутации, а второй вход - с единичным выходом дополнительного регистра информационного слова, первый второй входы и нулевой выход которого подключены соответственно к входной шине записи/чтения из процессора устройства , к входным шинам чтения из памяти информационного слова устройства и первому входу сумматора по модулю два, вторым входом подключенного к выходу регистра указателей ошибочных разрядов, третьим входом - к единичному выходу регистра информационного слова и трйтьему входу блока коммутации, а выходом - к первому входу элемента ; ИЛИ-НЕ и выходной шине невозможности коррекции устройства, второй выход дешифратора синдромов соедине 1 с вторым входом элемента ИЛИ-НЕ и четвертым входом блока коммутации, третий и четвертый выходы - соответственно с первым и вторым входами формирователя сигналов повторения обращений, а пятый выход - с выходной шиной сигнала неисправной ошибки, пятый вход блока коммутаций подключен к второму формирователя контрольных разрядов, шестой входк выходу элемента ИЛИ-НЕ, седьмой вход - к входной шине записи/чтения из процессора устройства и первому входу элемента ИЛИ, .восьмой вход к нулевому выходу регистра информационного слова, третий вход которого соединен с выходом элемента ИЛИ, вторым входом соединённого с выходной шинрй сигнала повторного чтения устройства и первым выходом формирователя сигналов повторения обращений, второй выход которого подключен к девятому входу блока коммутации и выходной шине сигнала повторной записи устройства,-а третий вход к входным шинам сигналов управления устройства, первый, второй и третий выходы блока коммутации соединены соответственно с выходными шинами записи в память информационного слова устройства, выходными шинами записи в процессор информационного слова устройства и выходными шинами записи в память контрольного слова, устройства. Формирователь сигналов повторения обращений содержит четыре элемента И, триггер записи, триггер чтения, триггер ошибки информационного слова и триггер ошибки контрольного слова, первые входы которых соединены с третьим входом формирова теля, и элемент ИЛИ, причем вторые входы первого.и второго элементов И являются соответственно первым и вторым входами формирователя, а выходы подключены соответственно к вто рым входам триггеров ошибки информационного и контрольного слов, выходы которых соединены соответственно с первым и вторым входами элемента ИЛИ, выходом подключенного к вторым входам третьего и четвертого элементов И, выходы которых соединен ны соответственно с вторыми входами триггеров записи и чтения, единичные выходы которых являются соответственно вторым и первым выходами формирователя, нулевой выход триггера записи подключен к третьему выходу четвертого элемента И. На фиг. 1 представлена блок-схема устройства; на фиг. 2 - схема дешифратора синдромов. Устройство {фиг. 1) содержит регистр 1 контрольного слова, регистр 2 информационного слова, узел 3 коррекцииодиночных ошибок, формирователь Ц контрольных разрядов, блок 5 сравнения, дешифратор 6. синдромов, дополнительный регистр 7 информационного слова, регистр 8 указателей ошибочных разрядов, формирователь 9 сигналов повторения обращений, состоящий из триггера 10 ошибки информационного слова, триггера 11 ошибки контрольного слова, триггера 12 записи, триггера 13 чтения, элементов И lA-17 и элемента ИЛИ 18, блок 19 коммутации, состоящий из трех групп элементов ИЛИ 20-2 элемент ИЛИ-НЕ 23, элемент ИЛИ 2, сумматор 25 по модулю два, входные шины 26 чтения из памяти информацион ного слова, входные шины 27 записи/ чтения из процессора, входные шины 28 управления, выходные шины 29 запи си в память контрольного слова, выходные шины 30 записи в память инфор мационного слова, выходные шины 31 и 32 записи в процессор контрольного и информационного слов, выходные шины сигналов невозможности коррекции, повторной записи, повторного чтения и неисправимой ошибки, входные шины 37 и 38 чтения;контроль ного слова из памяти и чтения из про цессора информационного слова, нулевой 39 и единичный iiO выходы регистра 2 информационного слова, шины k синдромов. Уаел 3 коррекции одиночных ошибок содержит элементы k2 сложения по модулю два (число элементов определяется разрядностью инфО(мационного слова) элементы 43 контроля четности (число элементов определяется разрядностью контроля по паритету) Формирователь k контрольных разрядов содержит группы элементов контроля четности (число элементов в группах определяется разрядностью контрольного слова). Блок 5- сравнения содержит элементы kB сложения по модулю два (число элементов определяется разрядностью контрольного слова). Дешифратор (фиг. 2) синдромов содержит элементы И kS, элемент ИЛИ 50, элементы И (число элементов И 53 определяется разрядностью информационного слова, а элементов И 52 .разрядностью контрольного слова), элементы ИЛИ Узел 3 служит для коррекций одиночных ошибок в информационном слове. Для этой цели Вторые входы узла, представляющие информационное слово, подключаются к первым входам элементов сложения по модулю два, а первые входы, представляющие содержимое регистра 8 указателей ошибочных разрядов, - к вторым входам тех же элементов для подразрядного сложения по модулю два одноименных разрядов. Выходы элементов 2 подключаются к вторым выходам узла и к входам элементов ЦЗ контроля четкости для выработки контрольных разрядов по паржтету для скорректированного информационного слова, выходы элементов 3 подключаются к первым выходам узла. Формирователь t контрольных разрядов служит для выработки контроль ых разрядов по паритету и контрольно: го слова на основании информационного слова, прочитанного из оперативной памяти. Для этой цели вход формирователя, представляющий информационное слово, подключается к входам элементов ЦЦ-Ц7 контроля четности. Выходы элементов k, определяющие контрольные разряды по поритету, подключаются к вторым выходам формирователя, а выходы элементов kj, определяющие контрольное слово, соединяются с первыми выходами формирователя. . Блок 5 сравнения служит для сравнения КОНТРОЛЬНОГО слова, прочитанно го из оперативной памяти в регистр 1 контрольного слова, и контрольного слова, сформированного формирователем Ц, Для этого первые входы блока 5 подключаются к первым входам элементов 8 сложения по модулю два, а вторые входы - к вторым входам этих же элементов для поразрядного сложения одноименных разрядов. Выходы эле ментов ЦВ соединяются с выходами блока 5 определяя собой синдромы. Дешифратор 6 синдромов служит для дешифрации синдромов, поступающих на входы дешифратора через шины 1 синдромов. Для этой цели входы дешифратора 6 подключаются к элементам И 9 51 и 52. Выход элемента И 9 подключается к второму выход дешифратора и третьему входу элемента И 53 выходы элементов И 51 соединены с входами элемента ИЛИ 5 и первым выходом дешифратора. Устройство работает следующим об

разом.

Для выполнения операции приема информации из процессора и записи ее в память по сигналу на шине 27 информационное слово по входным шинам 38 поступает в регистр 2 и даАее на входы формирователя 4 для выработки контрольного слова, которое затем заносится в регистр 1. Для записи в память контрольное слово выдается на шины 29 а информационное слог во с единичных вь1ходов регистра 2 через первую группу элементов И-ИЛИ 20 - на шины записи информационного слова.

При выполнении операции считывания из оперативной памяти по сигналу на шине 27 информационное слово, принятое по шинам 2б,, запоминается в регистре 2 и регистре 7 а контрольное слово через шины 37 запоминается в регистре 1. Далее сигналы с единичных выходов регистра 2 пос тупают 8 формирователь Ц контрольных разрядов, который формирует новое контрольное слово и разряды паритета для каждого байта информационного слова. Новое контрольное слово с первых выходов формирователя t и контрольное слово с единичных выходов регистра 1 поступают в блок 5 сравнения. Результатом этого сравнения являются синдромы поступающие через шины 1 синдромов на 9

так и при некоторых нечетных кратных ошибках, которые воспринимаются при дешифрации синдромов как одиночные.

В случае одиночной ошибки в информационном слове дешифратор 6 вырабатывает сигнал информационной ошибки, который под управле нием сийхросигнала с шин 28 через элемент И 1 включает триггер 10 и устанавливает в регистре 8 в единичное состояние разряд, указывающий номер ошибочного разряда в информационном слове. Разрядность регистра 8 совпадает с разрядностью информационного слова.

В случае одиночной ошибки в конт1рольном слове дешифратор вырабатывает сигнал контрольной ошибки, по которому устанавливается триггер 11 через элемент И 15 синхросигналом, поступающим с шин 28, а содержимое регистра 8 устанавливается в, нулевое значение.

Для случая ошибки в информационном слове по единичному значению триггера 10, а для случая ошибки в контрольном слове по единичному значению триггера 11 через элементы ИЛИ 18 и И 16 по синхросигналу, поступающему с шин 28, устанавливается-в единичное состояние триггер 12, по которому производится запись в оператив,ную память информации с нулевых выходов регистра 2 через первую группу 0 входы дешифратора 6. Если контрольные слова совпали, то дешифратор 6 на выходе 3 вырабатывает сигнал отсутствия ошибки, который поступает на входы второй и третьей групп элементов И-ИЛИ 21 и 22, разрешая выдачу разрядов паритета с выходов формирователя k и информационного слова с единичных выходов регистра 2 на шины 32 и 31 Для дальнейшей обработки в процессоре. Если контрольные слова не совпали, то при дешифрации синдромов возможна одна из следующих ситуаций: кратная четная ошибка; кратная нечечная ошибка; одиночная ошибка в информационном слове; одиночная ошибка в контрольном слове. В первых двух случаях дешифратор 6 вырабатывает в шину 35 сигнал неисправимой ошибки, по которому выполняется процедура обработки аппаратных ошибок. В последних двух случаях сигнал одиночной ошибки может быть выработан как при действительно одиночных. элементов И-ИЛИ 20. По завершению цикла записи синхросигналом, поступившим с шин 28, сбрасывается триггер 13 через элемент И 17« По едини ному состоянию триггера 13 происход чтение информации из оперативной па мяти на шины 28 и прием ее в регист 2. Далее содержимое регистра 2 с ед ничных выходов, содержимое регистра 7с нулевых выходов и содержимое ре гистра 8 складывается в сумматоре 2 Нулевой результат сложения указывает на действительно одиночную ошибку в информации, прочитанной из опе ративной памяти. Узел 3 корректирует ошибку по содержимому регистра 8 и выдает верную информацию через вторую и третью группы элементов И-ИЛИ.21 и 22 на шины 31 и шины 32 для дальнейшей обработки в процессо ре. Ненулевой результат сложения ука зывает на нечетную кратную ошибку в памяти, которая по виду синдромов максировалась под одиночную. В этом случае сумматор 25 вырабатывает сиг нал невозможной коррекции, по которому процессор выполняет процедуру обработки аппаратной ошибки. Таким образом, устройство позволяет выделять и корректировать толь ко одиночное ошибки и иск/иочает воз можность коррекции кратных нечетных ошибок, воспринимаемых по виду синдрома как одиночные. Это позволя ет повысить надежность обработки информации. Формула изобретения 1. Устройство для контроля и коррекции информации, содержащее регистр контрольного слова, первый и второй входы которого подключены соответственно к входным шинам чтения контрольного слова из памяти и входной шине записи/чтения из процессора устройства, выход - к выходным шинам записи в память конт рольного слова устройства и первому входу блока сравнения, а третий вход - к второму входу блока сравне ния и первому выходу формирователя контрольных разрядов, вход которого подключен к единичному .выходу регистра информационного слова, первым и вторым входами соединенного соответственно с ВХОДНЫМИ шинами чтения из процессора информационного слова и входными шинами чтения из памяти информационного слова, узел коррекции одиночных ошибок и дешифратор синдромов, соединенный входом с выходом блока сравнения,, отличающееся тем, что, с целью повышения достоверности работы устройства, в него введены регистр указателей ошибочных разрйдов дополнительный регистр информационного слов.а, блок коммутации, сумматор по модулю дваj формирователь сигналов повторения обращений, элемент ИЛИ- и элемент ИЛИ-НЕ, причем первый выход дешифратора синдромов через регистр указателей ошибочных разрядов подключен к первому выходу узла коррекции одиночных ошибок, первый и второй выходы которого соединены соответственно с первым и вторым входами блока коммутации, а второй вход - с единичным выходом дополнительного регистра информационного слова, первый, второй входы и нулевой выход которого подключены соответственно к входной шине записи/чтения из процессора устройства, к входным шинам чтения из памяти информационного слова устройства и первому входу сумматора по модулю два, вторым входом подключенного к выходу регистра указателей ошибочных разрядов, третьим входом к единичному выходу регистра информационного слова и третьему входу блока коммутации, а выходом - к первому входу элемента ИЛИ-НЕ и выходной шине невозможности коррекции устройства, второй выход дешифратора синдромов соединен с вторым входом элемента ИЛИ-НЕ и четвертым входом блока коммутации, третий и четвертый выходы - соответственно с первым и вторым входами формирователя сигналов повторения обращений, а пятый выход - с выходной шиной сигнала неисправимой ошибки, пятый вход блока коммутации подключен к второму выходу формирователя контрольных разрядов, шестой вход - к выходу элемента . ИЛИ-НЕ, седьмой вход - к входной шине записи/чтения из процессора устг ойства и первому входу элемента ИЛИ, восьмой вход - к нулевому выходу регистра информационного слова, третий вход которого соединен с выходом элемента ИЛИ, вторым входом соединенного с выходной шиной сигнала пов-. торного чтения у(,1роиства и первым выходом формирователя сигналов повторения обращений, второй выход которого подключен к девятому входу блока коммутации и выходной шине сигнала повторной записи устройства а третий вход - к входным шинам сиг налов управления устройства, первый второй и третий выходыьблока коммутации соединены соответственно с выходными шинами записи в .память информационного слова устройства, выходными шинами записи в процессор информационного слова устройства и выходными шинами записи в память контрольного слова устройства, 2. Устройство по п. 1, отличающееся тем, что формирова тель сигналов повторения обращений содержит четыре элемента И, триггер записи, триггер чтения, триггер оши ки информационного слова и триггер ошибки контрольного слова, первые входы которых соединены с третьим входом формирователя, и элемент ИЛИ причем вторые входы первого и вто012рого элементов И являются соответственно первым и вторым входами формирователя, а Выходы подключены соответственно к вторым входам триггеров ошибки информационного и контрольного слов, выходы которых соединены соответственно с первым и вторым входами элемента ИЛИ, выходом подключенного к вторым входам третьего и четвертого элементов И, выходы которых соединены соответственно с вторыми входами триггеров записи и чтения, единичные выходы которых являются соответственно вторым и первым формирователя, нулевой выход триггера записи подключен к третьему БУ ходу четвертого элемента И. Источники информации,, принятые во внимание при экспертизе 1.Вопросы радиоэлектроники. Серия ЭВТ вып. 10, 1978, с, 30-33. 2.Вопросы радиоэлектроники, Серия ЭВТ, вып. 11. 1977, с. 59-61 (прототип).

Авторы

Даты

1982-06-30—Публикация

1980-02-12—Подача