Изобретение относится к области вычислительной техники.

Известны цифро-аналоговые 1вычислительные управляющие устройства, содержащие блок пассивной памяти с подключенным к нему счетчиком-регистром значений аргумента, схему совпадений, блок оперативной памяти и сумматор, выход которого соединен со входами блока оперативной памяти и счетчика-регистра значений аргумента, а входы подключены через аналого-цифровой преобразователь к коммутатору входных сигналов и выходам блоков пассивной и оперативной памяти.

Иедостаток известных устройств заключается в том, что они имеют большой объем оборудования блока пассивной памяти.

Предложенное устройство отличается тем, что оно содержит счетчик-регистр приращений значений аргумента, входы которого соединены с выходами сумматора и блока оперативной памяти, а выходы через схему совпадений подключены к управляющему входу аналого-цифрового преобразователя, причем выход сумматора через цифро-аналоговый преобразователь соединен с одним из входов коммутатора входных сигналов и дополнительно введенным элементом нелинейной аппроксимации на каждом участке квантования.

например с конденсатором, вторая обкладка которого заземлена.

Это нозволило сократить требуемый объем нассивной памяти.

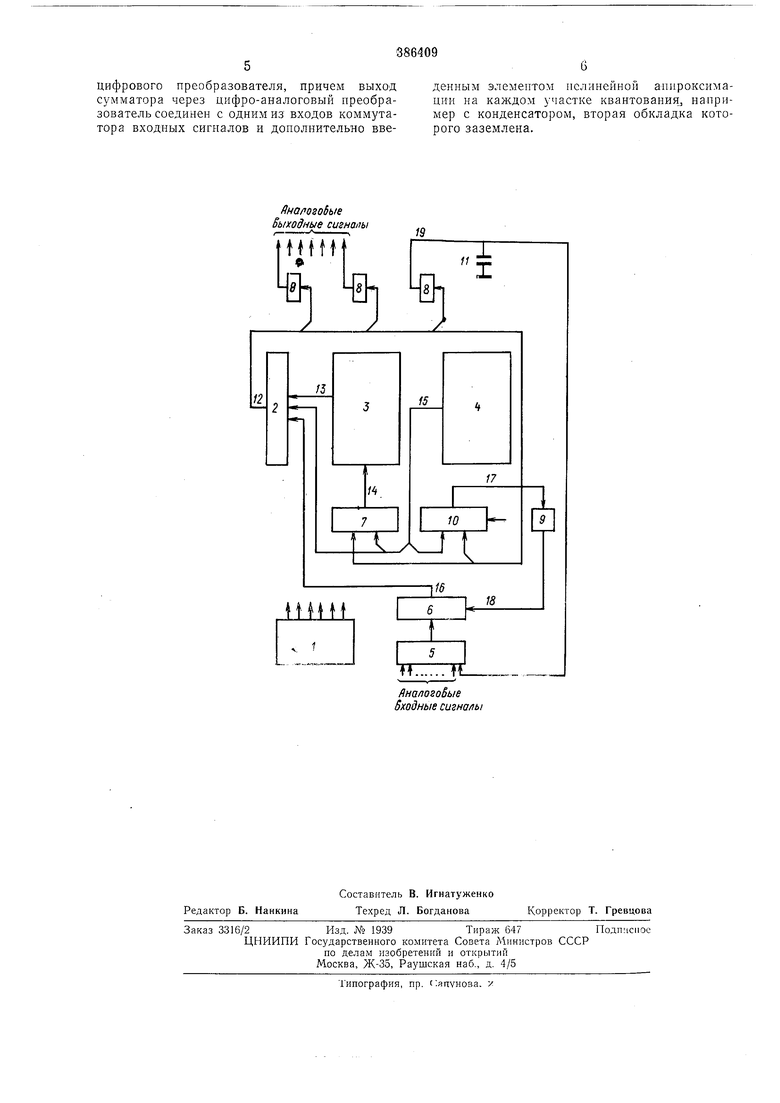

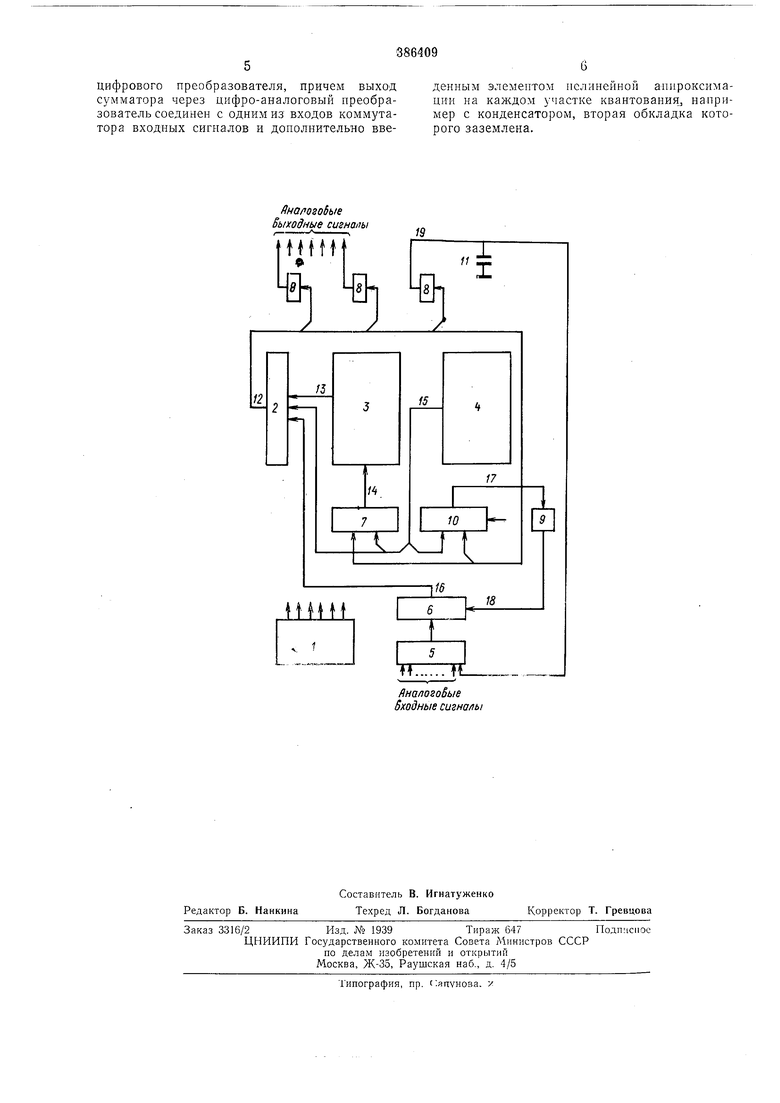

На чертеже приведена схема предлагаемого устройства.

Оно содержит блок управлеБИя 1, сумматор 2, блок 3 пассивной памяти, блок 4 оперативной памяти, коммутатор 5 аналоговых входных сигналов, аналого-цифровой преобразователь 6, счетчик-регистр 7 грубых значений аргумента, цифро-аналоговые преобразователи 8, схему совнадений 9, счетчик-регистр Ю цриращений аргумента, конденсатор 11 цифрами 12-19 обозначены основные связи, соединяющие соответствующие блоки устройства. Работа устройства состоит в следующем. Блок управления 1 вырабатывает последовательность сигналов, управляющих работой

всех остальных блоков и узлов устройства. Аналоговые входные сигналы, поступающие через коммутатор 5 на вход аналого-цифрового нреобразователя 6, преобразуются в нем в цифровую форму и затем подаются на сумматор 2. Затем осуществляется обработка поступивших входных сигналов в соответствии с заданным алгоритмом и рассчитанные величины регулирующих воздействий поступают на входы цифро-аналоговых преобразователей

8, выходы которых соединены неносредственно

со входами исполнительных устройств. Операции типа сложения, вычитания и другие осуществляются в сумматоре 2. Сложные операции ти.па умножения, деления, а также вычисления функций вида y f(x) (например, , , e,x и др.) осуществляются путем цифро-аналогового моделирования в соответствии с формулой:

y f(x) f(x,) + f(x),

где /(6, х) - функция, пропорциональная величине приращения аргумента бх.

При этом поведение функции на участке квантования Ал; (от Хо до ) моделируется во времени зарядом (разрядом) конденсатора 11, на который подается напряжение с выхода цифро-аналогового преобразователя 8, пропорциональное приращению искомой функции на рассматриваемом участке квантования

(o+l)-fW.

Коэффициент преобразования щага кваитования аргумента А.х во времени осуществляется изменением частоты имтульсов, подаваемых на вход счетчика-регистра 10 приращений аргумента. Частота устанавливается при настройке устройства (генератор импульсов па чертеже не показан).

При моделировании различных функций для повыщения точности моделирования могут использоваться различные участки кривой заряда (разряда) конденсатора 11. Для выполнения указанных выще операций и вычисления функций в блоке пассивной памяти имеется три таблицы грубых значений функций- логарифмов f(xo)log Хо; антилогарифмов / (хо) anti (log XQ) и синусов f (XQ)

Sin XQ.

Перед началом вычисленнй код аргумента х хо-{-8х, представленный грубым значением Хо и приращением бл: (соответственно старщие п-т разрядов и младщие т разрядов аргумента) подаются на входы счетчиков-регистров 7 м 10 соответственно. Код счетчикарегистра 7 представляет собой адрес ячейки блока 3, где хранится величина f(), например log Хо, которая считывается и подается на сумматор 2. Затем код счетчика-регистра 7 увеличивается на единицу младщего разряда и из блока 5 пассивной памяти на сумматор 2 поступает величина ,f(xo+l) (например, log(A;o+l). В сумматоре 2 вычисляется разность этих величин, т.е. определяется значение Д/ (Хо4-1) ), которое подается на вход одного из цифро-аналоговых преобразователей 8 (на чертеже расположен справа вверху), который в исходном состоянии очищен. На выходе цифро-аналогового преобразователя 8 устанавливается напряжение, пропорциональное величине Af. При этом начинается заряд конденсатора //и одновременно вычитание по «единице из счетчика-регистра 10, в котором находилась величина бх.

В момент очистки счетчика-регистра 10. который фиксируется схемой совпадений 9, аналого-цифровой преобразователь 6 измеряет значение напряжения на конденсаторе //, которое на период измерения для уменьшения динамической погрещности может фиксироваться аналоговым фиксатором (на чертеже не показан). Таким образом, определяется значение функции /(бх). Величина /(бх) с

выхода преобразователя 6 подается на вход сумматора 2, где вычисляется значение /(x)f(xo)+f(6).

Умножение и деление осуществляются с номощью таблиц логарифмов путем отыскания

логарифмов исходных величин (а, в. Затем

определяется величипа log(aXe) или log - и

S

антилогарифмирование описанным выще способом, за исключением того, что измерение значения /(бх) осуществляется при разрядке конденсатора 11. Для этого после подачи величины Af на вход преобразователя 10 происходит его очистка и начинается разряд конденсатора 11.

Ка,к видно из онисания работы схемы, погрещность вычислений лищь незначительно зависит от погрещности аналоговой части вычислителя. Для получення погрешности, равной «единице младшего разряда при представлении аргументов и функций 14-ю двоичными разрядами, достаточно иметь в блоке пассивной памяти таблицу 100 значений логарифмов (столько же значений антилогарифмов). Для вычисления функции оказывается также достаточным иметь 100 грубых ее значений при той же точности вычислений. При этом для получения указанной погрещности 2 требуется обеспечить относительную погрешность (в сумме) аналогоцифрового и цифро-аналогового преобразователей ие более от полной шкалы, что легко достигается.

Предмет изобретения

Цифро-аналоговое вычислительное управляющее устройство, содержащее блок пассивной памяти с подключенным к нему счетчиком-регистром значений аргумента, схему совпадений, блок оперативной памяти и сумматор, выход которого соединен со входами блока оперативной памяти и счетчика-регистра значений аргумента, а входы подключены через аналого-цифровой преобразователь к коммутатору входных сигналов и выходам блоков пассивной и оперативной памяти,, отличающееся тем, что, с целью сокращения

требуемого объема пассивной памяти, оно содержит счетчик-регистр приращений значений аргумента, входы которого соединены с выходами сумматора и блока оперативной памяти, а выходы через схему совпадений

подключены к управляющему входу аналогоцифрового преобразователя, причем выход сумматора через цифро-аналоговый преобразователь соединен с одним из входов коммутатора входных сигналов и дополнительно введенным элементом нелинейной анироксимации на каждом участке квантования, нанрнмер с конденсатором, вторая обкладка которого заземлена.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифро-аналоговое вычислительное устройство | 1973 |

|

SU441658A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1973 |

|

SU409226A1 |

| Вычислительное устройство | 1982 |

|

SU1040493A1 |

| Устройство для воспроизведения переменных во времени коэффициентов | 1981 |

|

SU1005087A1 |

| Устройство для вычисления полиномиальной функции от аналогового аргумента | 1990 |

|

SU1737444A1 |

| Цифровое вычислительное устройство | 1973 |

|

SU474012A2 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1273944A1 |

| Аппроксимирующий функциональный преобразователь | 1984 |

|

SU1205153A1 |

| Функциональный аналого-цифровой преобразователь | 1977 |

|

SU588626A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

йнапоаоЬые выходные сигна/ ы

Н...... t1

йнапогоЁые Входные сигналы

Авторы

Даты

1973-01-01—Публикация