1

Изобретение относится к области вычислительной техники и может быть использовано при построении цифровых универсальных-специализированных машин.

Известно цифровое вычислительное устройство но основному авт. св. № 409226, использующее при вычислении взаимообратных функций таблицы значений (соответствующих старшей части аргумента) только прямых функций, в том числе таблицы логарифмов, Таблица логарифмов используется при вычислении интерполяционной поправки функций.

Известное устройство имеет следующие недостатки: низкое быстродействие при вычислении значений функций в случае использования таблиц двоичных логарифмов нормализованного аргумента в связи с необходимостью предварительно нормализовать приращение функции и аргумента перед выборкой из таблицы соответствующих им логарифмов и дополнительно обрабатывать их характеристики при вычислении интерполяционной поправки, большое оборудование блока пассивной памяти и сумматора нрн вычислении значений функций в случае использования таблицдвоичных логарифмов ненормализованного аргумента, вызванное большим объемом этих таблиц и необходимостью дополнительно хранить

и обрабатывать характеристики логарифмов, кроме их мантисс.

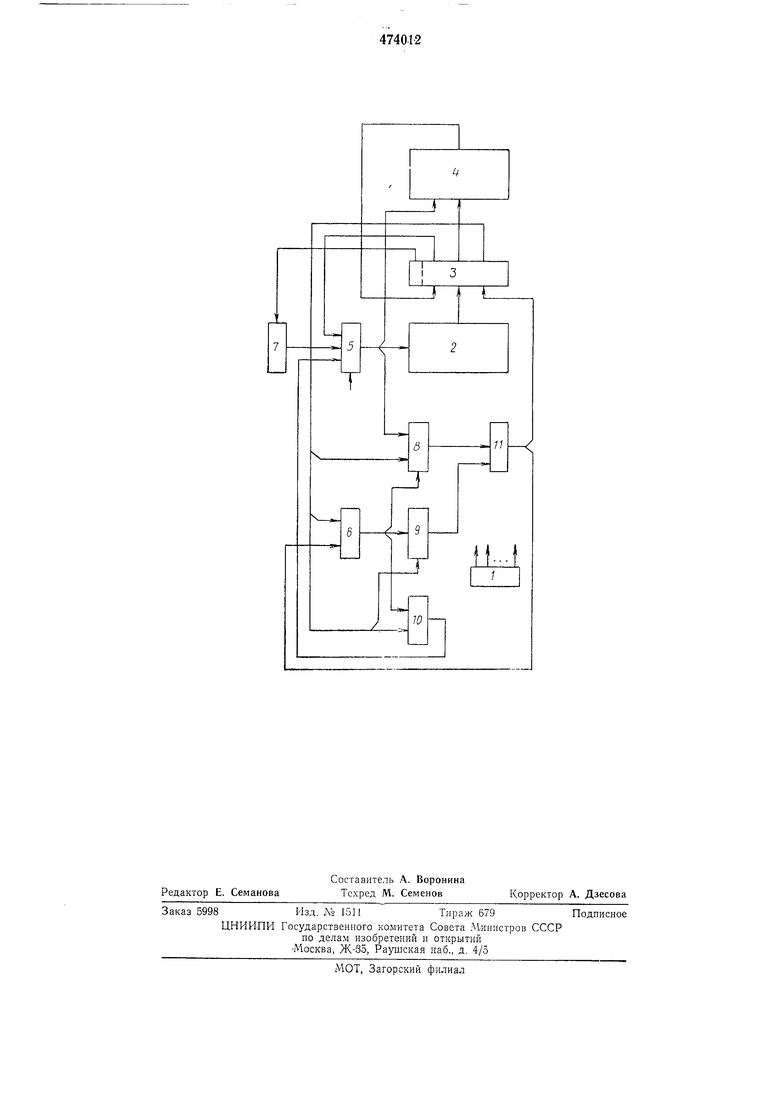

Это достигается тем, что в устройство введены два нор.малнзатора, в.ходы которых соединены с выходами регистра приращений и сумматора, денормализатор, входы которого подключены к выходам регистра грубых значений, сумматора и регистра приращений, регистр характеристики, входы которого соединены с выходом денормализатора и первого нормализатора, а выход соединен со входами сумматора и регистра приращений, причем выход второго нормализатора соединен со входом регистра грубых значений.

На чертеже представлена блок-схема устройства.

Оно состоит из блока управления 1, блока 2 пассивной памяти, сумматора 3, блока 4 оперативной памяти, регистра грубых значений аргумента 5, регистра приращений 6, раснределителя сигналов 7, денормализатора 8, нормализаторов 9 и регистра характеристики 11.

Нормализатор 10 реализует -разрядный сдвиг в сторону старщих разрядов числа, поступающего на один из его входов, где А-положение старшего, не равного нулю, разряда числа на входе нормализатора.

Нормализатор 9 реализует / -разрядный сдвиг в сторону старших разрядов числа, поступающего iia его вход, при этом /{-положение старшего, ие равного пулю, разряда второго числа па его входе. Денормализатор 8 |)еализуст /г-разрядиыи сдвиг в сторону младншх разрядов числа, ностунающего па одип пз его входов. При этом -ноложепие старпюго, не равного нулю, разряда числа на входе денормалпзатора 8. Прн вычислении зпачеинГ взаимообратных функции (прямой // -- J(х) н обратной .v Г (i/) псиользуется таблица грубоквантоваппых по аргу.мепту зпачепип одпоп из этих фупкцп| 1, папрп.мер, прямой фупкции, в том числе и таблица значений двоичных логариф.мов нор.мализоваппого аргумента. Последняя, кроме того, используется для вычисления иитерполяциоппо поправки всех функций (в том числе и мантиссы логарифма). Рассмотрим работу устройства при вычислении зпачепий прямых и обратпых (включая вычисление мантиссы функции х по маптиссе двоичного логарифма). Предполагается, что вычисляется значение функции по apryMeirry, являющемуся результатом предыдущей операции и содержащемся в сумматоре 3. Вычисления зпачепий прямых фупкциГ // - /(.г) вынолняются согласно алгоритму ( /(Л ,- ) + rexpaj log; Д/ (i -f 1 : t) 1 + og-2 J аргумента зпачепие где -Xj - rpyooe (старшие разряды), бл: - приращепие аргумента (младшие разряды), A/(i+l; г) - /(А-; +1) - /(л-; ) -- прираН1,ение функции на niare квантования аргумс та Л А . Аргумепт X из еумматора 3 передается в регистр 5 (грубое значение х } п в регистр 6 (приращепие б; V. Содержимое регистра 5 служит адресом, по которому из блока 2 выбирается соответствующее ему зпачепие функции п пересылается в сумматор 3 ц в одну из рабочих ячеек блока 4. После этого к коду регистра 5 прибавляется «1. Мз блока 2 выбирается значение функции, соответствующее содержимому регистра 5, и на сумматоре 3 определяется приращение функции Д/(г-Ь1; г ). Приращение функции А (г-Ы; О (младшие разряды сумматора 3) через нормализатор 10 (формируется величина --нересы/шется в регистр о, и одновреме)П1о через денормалпзатор 8 под унравленпем содержилц)го (бл-) регистра б иересылается в регистр 11. При этом положение старшего, не paBHoio пулю, разряда содержимого регистра 11 определяет величипу отрицательной характеристики ироизведеция: / (I -Ь 1; /) т. е. AV- /гр,д- + Сумматор 3 очищается, 1 ПО содержимому регистра 5 из блока 2 )егистра 5 f (i -.- 1 : о иа него выбирается значение iog2 2 V. , затем прпращепие аргумеита бх и:Г регистра б через норма.шзатор 10 (формируnepeci)i;iaстся в регнстр 5, по содержимому которого ,,, ПЗ блока 2 выоирается зиачение Iog2- . Лх Па сумматоре 3 определяется сумма мантисс логарифмов сомножителей произведения (2). В случае переполпеппя cy iмaтopa 3, т. е. еслп -/| 1, в сумматоре 3 остается его дробное содержимое п, кроме того, содержимое регистра 11 пересылается в регистр б со сдвигом па один разряд в сторопу старших разрядов. Если переполпепия сум.матора 3 не произошло, то содержимое регистра 11 пересылается в регнстр 6 без изменения. Содержимое сумматора 3 пересылается в одни из его приемных регистров (на чертеже не показап), регистр 5 оч нцается. Из распределителя 7 13 регистр 5 заиосится «1 старшего разряда, и соответственно ей (как по значению аргумента) из блока 2 выбирается зиачение логарифма и вычитается на сумматоре 3 их содержимого приемного регистра этого сумматора. Затем из распределителя 7 в регистр 5 заносится «1 следующего разряда, нри этом триггер старшего разряда регистра о остается в едипичном состоянии, если результат вычитания в суммагоре 3 положптелеп, и сбрасывается в нулевое состояние, если результат вычитания в су.мматоре 3 отрицателен. (Этот цроцесс ироизводится до перебора всех разрядов регистра 5). По окончапии этого процееса в регистре 5 содержится зпачепие мантиссы интерполяционпой поправки, соответствующее прирап1,ению аргумента 8х. Содержимое регистра 5 через денормализатор 8 под управлением содержимого регистра 6 (оиределяется произведение-- - &.Х / пересылается в регистр 11, а значение / (х-) из блока 4 оперативной памяти иересылается в предварительно очищенный е чмматор 3. Содержимое региетра 11 перссы.тается в .млад1пне разряды еумматора 3, где определяется З11ачецие фуикшп по.тпоразрядного apгy.Ieптa как сумма -V (i + 1;0 A.v

Результат остается в сумматоре 3 или пересылается в блок 4 оперативной памяти.

Вычисление зиачеиий обратных функцп| | .V /(//) ведется согласно пыражсипю:

I б(/ f (у) А-;-Ь Ал- ехр2 logg-;: -;Af (/+ 1;/)

-г log2

где Xf - старн ая часть ;л1ачспня ооратпой функции,

У У - /(,-) - прнращсине аргумента обратной функции,

+ - операция суммирования но модулю два.

Устройство работает следующим образодк

Аргумент у пересылается иа один из нриемпых регистров сумматора 3 (на чертеже не показан), регистр 5 очигцается.

Из распределителя 7 в регистр 5 заносится «1 старшего разряда, из блока 2 выбирается соответствующее значение прямой функции, которое вычитается иа сумматоре 3 из содержимого его прямого регистра. Затем из распределителя 7 в регистр 5 заносится «1 следующего разряда. Если результат вычитания в сумматоре 3 отрицателен, то триггер старшего разряда регистра 5 сбрасывается в нулевое состояние, если положителен, то остается в единичном состоянии. Этот процесс производится до перебора всех разрядов регистра 5. По окончании этого процесса в регистре 5 содержится значение старшей части обратной функции, т. е. х. Результат Х; из регистра 5 пересылается в блок 4 оперативной памяти, а приращение аргумента обратной функции бу (младшие разряды сумматора 3) пересылается в регистр приращений 6. Затем на сумматоре 3 определяется разность 4/ (г-г -fl ;() Эта разность (младшие разряды сумматора 3) через нормализатор 10 (формируетAf

J , 1 ) пересылается

ся величина , 2

Ало

в регистр 5 и одновременно приращение бг/ аргумента обратной функции (содержимое регистра 6) через нормализатор 9 под управлением содержимого младших разрядов сумматора 3 пересылается в регистр И. При этом положение старшего, не равного пулю, разряда содержимого регистра И определяет отрицательпую характеристику частного

бу . Af (гч- 1;0

(6)

Q

Дл:

т. е. /JQ kfjy - д/- Сумматор 3 очищается, по содержимому регистра 5 из блока 2 на

иего выбирается значение 1о 2- 7- 2 /Затем приращение 8у аргумента обратиой

функции из регистра 6 через нормализатор 10 (оиределяется величина - ) пересылается в регистр 5, но содержимому которого из блока 2 выбирается зиачение loga - 2С

н иа сумматоре 3 определяются разности мантисс двоичиых логариф.мов делимого и делителя, выражения (6). В случае отрицательного результата в су Л аторе 3. т. с. есл1

log 9 .:

Д-v

В сумматоре 3 определяется юдyль его содержимого и, кроме того, содержимое регистра 11 пересылается в регистр 6 со сдвигом па один разряд в сторону младших разрядов. Если результат в сумматоре 3 ноложителен, то содержимое регистра 11 пересылается в регистр 6 без сдвига. Содержимое сумматора 3 пересылается в один из его приемных регистров, а регистр 5 очищается. По замкнутому контуру: раснределитель 7 - регистр 5 - блок 8 - сумматор 3-в регистр 5 в результате последовательности операций «чтение - сравнение аналогично оиисанному выше подбирается значение мантиссы интерноляционой поправки, соответствующей приращению бг/ аргумента обратной функции. Содержимое регистра 5 через денормализатор 8 под управлением содержимого регистра 6 (определяется частное 6) пересылается в регистр 11. Из блока 4 оперативной памяти выбирается старшая часть значення обратной функции, а из регистра 11 - младшая, и и результате операции «сумма по модулю два на сумматоре 3 определяется нолноразрядное зпачение обратной функции.

3

(У) А-.-Ь(8)

A.v

дД/-- ;/)

Реззльтат пересылается в блок 4 оператпвной памяти или остается в сумматоре 3.

П р е д мет и з о б р е т е н и я

Цифровое вычислительное устройство но авт. ев. 409226, отличающееся тем, что, с целью повышения быстродействия, оно содержит два нормализатора, входы которых соединены с выходами регистра приращений и сумматора, денормализатор, входы которого подключены к выходам регистра грубых значений, сумматора и регистра приращений, регистр характеристики, входы которого соединены с выходом денормализатора и иервого нормализатора, а выход соединен со входами су.м.матора н регистра нриращений, нричем иыход второго нормализатора со входом регистра грубых значений.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1973 |

|

SU409226A1 |

| Устройство для возведения в степень | 1984 |

|

SU1228101A1 |

| Устройство для вычисления функций | 1985 |

|

SU1297038A1 |

| Цифровой генератор функции | 1977 |

|

SU711556A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА | 1991 |

|

RU2006916C1 |

| Устройство для логарифмирования двоичных чисел | 2015 |

|

RU2614932C1 |

| Цифровое устройство для логарифмирования двоичных чисел | 1976 |

|

SU593212A1 |

| Цифровое логарифмическое устройство | 1983 |

|

SU1101819A1 |

| Устройство для вычисления экспоненциальной функции | 1986 |

|

SU1465884A1 |

| Цифровое устройство для логарифми-РОВАНия дВОичНыХ чиСЕл | 1979 |

|

SU813414A2 |

Авторы

Даты

1975-06-15—Публикация

1973-06-25—Подача