1

Изобретение относится к области зычислител1яюи техники и может быть использовано ири создании цифровых универсальных и опеииализн1роваиных вычислительных машин.

Известна цифровая вычислительная машииа, исиользующая ири вы-числении функций (log.v, X и др.) таблицы из значений. Набор значений функций соответствует старшей части аргумента. Поправка, соответствующая младшей части аргумента (.приращению), определяется с иомоадью ли1ие|п-1ОЙ иптерлоляп,ии с исиол1530ванием того же органического 1абора значений функций логарифма и эксионеиты.

Однако это устройство имеет большой объем блока ;пасс1Рвиой в связи с необходнмостью хранить таблицы как для шрямых функций y f{x), так ц для обратных x F(y) U том случае, если требуется вычислять и ту и другую.

Устранение указанного недостатка является целью изобретения. Это достигается благодаря тому, что иредложенная маншпа имеет распре.делитель си.гналов, вход которого соединен с выходами триггера знака сумматора, а выход со входом регистра грубых значений, выходы которого соединены со входами блока оператизиой памяти и су.мматора.

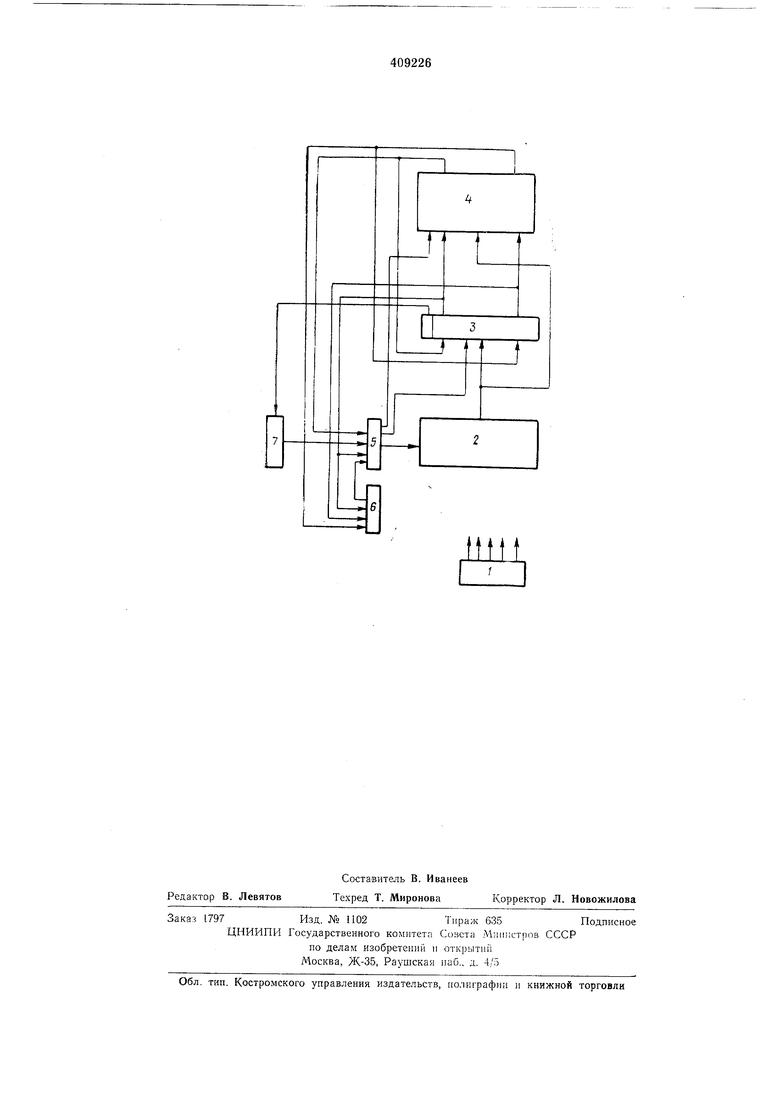

Схема предлагаемого устройства изображеиа иа чертеже.

2

Устройство состоит из блока у11равлеи 1я /, блока иассизной иамяти 2, сумматора о, блока онеративной памяти 4, регистра-счетчика грубых значений аргумента 5, регистра пр.иращений 6 и распределителя сигна.тов 7.

Блок 2 подключен своим} адреснымн входамн к выходам регистра-счетчика 5, а выходам} к сумматору 3 и к блоку 4. Последний своими входами соад}}неи также с выходами

сумматора 3, а выходам} со входал п сумматора о и входами регистра-счетчика 5 ц регистра 6. Регистр-счетчик 5 подключен входалп к выходам старшей разрядной части сумматора о, к 1выходам регистра 6 и расцределителя 7. Репгстр 6 входам: соеди} ен также с выходами сумматора 3, котор з Й подключен, кроме того, одним выходом ко выходу распредел теля 7. Регистр 5 соединеи также с сумматором о ц с блоком 4. Пр}1 вычислении i/ f(x) и обратной x F(y) функций используется таблица грубо квантованных по аргументу значений одной }13 этих функций, паири ер прямой функции.

Рассмотрим работу устройства на примере

в лчисления функций у 1о§х ц л , ечитая, что в блоке 2 хранятся таблицы значений фуикц-ий log Л . Для функции y ogx вычислеиня ведутся согласно выражен}1ю log.v --- log-Xi+exp(log(AlogA-)-f Ьдбд;-logA-v) (1)

где .Vj - грубо квантованные значения аргумента; бх - приращение аргумента; Alogx - приращение функции на шаге квантования аргумента; Л.х -:щаг кваитования аргумента. Устройство работает -следующим О(б1ра:зом. Из блока 4 аргумент х иересылается в регистры 5 и 6 (в регистр 5 - грубое значение аргумента (Xi)-a в регистр 6-значение ириращеиия аргумента (8х). Грубое значение аргумента служит адресом, ИО которому из блока 2 выбирается соответствующее ему значение .функции и пересылается в сумматор и в блок 4. После этого к концу регистра 5 прибавляется «единица его младшего разряда. Из блока 2 выбирается значение функции, соответствующее значению аргумента и на сумматоре 3 определяется разность Alog.r IogA-i+i -log.xi(2) Из регистра 6 .приращение аргумента б.г пересылается в реги1стр 5, а старшая часть вычисленного выражения (2) из сумматора 3 переводится в регистр 6. Из блока 2 выбирается значение логарифма, соответствующее коду регистра 5 (log()) и прибавляется к содержимому сумматора 3. В регистр 5 заносятся все «единицы из блока 4 (максимальиое зиачение ириращения аргумента), затем выбирается из блока 2 значение логарифма (logAx) и вычитается из содержимого сумматора. Старщая часть содержимого сумматора пересылается в один из приемных регистров сумматора (на чертеже не показан), а младшая часть сумматора и регистр и счищаются. Затем из распределителя 7 в регистр 5 заиосится «1 старшего разряда, и соответственно ей (как значение ар гумента) из блока 2 выбирается значение логарифма и вычитается на сумматоре из содержимого прпемного регистра сумматора. Если эта разность положительна, то из распределителя в регистр 5 заносится «1 следующего разряда, при этом триггер старщего разряда регистра 5 остается в «един ичном состоянии. Если Ж1: знак разности отрицательный, то из распределителя в регистр 5 заносится «Ь следующего разряда, а триггер старшего разряда регистра 5 сбрасывается в «нулевое состояние. Этот процесс идет до перебора всех разрядов регистра 5. По окончании процесса в регистре 5 содер.жится значеиие поправки, соответствующей приращению аргумента бл. Затем из блока 4 выбирается на сумматор значение log JCj, в младшую часть к нему прибавляется содержимое регистра 5. Результат переносится в блок 4 или остается на сумматоре. Для функции .г ехр г/ вычисления ведутся согласно выражению е.хр г/ л-,+ехр (logAA:-j-Iog(61og.v) (Alog.t))(3) Устройство работает следующим образом. Из блока 4 аргумеит (у иередается на один из приемных регистров сумматора 3. Затем КЗ раопределителя 7 в регистр 5 заносится « старшего разряда и соответственно ей из блока 2 выбирается значение логарифма, которое вычитается на сумматоре из со.держимого приемного регистра сумматора 3. Если эта разность иоложительна, то из распределителя 7 в регистр 5 заносится «1 следующего .разряда. При этом триггер старшего разряда регистра 5 остается в «единичном состоянии. Если же .знак разиости отрицателен, то из раоиределителЯ 7 в регистр 5 заносится «единица следующего разряда, а триггер старшего разряда сбрасывается в «нулевое состояние. Пи замкнутому контуру: распределитель 7, регистр 5, блок 2, сумматор 3 осуществляется подбор в регистре 5 значения старщей части функции ехр г/, т. е. х. Результат (л:|) из регистра5 иересылается в блок и остается на регистре. Старщие значащие цифры разности (о§,х щу-logA-,) из сумматора передаются в регистра. Соответственно значению числа в регистре 5 из 2 выбирается значение логарифма и передается в сумматор. Зате.м к содержимому регистра 5 прибавляется «едииица его младщего разряда и иа сумматоре определяется разность Alogx logХ; и-log..ri(4) Содержимое регист ра 6 передается в регистр 5, а старщие значащие цифры разиости (4) из су.мматора 3 передаются в регистр 6. I-is блока 2 соответственно содержимому регистра 5 выбирается на сумматор значение логарифма log(61ogA;). После этого из регистра 6 число пересылается в регистр 5 (Alog.v) и из блока 2 выбирается соответственное ему значение логарифма и вычитается из содержимого сумматора. Затем в регистр 5 заносятся все «единицы и ИЗ -блока 2 выбирается соответствующее значение .логарифма и прибавляется к содержимому сумматора 3. Старшая часть содержимого сумматора пересылается в один из его приемных регистров. По цепочке: распределитель 7, регистр 5, блок 2, сумматор 3 в регистре 5 подбирается значение экспоненты содержимого ириемиого регистра сумматора. Затем из блока 4 передается на сумматор значение -Vi и в младшую часть к нему ирпоавляется содержимое регистра 5. Результат переносится в блок 4 или остается на сумматоре. Аиалогичио описанному устройство позволяет вычислять прямые и обратные тригонометрические фуниции, иользуясь табли.цами только пря.мых тригонометрических функций, используя ири вычислеиия.х интериоляциоиной поправки таблицы логарифмов. Пред м е т и з о б р е т е и и я Цифровое вьгчислительное устройство но авт. св. ЛЬ 318031, отличающееся тем, что, с целью расширения функциональных возможностей устройства и иовышения его быстродействия, оно содержит ра-спределитель сигналов, вход которого соединен с выхода.ми триггера зна.ка сумматора, а выход - со входом регистра грубых значений, выходы которого соединены со входами блока оперативной памяти с мматс1па.

lilJt

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое вычислительное устройство | 1973 |

|

SU474012A2 |

| Цифровое устройство для логарифмирования двоичных чисел | 1976 |

|

SU593212A1 |

| Цифро-аналоговое вычислительное устройство | 1973 |

|

SU441658A1 |

| ЦИФРО-АНАЛОГОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УПРАВЛЯЮЩЕЕ | 1973 |

|

SU386409A1 |

| ЭС | 1973 |

|

SU369589A1 |

| Устройство для возведения в степень | 1984 |

|

SU1228101A1 |

| Устройство для вычисления корней | 1990 |

|

SU1751777A1 |

| Цифровое устройство для логарифми-РОВАНия дВОичНыХ чиСЕл | 1979 |

|

SU813414A2 |

| Функциональный преобразователь | 1988 |

|

SU1541629A1 |

| Устройство для вычисления функций двух аргументов | 1986 |

|

SU1413626A1 |

Авторы

Даты

1973-01-01—Публикация