1; - .

Изобретение относится к области вычислительной техннки.

Известна интеспральная матрица заио минающего устройсша, каждая ячейка которой последавательно включенные р-п-р-п диод и .резистОр и каждая из систем шин лаходиися на разных сторонах тела .матрицы.

Для обеспечения односторонней однослойной .азводки лрадлагается выполнить матрицу .на р-п-р-п диодах, имеющих продольную структуру с за1шунти1рова1Н1НЫм 1перехощ,ом рэмиттер-/г-ба.за, а одйу И|3 систем .шит выполнить в виде я+-0.5ласти в слое пнбазы.

Для упрощения 1Ко.нстру1Щ|Ии иредлагается в качестве iНагрузочного резистора фуйкционально использовать участок п-базы.

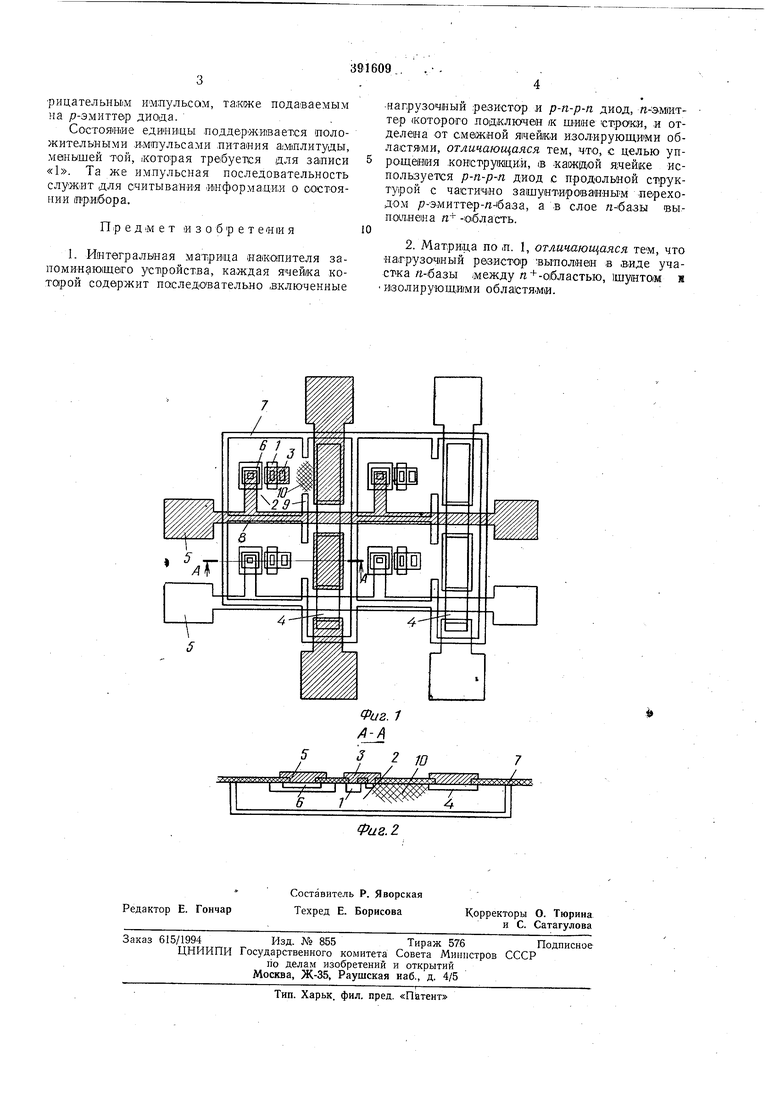

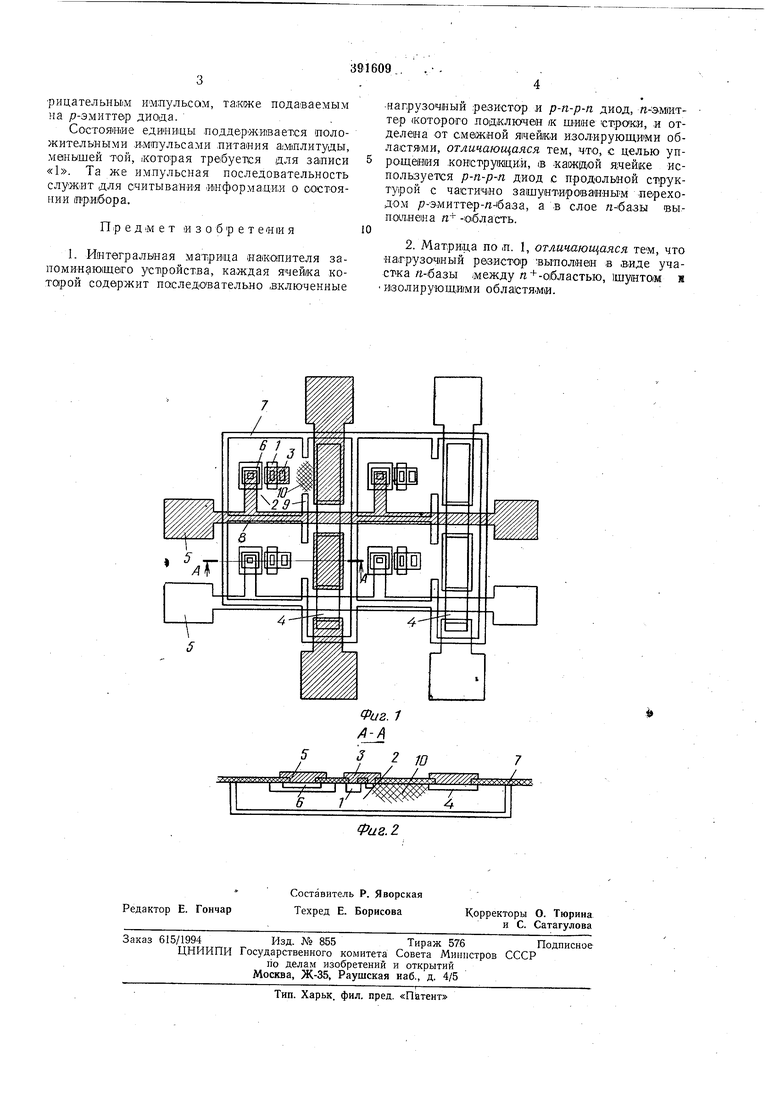

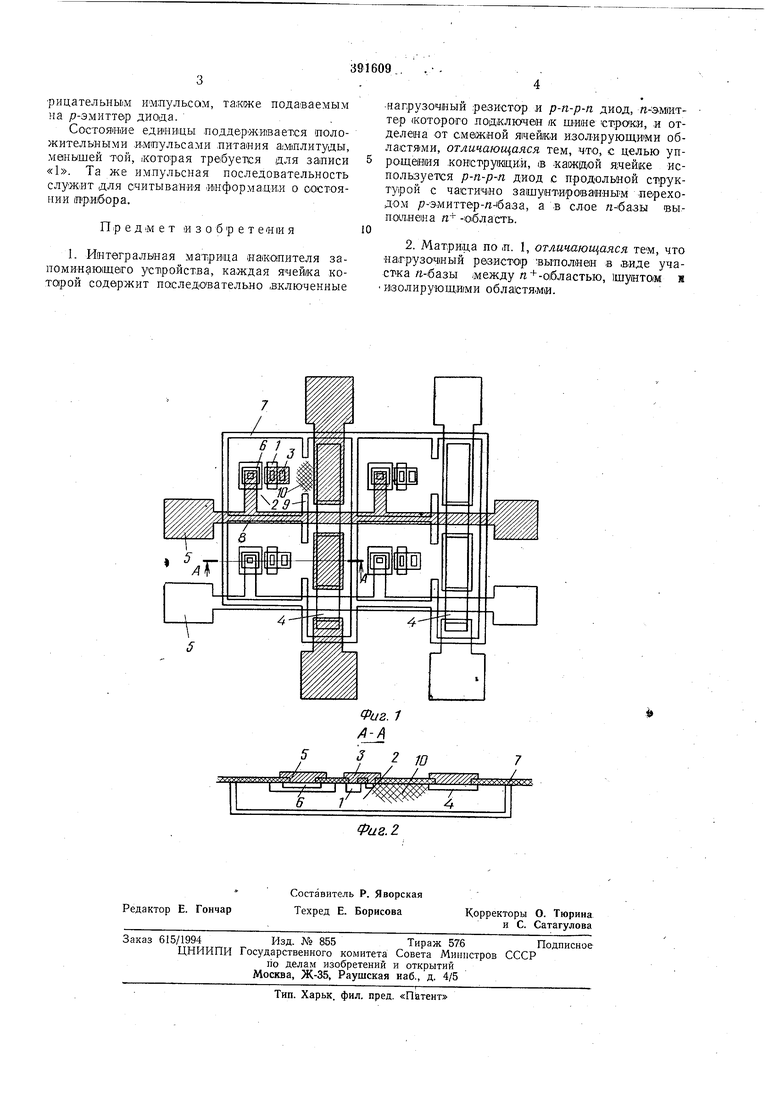

На фиг. 1 изО(бражвн эскиз топологии матрицы; на фиг. 2 - эакиз .поперечного сечения ОД1НОЙ ячейки .матрицы.

ячейка матрицы включает о-родольный р-п-р-п Д1ИОД, у которого переход рзмиттер /-лнбаза 2 зашу1Нти рО1ван резистором, o6ipai3DiBaiH:Hbi|M: .Мвталличеюкой перемычкой 3 и -резистором, образованным слоем 2 непосредственно под р-эмиттером 1. В слое л-.бавы 2 на некотором расстоянии от шунта 3 выполнена «+-область 4, служащая для контакта с уО-эм,иттером / и являющаяся шиной столбца матрицы.

Шина строки 5, ж .которой подсоединен пэмиттер 6, выполнена путем металлизации. Каждый столбец матрицы имеет общий изолирующий карман 7, профиль которого включает

отростки 8 и 5, позволяющие изолировать друг от друга ячейки внутри iKapMaaa и имеющие акна, служащие для ограничения о.бласти функционального нагрузо.чного --резистора, выполненного в виде участка 10 п-базы 2 между

я + -областью 4 и шунтом 3.

Поле матрицы обра.зуется мультипликацией .соответствующет-о чирла столбцов с необходимым количеством запаминающих р-п-р-п диодиых ячеек.

Спецификой работы продольного р-п-р-п диода с одним завшунтироварным эмиттерным переходом является тот факт, что работа прибора определяется соотношением зарядов на оставшихся незашунтированных переходах.

Р-п-р-п диод может находиться в двух состояниях - с бельш.им порогом В1клю1чения-и с малым порогом включения. Состояние с малым поро.гом включения соответствует «1, состояние с большим порогом включения «О.

За.пись «1 осуществляется импульсом положительной полярности, подаваемым на шину столбца, к которой через р-езистор подключен /и-эмиттер четырехслойното диода.

Стирание (запись «О) осуществляется отрицательным импульсом, также подаваемым на уо-эмиттер диода.

Состояяие единиады поддерживается положительными ймиульсами питания амплитуды, меньшей той, жоторая требуется для записи «1. Та же импульсная последовательность служит для считывания информацни о состоянии (Прибора.

П .р е д им е т и з о б р е т е « и я

1. Интегральная матрица иакапителя запомИНаЮ1щего уст1ройства, каждая ячейка которой содержит последовательно лключенные

нагрузочный .резистар и р-п-р-п диод, тг- эмиттер (Которого подключен /к шине строки, .и отделена от смежной янейк.и изолирующими областями, отличающаяся тем, что, с целью упрощения ,конст1ру1К1ци,и, iB -каждой ячейке используется р-п-р-п диод с продольной структурой с частично зашунтировакньш переходом р-эмиттер-/г-база, а в слое п-ба.зы свыиал.не1на л+ -область.

2. Матрица по л. 1, отличающаяся тем, что нагрузочный резистор -выполнен в .виде участка л-б азы между « + -0|бластью, 1щуито1М и изолирующими областями.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU360693A1 |

| Оптический транспарант | 1989 |

|

SU1647649A1 |

| Интегральный нейрон | 1981 |

|

SU1074345A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ | 1972 |

|

SU434481A1 |

| Накопитель | 1989 |

|

SU1656595A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПЕРЕДАЧИ ГРАФА | 1970 |

|

SU259495A1 |

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

| Запоминающее устройство | 1985 |

|

SU1256097A1 |

| Интегральная схема быстродействующего матричного приемника оптических излучений | 2015 |

|

RU2617881C2 |

Авторы

Даты

1973-01-01—Публикация