1

Изобретение относится к вычислительной технике и -может быть применено в запоминающих устройствах (ЗУ выполненных на биполярш гх запомицаю щих транзисторах.

Цель изобретения - повышение быстродействия устройства.

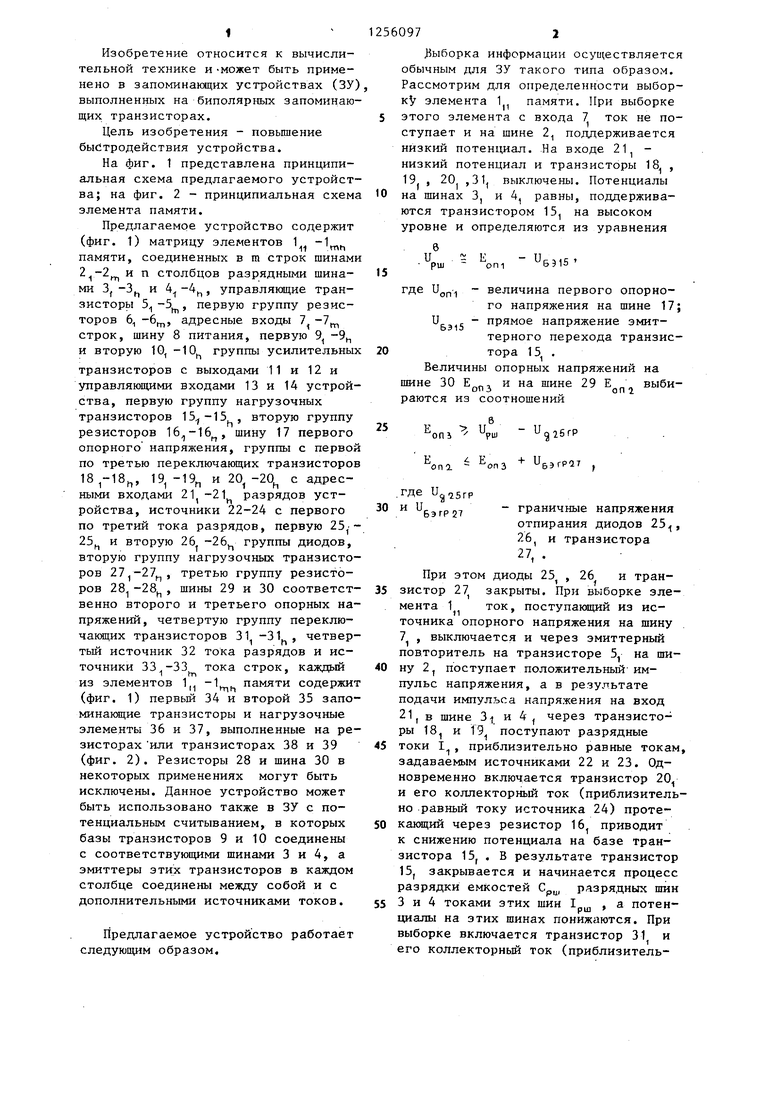

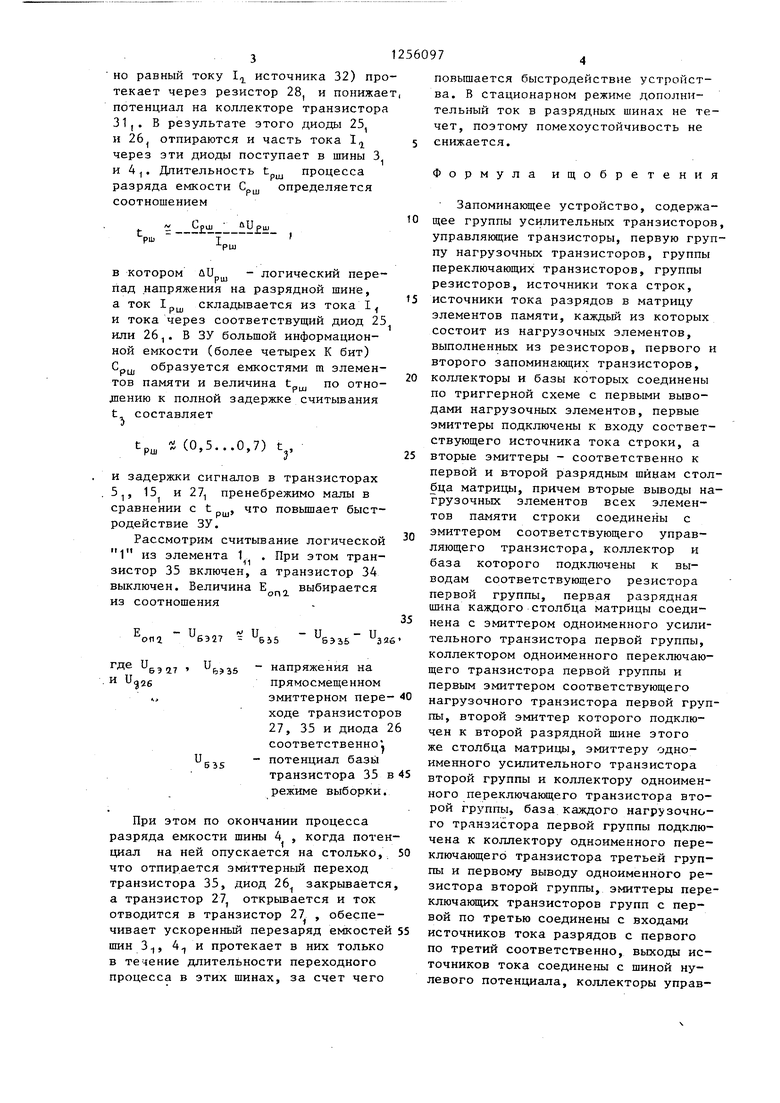

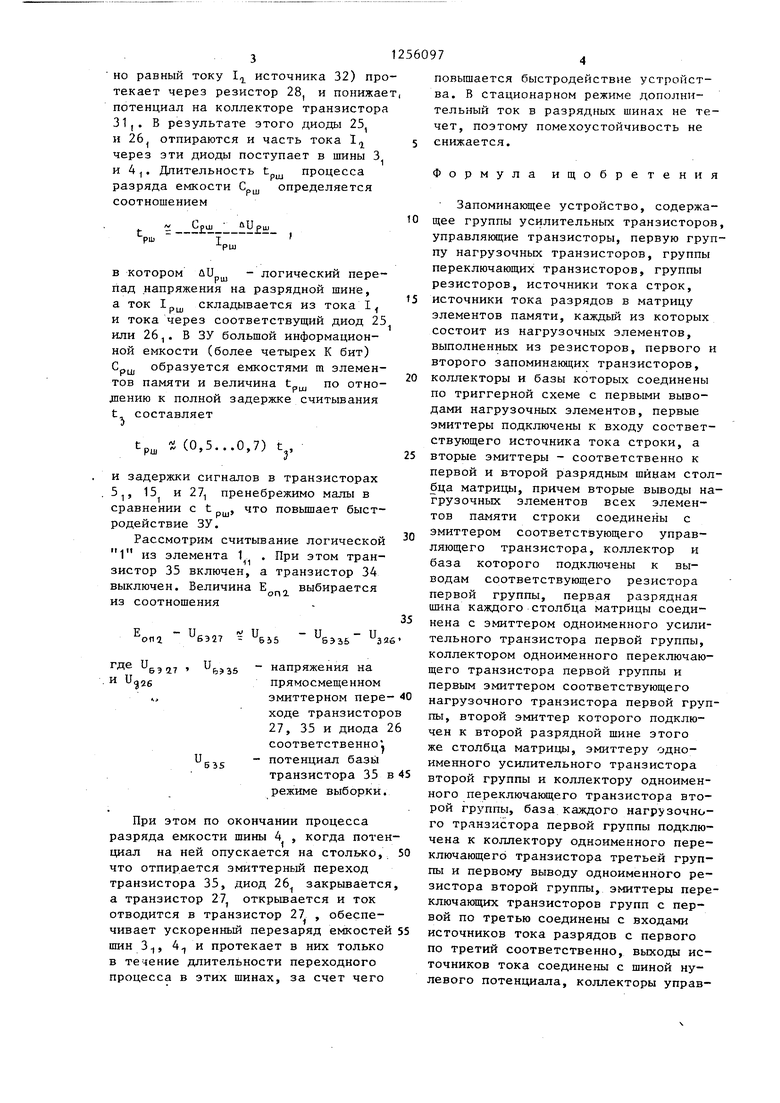

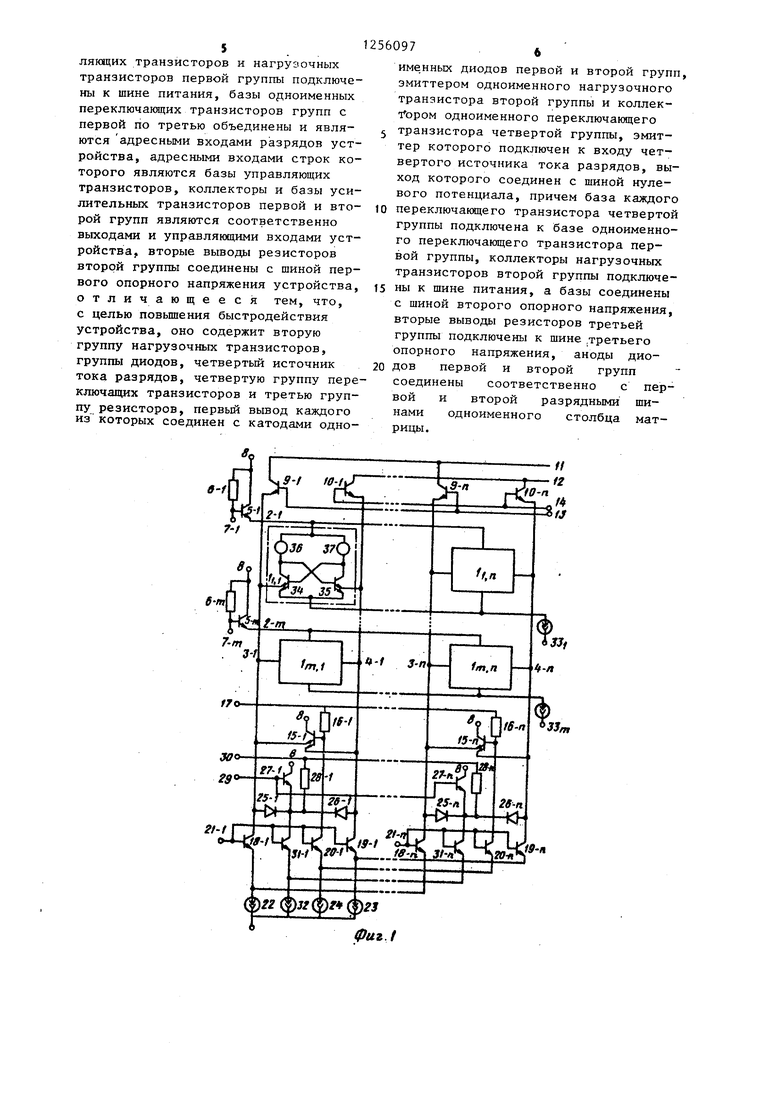

На фиг. 1 представлена принципиальная схема предлагаемого устройства; на фиг. 2 - принципиальная схем элемента памяти.

Предлагаемое устройство содержит (фиг. 1) матрицу элементов 1 -1, памяти, соединенных в m строк шинам и п столбцов разрядными шинами 3j -3 и 4 -4|, управлякщие транзисторы 5 -5|, первую группу резисторов 6 ( адресные входы 7 -7, строк, шину 8 питания, первую 9, -9 и вторую 10, -10 группы усилительны

транзисторов с выходами 11 и 12 и управляющими входами 13 и 14 устройства, первую группу нагрузочных транзисторов , вторую группу резисторов , шину 17 первого опорного напряжения, группы с перво по третью переключающих транзисторо 18,-18,, 19, -19 и с адресными входами 21, 21 разрядов устройства, источники 22-24 с первого по третий тока разрядов, первую 25, 25 и вторую 26 -26 группы диодов, вторую группу нагрузочных транзисторов 27,-27, третью группу резисторов 28, -28, шины 29 и 30 соответственно второго и третьего опорных напряжений, четвертую группу переклю- чакицих транзисторов 31, 31, четвертый источник 32 тока разрядов и источники 33.-33 тока строк, каждый 1 п

из элементов 1,, -1 памяти содержи (фиг. 1) первьш 34 и второй 35 запоминающие транзисторы и нагрузочные элементы 36 и 37, выполненные на резисторах или транзисторах 38 и 39 (фиг. 2). Резисторы 28 и шина 30 в некоторых применениях могут быть исключены. Данное устройство может быть использовано также в ЗУ с потенциальным считыванием, в которых базы транзисторов 9 и 10 соединены с соответствующими шинами 3 и 4, а эмиттеры этих транзисторов в каждом столбце соединены между собой и с дополнительными источниками токов.

Предлагаемое устройство работает следующим образом.

ыбopкa информации осуществляется обычным для ЗУ такого типа образом. Рассмотрим для определенности выбор- KV элемента 1,, памяти. При выборке

этого элемента с входа 7 ток не поступает и на шине 2, поддерживается низкий потенциал. На входе 21, - низкий потенциал и транзисторы 18, , 19 , 20 ,31, выключены. Потенциалы

на шинах 3, и 4, равны, поддерживаются транзистором 15, на высоком уровне и определяются из уравнения

6

% оп1

где Uдp,, - величина первого опорного напряжения на шине 17; и , - прямое напряжение эмитЬЭ10

терного перехода транзистора 15, .

Величины опорных напряжений на шине 30 и на шине 29 Е выбираются из соотношений

опь 6

- pu)

- и

опа

6 Е

опз

+ и

glSrP

бэграт

.где и,5гр

и и

бэгр 27

- граничные напряжения отпирания диодов 25.,,

26,и транзистора

27,.

При этом диоды 25 , 26 и транзистор 27, закрыты. При выборке элемента 1 ток, поступакяций из источника опорного напряжения на шину 7, , выключается и через эмиттерный повторитель на транзисторе 5, на шину 2, поступает положительный импульс напряжения, а в результате подачи импульса напряжения на вход 21, в шине 3i и 4, через транзисторы 18, и 19 поступают разрядные

токи 1, приблизительно равные токам, задаваемым источниками 22 и 23. Одновременно включ;ается транзистор 20., и его коллекторный ток (приблизительно равный току источника 24) протекающий через резистор 16, приводит к снижению потенциала на базе транзистора 15, . В результате транзистор 15, закрывается и начинается процесс разрядки емкостей Ср, разрядных шин

3 и 4 токами этих шин I , а потенциалы на этих шинах понижаются. При выборке включается транзистор 31 и его коллекторньй ток (приблизительно равный току 1 источника 32) протекает через резистор 28, и понижает потенциал на коллекторе транзистора 31,. В результате этого диоды 25, и 26. отпираются и часть тока 1 через эти диоды поступает в шины 3 и 4 ,. Длительность tp, процесса разряда емкости соотношением

рш

рш

определяется

аи

-

рш

-рш

в котором uU - логический пере1 25.

пад напряжения на разрядной шине, а ток Ipi складывается из тока I и тока через соответствущий диод или 26,. В ЗУ большой информационной емкости (более четырех К бит) С„,„ образуется емкостями m элемен-рш

тов памяти

и величина t

рш

по отнодпению к полной задержке считывания

составляет

РШ

(О,5...О,7) t

задержки сигналов в транзисторах

15. и 27, пренебрежимо малы в

что повьппает быст1 , ,, сравнении с t р, родействие ЗУ.

Рассмотрим считывание логической . При этом тран- а транзистор 34 выключен. Величина Е. выбирается из соотношения

1 из элемента 1. зистор 35 включен,

- и

де и

опа UB.T

926

6Э27

ri и

Б55

- б..5- за.

и

6 35

63S

напряжения на прямосмещенном эмиттерном пере- 40 ходе транзисторов 27, 35 и диода 26 соответственно: потенциал базы транзистора 35 в 45 режиме выборки.

При этом по окончании процесса

разряда емкости шины

когда потен

циал на ней опускается на столько, что отпирается эмиттерный переход транзистора 35, диод 26 закрывается а транзистор 27, открьшается и ток отводится в транзистор 27 , обеспечивает ускоренный перезаряд емкостей шин 3, 4 и протекает в них только в течение длительности переходного процесса в этих шинах, за счет чего

т,

10

.

15

20

25

30

35

.

- 40 ов 26 в 45 .

н50

я, й 55

повышается быстродействие устройства. В стационарном режиме дополнительный ток в разрядных шинах не течет, поэтому помехоустойчивость не снижается.

Формула ищобретения

Запоминающее устройство, содержащее группы усилительных транзисторов, управлякнцие транзисторы, первую группу нагрузочных транзисторов, группы переключающих транзисторов, группы резисторов, источники тока строк, источники тока разрядов в матрицу элементов памяти, каждый из которых состоит из нагрузочных элементов, выполненных из резисторов, первого и второго запоминакицих транзисторов, коллекторы и базы которых соединены по триггерной схеме с первыми выводами нагрузочных элементов, первые эмиттеры подключены к входу соответствующего источника тока строки, а вторые эмиттеры - соответственно к первой и второй разрядным шинам столбца матрицы, причем вторые выводы нагрузочных элементов всех элементов памяти строки соединены с эмиттером соответствующего управляющего транзистора, коллектор и база которого подключены к выводам соответствующего резистора первой группы, первая разрядная шина каждого столбца матрицы соединена с эмиттером одноименного усилительного транзистора первой группы, коллектором одноименного переключающего транзистора первой группы и первым эмиттером соответствующего нагрузочного транзистора первой группы, второй эмиттер которого подключен к второй разрядной шине этого же столбца матрицы, эмиттеру одноименного усилительного транзистора второй группы и коллектору одноименного переключающего транзистора второй группы, база каждого нагрузочного транзистора первой группы подключена к коллектору одноименного переключающего транзистора третьей группы и первому выводу одноименного резистора второй группы, эмиттеры пере- ключакяцих транзисторов групп с первой по третью соединены с входами источников тока разрядов с первого по третий соответственно, выходы источников тока соединены с шиной нулевого потенциала, коллекторы управлягацих транзисторов и нагрузочных транзисторов первой группы подключены к шине питания, базы одноименных переключакяцих транзисторов групп с первой по третью объединены и являются адресными входами разрядов устройства, адресными входами строк которого являются базы управляющих транзисторов, коллекторы и базы усилительных транзисторов первой и второй групп являются соответственно выходами и управляющими входами устройства, вторые выводы резисторов второй группы соединены с шиной первого опорного напряжения устройства, отличающееся тем, что, с целью повьшения быстродействия устройства, оно содержит вторую группу нагрузочных транзисторов, группы диодов, четвертый источник тока разрядов, четвертую группу пере ключащих транзисторов и третью группу резисторов, первый вывод каждого из которых соединен с катодами одноименных диодов первой и второй групп, эмиттером одноименного нагрузочного транзистора второй группы и коллек- т ором одноименного переключающего

транзистора четвертой группы, эмиттер которого подключен к входу четвертого источника тока разрядов, выход которого соединен с шиной нулевого потенциала, причем база каждого

переключающего транзистора четвертой группы подключена к базе одноименного переключающего транзистора первой группы, коллекторы нагрузочных транзисторов второй группы подключены к шине питания, а базы соединены с шиной второго опорного напряжения, вторые выводы резисторов третьей группы подключены к шине .третьего опорного напряжения, аноды диодов первой и второй групп

соединены соответственно с первой и второй разрядными шинами одноименного столбца матрицы.

e-f

iO

фиг.1

Составитель Т.Зайцева Редактор А.Сабо Техред А.Кравчук

Заказ 4830/52 Тираж 543Подписное

ВНИШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская.наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,А

фиг. 2

Корректор Л.Пилипенко

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Запоминающее устройство | 1985 |

|

SU1305774A2 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

| Усилитель записи-считывания | 1986 |

|

SU1437913A1 |

| Устройство для обращения к памяти (его варианты) | 1982 |

|

SU1092561A1 |

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1689991A1 |

| Запоминающее устройство | 1986 |

|

SU1361630A1 |

| Формирователь уровня считывания | 1984 |

|

SU1244718A1 |

Изобретение .относится к вычислительной технике, в частности к интегральным запоминающим устройствам на биполярных транзисторах. Целью изобретения является повьшение быстродействия запоминающего устройства. (ЗУ). ЗУ содержит матрицу элементов памяти на биполярных транзисторах, две группы усилительных и первую группу нагрузочных транзисторов, источники тока строк и управляющие транзисторы, служащие для выборки строк, три группы переключающих транзисторов, и три источника тока, служащие для выборки разрядов. Кроме того, в устройство введены вторая группа нагрузочных транзисторов, третья группа резисторов, четвертая группа переключающих транзисторов, две группы диодов, создамцих форсированный режим перезаряда емкостей разрядных шин, и четвертый источник тока разрядов, создающий дополнительный ток в разрядных пшнах устройства. Поскольку дополнительный ток протекает только в течение форсированного режима переходного процесса перезаряда емкостей разрядных шин, время выборки снижается. Помехоустойчивость ЗУ не снижается, так как в стационарном режиме дополнительный ток в вибирае- мьй элемент памяти не течет. 2 ил. сл NP сл О) о ;о

| Электронная техника | |||

| Сер | |||

| Микроэлектроника, 1975, вып.З, с.15 | |||

| IEEE J | |||

| of Solid State Sircuits, 1983, № 5, p.515. |

Авторы

Даты

1986-09-07—Публикация

1985-01-21—Подача