Изобретение относится к области телеграфной связи, а именно к устройствам фазирования псевдослучайных последовательностей, образованных путем сложения по модулю два ряда рекуррентных последовательностей, сформированных в п регистрах с логическими обратными связями.

Известны устройства фазирования псевдослучайных последовательностей, содержащие узел проверки соответствия принимаемой последовательности закону формирования, узел коррекции ошибок и узел .включения, обеспечивающий обнаружение неискаженного участка последовательности и включение узла коррекции ошибок. Однако такие устройства теряют фазу при .наличии в канале ошибок.

Цель изобретения - удержание цравильнюй фазы при наличии ошибок.

Это достигается тем, что в предлагаемом устройстве схема коррекции ошибок своими выходами, соответствующими каждому регистру с логическими обратными связями, включена между входом устройства и выходом каждого из п регистров с логическими обратными связями. Выход каждого из п сумматоров по модулЮ два подсоединен к соответствующему входу схемы коррекции ошибок, начиная со второго, а к первому входу схемы коррекции ошибок нодключен выход схемы

Включения. К входу последней подсоединен выход л-го сумматора по модулю два.

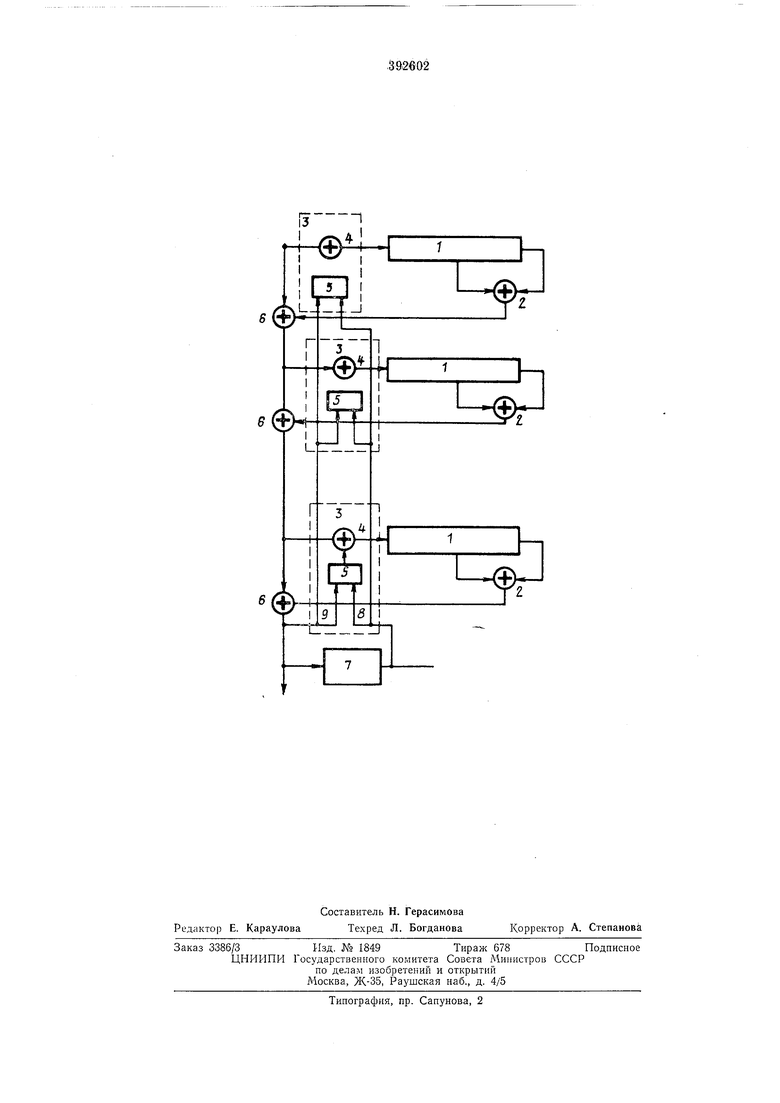

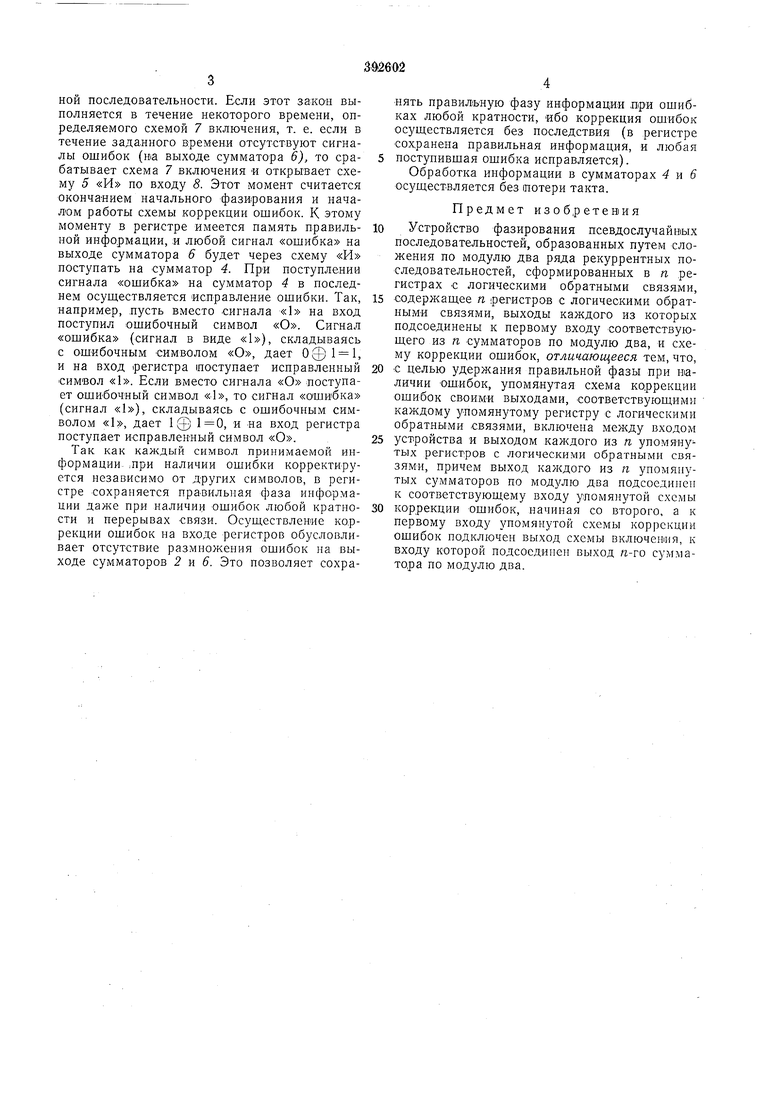

На чертеже приведена блок-схема предлагаемого устройства.

Устройство фазирования псевдослучайных последовательностей содержит п регистров 1 с логическими обратными связями на сумматор 2 по модулю два, схемы 3 коррекции ошибок, состоящие из сумматоров 4 по модулю

два и схем 5 «И, п сумматоров 6 по модулю два и схему 7 включения.

Когда схема 3 коррекции ошибок выключена (с начала работы), т. е. на входе 8 схемы «И разрешающий сигнал отсутствует, то сигнал «ошибка, поступающий на вход 9 схемы «И, не проходит на ее выход. Поэтому на выходе схемы «И сигнал коррекции ошибок отсутствует. При отсутствии сигналов .на выходе схемы «И сумматор 4 пропускает входную

информацию на вход регистра 1 (если входная информация соответствует Б данный момент сигналу «1, то если входная информация «О, то 000 0, так как на выходе схемы «И сигнал «О).

Таким образом, входная информация (при включенной схеме коррекции ошибок), без изменений поступает в регистр 1.

В регистре 1, сумматорах 2 6 осуществляется проверка соответствия принимаемой информации закону формирования рекуррентной последовательности. Если этот закон выполняется в течение некоторого времени, определяемого схемой 7 включения, т. е. если в течение заданного времени отсутствуют сигналы ошибок (Hia выходе сумматора 6), то срабатывает схема 7 включения и открывает схему 5 «И по входу 8. Этот момент считается оконча«ием начального фазирования и началом работы схемы коррекции ошибок. К этому моменту в регистре имеется память правильной информации, и любой сигнал «ошибка на выходе сумматора 6 будет через схему «И поступать на сумматор 4. При поступлении сигнала «ошибка на сумматор 4 в последнем осуществляется исправление ошибки. Так, например, .пусть вместо сигнала «1 на вход поступил ошибочный символ «О. Сигнал «ошибка (сигнал в виде «1), складываясь с ошибочным символом «О, дает 0@1 1, и на вход регистра поступает исправленный символ «1. Если вместо сигнала «О поступает ошибочный символ «1, то сигнал «ошибка (сигнал «1), складываясь с ошибочным символом «1, дает 10 , и на вход регистра поступает исправлен-ный символ «О.

Так как каждый символ принимаемой информации :При наличии ошибки корректируется независимо от других символов, в регистре сохраняется правильная фаза информации даже при наличии ошибок любой кратности и перерывах связи. Осуш,ествление коррекции ошибок на входе регистров обусловливает отсутствие размножения ошибок на выходе сумматоров 2 и 5. Это позволяет сохранять правильную фазу информации при ошибках любой кратности, ибо коррекция ошибок осуществляется без последствия (в регистре сохранена правильная информация, и любая поступившая ошибка исправляется).

Обработка информации в сумматорах 4 ц 6 осуществляется без потери такта.

Предмет изобретения

Устройство фазирования псевдослучайных последовательностей, образованных путем сложения по модулю два ряда рекуррентных последовательностей, сформированных в п регистрах с логическими обратными связями,

содержащее п регистров с логическими обратными связями, выходы каждого из которых подсоединены к первому входу соответствующего из п сумматоров по модулю два, и схему коррекции ощибок, отличающееся тем, что,

с целью удерл ания правильной фазы при Hiaличии ощибок, упомянутая схема коррекции ощибок своими выходами, соответствующими каждому з Помянутому регистру с логическими обратными связями, включена между входом

устройства и выходом каждого из п упомяну тых регистров с логическими обратными связями, причем выход каждого из п упомянутых сумматоров по модзлю два подсоединен к соответствующему входу упомянутой схемы

коррекции ошибок, начиная со второго, а к первому входу упомянутой схемы коррекции ощибок подключен выход схемы включения, к входу которой подсоединен выход п-го сумматора по модулю два.

| название | год | авторы | номер документа |

|---|---|---|---|

| Р-У6.-К ИЗОБРЕТЕНИЯ | 1973 |

|

SU391749A1 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ ПО ЦИКЛАМ | 1970 |

|

SU275106A1 |

| УСТРОЙСТВО ДИВЕРГЕНТНОГО ДЕКОДИРОВАНИЯ СЕГМЕНТОВ ЛИНЕЙНОЙ РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2023 |

|

RU2820053C1 |

| Устройство для цикловой синхронизации | 1976 |

|

SU640439A1 |

| Устройство фазирования псевдослучайных последовательностей | 1974 |

|

SU657637A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ НА ОСНОВЕ МАТРИЧНОЙ ОБРАБОТКИ И ДЕЦИМАЦИИ РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2023 |

|

RU2820337C1 |

| Устройство для цикловой синхронизации с исправлением одиночных ошибок в рекуррентной последовательности | 1971 |

|

SU454705A1 |

| Устройство для контроля ошибок канала магнитной записи-воспроизведения | 1983 |

|

SU1101887A1 |

| Устройство для автоматического измерения характеристик дискретного канала связи | 1984 |

|

SU1197103A1 |

| Устройство для контроля ошибок воспроизведения информации с носителя магнитной записи | 1988 |

|

SU1527666A1 |

Авторы

Даты

1973-01-01—Публикация