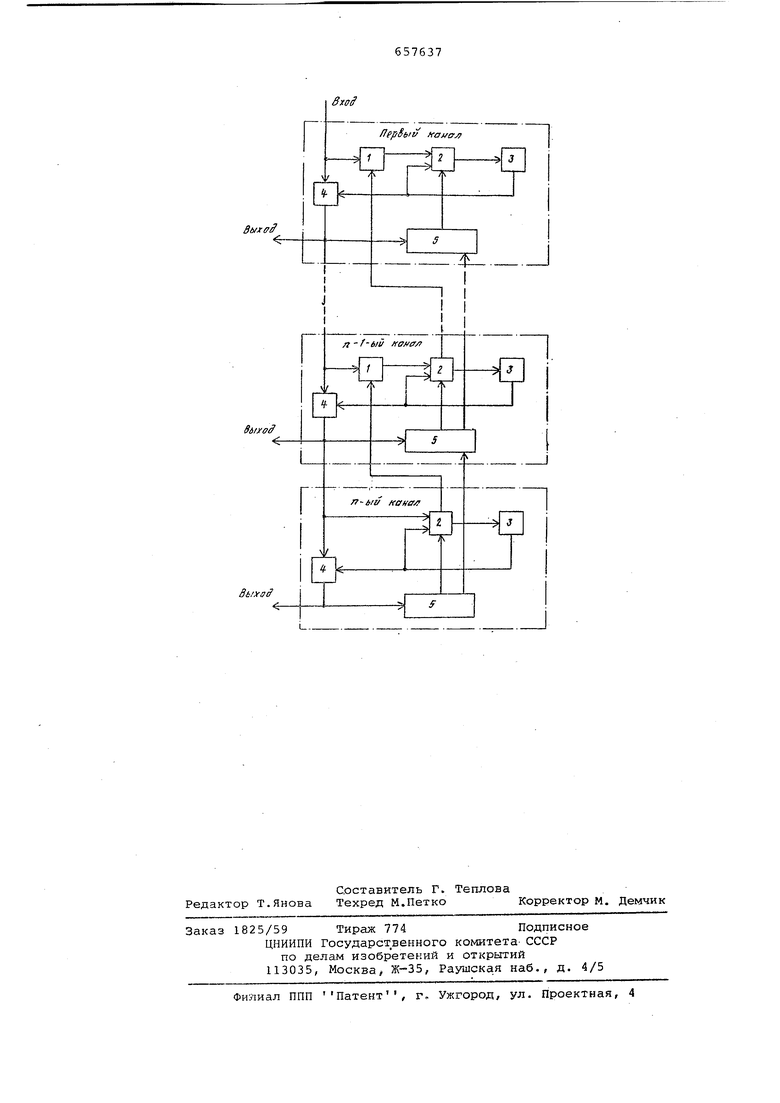

управляющим входам клгоча 2 подключены соответственно выход регистра сдвига 3 иепосредственно, а выход второго сумматора 4 через блок управления 5. Кроме того, другие выходыключа 2 и блока управления 5 каж,цого канала, кроме первого, подключены соответственно к вторым входам первого сумматора 1 и блока управления 5 предыдущего канала. Выход второго .сумматора 4 каждого канала (начиная с первого) соединен с вторым входом второго сум матора 4 последующего канала обработки ПСП. Устройство работает следующим образом. При включении устройства блоки управления 5 во всех П каналах уста навливаются в исходное состояние, при этом ПСП с входа устройства поступает через соответствующие сумматор 1 и ключ 2 в регистр сдвига 3. При поступлении на вход устройства последовательности, образованной сложением по модулю два П рекуррентных последовательностей с помощью сумматоров 4 и регистров сдвига 3 осуществляется проверка поступающей последовательности на соответствие закону формирования ее на передаче. В случае отсутствия ошибок на вы ходе п-го канала отсутствуют сигналы Ошибки, при этом блок управления 5 П ГО канала запрещает поступлени последовательности из сумматора 4 П-1-ГО канала на вход регистра сдвиг 3 Н-го канала, разрешает прохождение последовательности с выхода регистра сдвига 3 П-го канала на его вход чер сумматор 1 канала и подготавливает блок управления 5 П-1-го канала. В сумматоре 1 П-1-го канала осуще ствляется вычитание по модулю два из входной последовательности, поступаю щей с выхода сумматора 4 канала рекуррентного кода, сформирован ного в регистре сдвига 3 п -го канал В случае отсутствия ошибок на вы ходе су1 лматора 4 п-го канала блок управления 5 того же канала выдает сигнал, включающий блок управления 5 И 1-го канала, который запрещает поступление последовательности из сумматора 4 П 2-го канала на вход ре гистра сдвига 3 ti-1-го канала, разрешает прохождение последовательности с выхода регистра сдвига 3 и-1-го канала на его вход через сумматор 1 канала и подготавливает блок управления 5 п -2-го канала. Аналогично фазируются остальные регистры сдвига 3. Б случае поступления на вход устройства последовательности, образованной сложением по модулю два т рекуррентных кодов, где hi п , устройство начинает фазироваться с регистра сдвига 3 Tl-ro канала. Формула изобретения Устройство фазирования псевдослучайных последовательностей, содержащее в каждом из п-1 каналов обработки псевдослучайных последовательностей последовательно соединенные первый сумматор по модулю два, регистр сдвига с логической об|затной связью и второй сумматор по модулю, два, дру.гой вход которого соединен с соответствующим входом первого сумматора по модулю два, а в п канале - регистр сдвига с логической обратной связью и второй сумматор по модулю два, .а также блок управления, отличающееся тем, что, с целью удержания правильной фазы при наличии ошибок за счет обработки различного числа псевдослучайных последовательностей, в каждом из И-1 каналов между выходом первого сумматора по модулю два и входом регистра сдвига с логической обратной связью, а в П канале на входе регистра сдвига с логической обратной связью включен ключ, к управляющим входам которого подключены соответственно выход регистра сдвига с логической обратной связью непосредственно, а выход второго сумматора по модулю два - через блок управления, причем выходы ключа и блока управления каждого канала обработки псевдослучайных последовательностей подключены соответственно к вторым входам первого сумматора по модулю два и блока управления предыдущего канала обработки псевдослучайных последовательностей.

(JepSbv

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство фазирования псевдослучайных последовательностей | 1986 |

|

SU1381726A1 |

| Способ цикловой синхронизации с динамической адресацией получателя | 2016 |

|

RU2621181C1 |

| Устройство для контроля дуплексного канала связи | 1982 |

|

SU1061280A1 |

| Устройство для контроля дуплексного канала связи | 1983 |

|

SU1231621A2 |

| Устройство ввода-вывода синхронной двоичной информации в цифровые тракты | 1984 |

|

SU1374438A1 |

| Система для передачи и приема дискретной информации | 1980 |

|

SU886296A1 |

| Автокорреляционный измеритель параметров псевдослучайного фазоманипулированного сигнала | 1987 |

|

SU1518894A2 |

| Устройство для контроля дискретного канала | 1984 |

|

SU1298930A1 |

| Автокорреляционный измеритель параметров псевдослучайного фазоманипулированного сигнала | 1984 |

|

SU1197102A2 |

| Система телемеханики | 1986 |

|

SU1363282A1 |

Вь/кр

ffovcr/r

IPi

8&tyoff

ufl/ KOHffJ

Авторы

Даты

1979-04-15—Публикация

1974-10-29—Подача