Изобретение относится к вычислительной технике. Устройство может быть использовано для определения основных характеристик случайных процессов и в качестве решающего звена в системах автоматического регулирования технологических процессов. Известны комплексные экспресс-анал;изаторы случайных процессов, содержащие блок динамической памяти, два цифровых блока сравнения, схему «И, блок переписи, блок местного управления, датчик равномерно распределеииых случайных чисел, переключатели, блок схем «И и блок суммируюн их счетв этих устройствах аналоговые анализаторы дают высокую .методическую погрешность и не позволяют обрабатывать первичную информацию в реальном масштабе времени; цифровые анализаторы содержат громоздкие множительные устройства, сумматоры, уст ройства задержки и ЗУ большой емкости; для вычисления различных оценок вероятностных характеристик требуется отдельная аппаратура, что снижает надежность анализаторов, увеличивает их аппаратурный объем. Цель изобретения - упрощение схемы устройства. Предлагаемый экспресс-анализатор отличается тем, что выход блока динамической памяти через блок переписи и переключатель подсоединен либо ко входу первой цифровой схемы (блока) сравнения, либо ко входу схемы «И, второй вход которой, объединенный с управляющим входом датчика равномерно распределенных случайных чисел и через переключатель - со вторым входом первой цифровой схемы (блока) сравнения, соединен со вторым выходом блока местного управления, первый выход которого нагружен на управляющие входы блока переписи и блока динамической памяти, а третий соединен с управляющим входом блока схем второй выход блока динамической памяти через переключатель объединен с первым входом второй цифровой схемы (блока) сравнения, второй вход которой подключен к первому выходу датчика равномерно распределенных случайных чисел, второй выход которого через переключатель объединен со вторым входом первой цифровой схемы сравнения; выход второй Цифровой схемы сравнения нагружен на первый вход блока суммирующих счетчиков, объединенный с первым входом схемы «И, второй вход которой, связанный со вторым входом блока суммирующих счетчиков, соединен с выходом первой цифровой схемы сравнения и через переключатель - с сигнальиым входом блока схем «И, который через тот же переключатель связан либо с выходом первой схемы «И либо с выходом

второй схемы выход блока схем «И соединен с третьим входом блока суммир-ующих счетчиков, выход которого является выходом всей схемы.

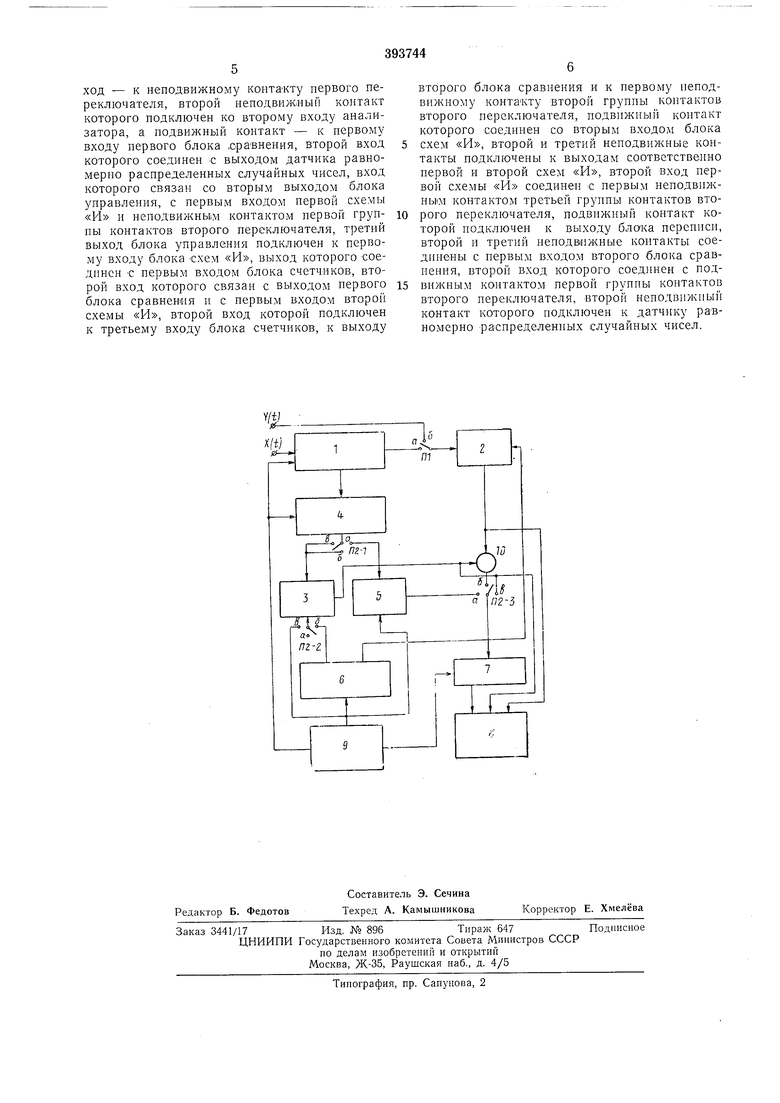

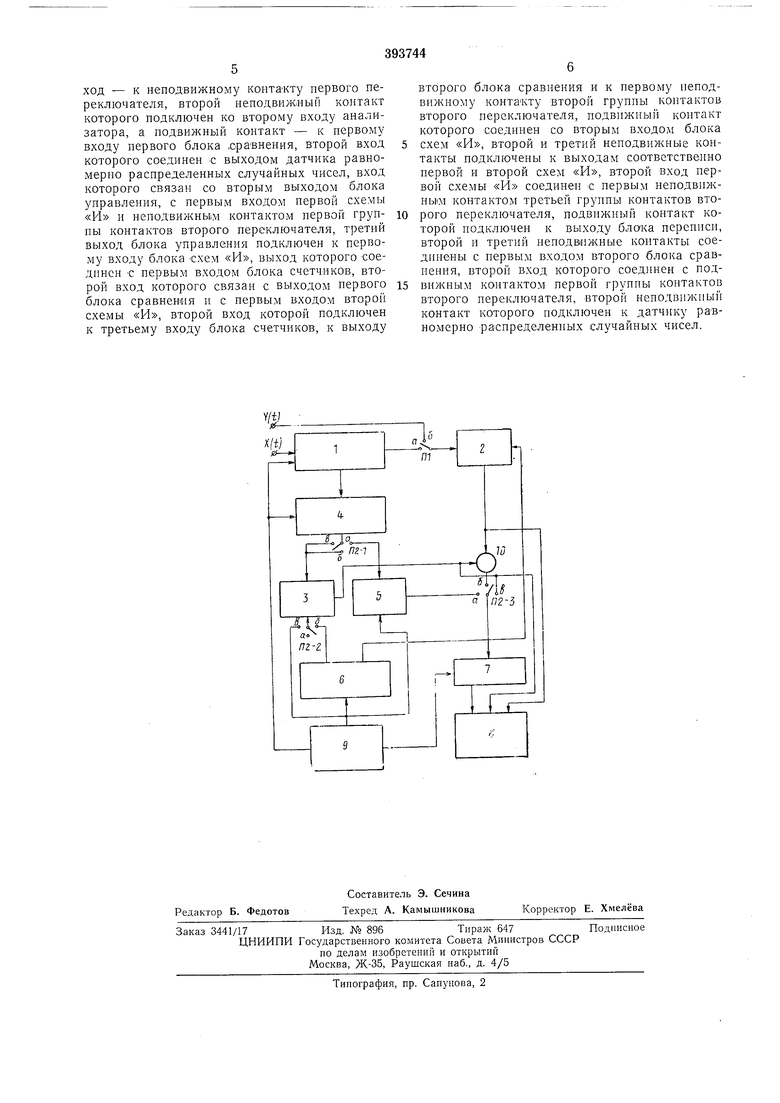

Блок-схема устройства показана на чертеже.

Комплексный экспресс-анализатор coдepJ жит блок динамической памяти /, состоящий из L регистров .сдвига, каждый на п разрядов (предназначен для получения переменной задержки ирц вычисление корреляционных функций);

- цифровые блоки сравнения 2, 3, алгоритм работы которых -

1 при Xi Zi

У1

О при л:; 2г,

где Xj - значение ординаты исследуемой

функции;

Z,- - значение ординаты вспомогательного сигнала;

-блок переписи 4, поочередно переписывающий значения исследуемой функции в блоки 3 и 5;

-схему «И 5, алгоритм работы которой-

I 1 при л:; г; 1 О при ,

-датчик равномерно распределенных случайных чисел 6 (ДРРСЧ), формирующий взаимно независимые числа, равномерно распределенные в ннтервале изменения исследуемой функции;

-блок схем «И 7, записывающий вычислеияые частные значения статистических характеристик в нужные адреса блока 8;

-блок суммирующих счетчиков 5, выполняющий функцию л-канального цифрового интегратора;

-схему «И 10.

При вычислеиин моментов и момсптных функций случайных процессов (математического ожидания, дисперсии, корреляционных функций) переключатель П2 иаходится в положении б. Положение о переключателя П1 соответствует режиму вычисления автокорреляционной функции, положсиие б - взаимокорреляционной.

Значение ординат исследуемой случайной функции X(i), занисаииые в блоке динамической памяти в виде L-разрядных двоичных чисел, поочередио переписываются блоком переписи, управляюнщми сигналами для которого являются сигналы, сформироваиные блоком местного управления, па первые входы .цифрового блока сравнения 3. На вторые входы этого блока подаются .-разрядные двоичные числа с выхода ДРРСЧ. Выходной числовой иоток блока 3 является статист гчески;М отображением функиИИ (t).

Цифровой блок сравнения 2 работает аналогичио. При вычислении первый начальных

моментов ( и ) переключатель П1 ставится в положение б. При этом значения функций X(t) и y(t) статистически кодируются в блоках 2 и 3 и интегрируются в счетчнках гпх и tn,j блока 9.

При вычислении моментов второго порядка числовые последовательности с выходом блоков 2 и 3 перемножаются на схеме «И 10 и через блок схем «И записываются в соответствующие счетчнк блока 8, причем прн вычислеиии автокорреляционной функции случайного процесса X{t) каждое чнсло л ,;, где , 2, ... .V Л - число членов ряда фуикцни X(t), поочередно умножается на

числа Xi+i; Xi.z; .... лг-ь„. Число Xi задерживается в блоке динамической памяти.

Для вычисления взаимокорреляционной функ-ции процессов X(t) и У(t) каждое У; число умножается иа числа ряда A,-+i; Xi..2, ,

Х:+пПри вычислении интегрального закона распределения F(x) случайного процесса X(t) из блока 9 на вторые входы блока 3 через переключатель П2 подаются числа, линейно

изменяющиеся в интервале изменення исследуемой функции, причем период повторения этой линейной последовательности равен периоду подачи на первые входы блока 3 значений исследуемой функции y(t).

Синхронно с выдачей каждого чнсла из лннейной последовательности блок 9 выра.батывает разрешающий сигнал, который подается па один из раздельных входов блока схем «И 7. Каждая схема блока 7 иагружена на

вход «своего счетчика из блока 8. Таким образом, при фор.мнровании первого числа из линейной последовательности открыта первая схема блока 7 и, следовательно, результат сравнения этого чнсла со значением иеследуемой функции заннсывается в иервый счетчик блока 8 и т. д.

При вычислении плотности вероятности f(X) случайного нроцесса X(t) (нереключатель |П2 в положеЕ1ии а) числа линейной последовательности с выхода блока 9 поступает на схему «И 5, которая формнрует сигнал «1 только при одинаковых значениях исследуемо случайиой функции и одного из чисел линейпой последовательности. В остальном работа схемы аналогична описанной г.ыще.

Предмет изобретен и я

Комплексный экспресс-анализатор случайных процессов, содержаи ий блоК памяти, блокн сравнения, схемы «П, блок нерепнси, блок управления, блок схем «П, датчик равномерно распределеиных случайных чисел, блок счетчиков н переключателя, отличающийся тем, что, с целью упрощения схемы, первый выход блока управления подключен к первым входам блока переписи и блока памяти, второй вход которого подключеи к первому входу анализатора, иервый выход - ко второму входу блока иереписи, второй выход - к неподвижному контзкту первого переключателя, второй неподвижныГ) контакт которого подключен ко второму входу анализатора, а подвил ный контакт - к первому входу первого блока сравнения, второй вход которого соединен с выходом датчика равномерно распределенных случайных чисел, вход которого связан со вторым выходом блока управления, с первым входом первой схемы «И и неподвижны1м контактом первой группы контактов второго переключателя, третий выход блока управления подключен к первому входу блока схем «И, выход которого соединен € первым входом блока счетчиков, второй вход которого связан с выходом первого блока сравнения и с первым входом второй схемы «И, второй вход которой подключен к третьему входу блока счетчиков, к выходу

второго блока сравнения н к первому неподвижному контакту второй группы контактов второго переключателя, подвижный контакт которого соединен со вторым входом блока схем «И, второй и третий неподвижные контакты подключены к выходам соответственно нервой и второй схем «И, второй вход первой схемы «И соединен с первым пеподвижНЫ1М контактом третьей группы контактов второго переключателя, подвижный контакт которой подключен к выходу блока переписи, второй и третий иеподвижные коптакты соединены с первым входом второго блока сравнения, второй вход которого соединен с подвижным контактом первой группы коитактов второго переключателя, второй неподвижный контакт которого подключен к датчику равномерно распределенных случайных чисел.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Многоканальный статистический анализатор | 1977 |

|

SU732890A1 |

| Генератор пуассоновского потока импульсов | 1991 |

|

SU1786648A1 |

| Статистический анализатор | 1977 |

|

SU693398A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Цифровой анализатор спектра | 1979 |

|

SU798615A1 |

| Универсальный статистический экспрессанализатор | 1972 |

|

SU452000A1 |

| Анализатор спектра сигналов | 1986 |

|

SU1399765A1 |

| Цифровой вероятностный фильтр | 1972 |

|

SU479117A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

Авторы

Даты

1973-01-01—Публикация