1

Предложенное устройство относится к области дискретной автоматики и вычнслительной техники и может .быть использовано при реализации технических средств вычислительной техники и систем автоматического управления и контроля.

Известны устройства для сравнения десятичных чисел, содержащие два регистра, связанные входами с выходом схемы «И, а выходами- со входами соответствующих элементов памяти, одни выходы которых подключены ко входам схемы формирования результата сравнения, связанной выходами со входал н схемы индикации.

Однако известные устройства имеют низкое быстродействие.

Предложенное устройство отличается тем, что в него введены схема управления опросом, входы которой связаны с другими выходами соответствующих элементов памяти, а выхолЧы - со входами опроса элементов памяти, и узел контроля, вход которого связан с выходом схемы «И, а выход - с другим входом схемы управления опросом и со входом схемы «И.

Это позволяет увеличить быстродействие устройства.

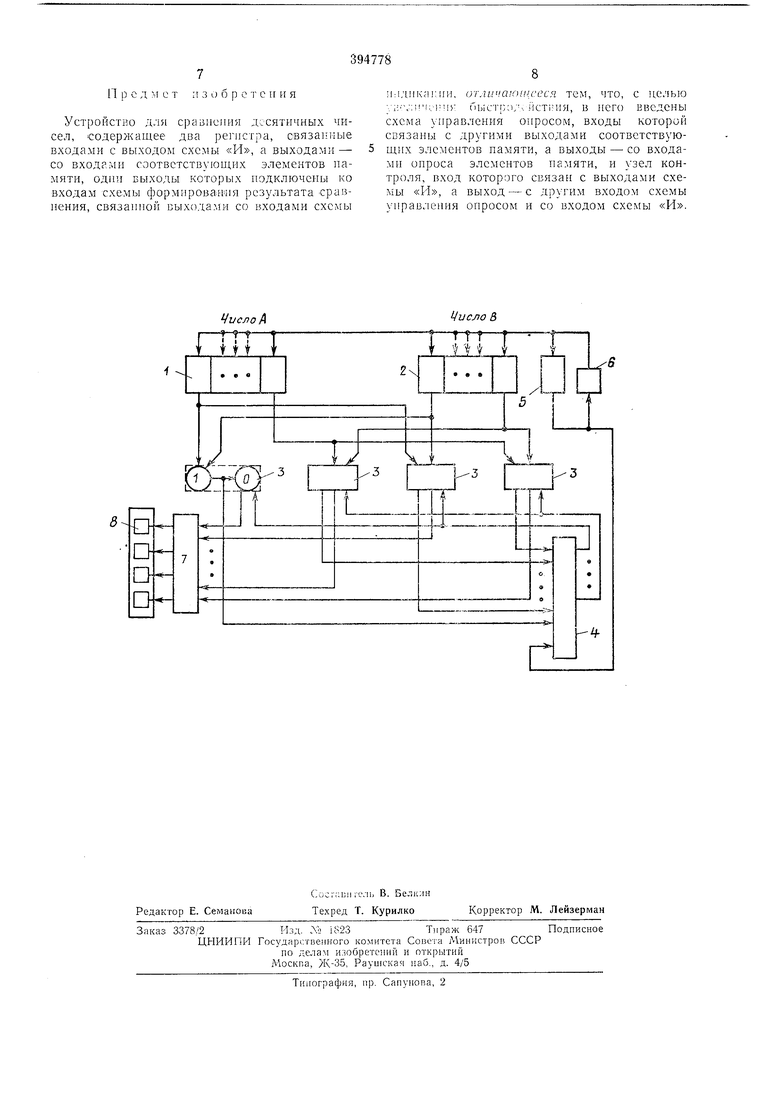

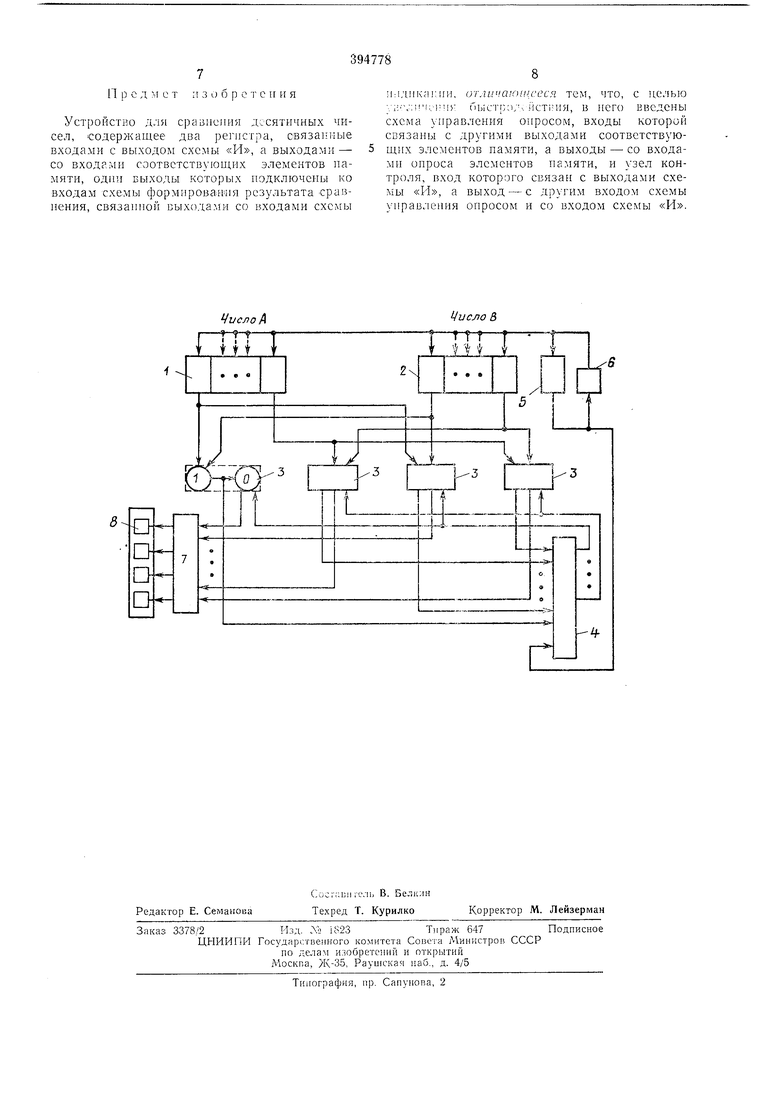

Блок-схема устройства приведена на чертеже.

Устройство содержит регистр / числа Л и

регистр 2 числа В, выходы которых связаны со входами соответствующих элементов памяти 3. Выходы элементоБ памяти подключены ко входам сх:мы управления опросом 4.

другой вход которой связан с выходом узла контроля 5, подкл;оче;п1ого ко входу схемы «И 6, соединенной выходом с информационными входами регистров / и 2.

Выходы элементов памяти 3 связаны со

входами схемы формирования результата сравнения 7, выходы которой подключены ко входам схемы индикации 8. Регистры 1 и 2 содержат двоично-десятичные декады на каждый десятичный разряд сравниваемых щкал,

служащие для записи и параллельного сравнения десятичных разрядов чисел.

Элементы пг,:.:яти 3 слу-сат для приема и хранения информации, полученной в результате параллельного сравнения в двоично-десятичных декадах регистров 1 и 2 десятичных разрядов одпнаки.вого порядка сравниваемых чисел. Каждый элемент памяти может быть выполнен, например, на двух ферритовых сердечниках, связанных между собой так, что

в исходном положении первый ферритовый сердечник находится в состоянии «1, а второй - в ссстояпнн «О.

Схема управления онросом 4 по мере переполнения двоично-десятичных декад регистров / и 2 анализирует информацию, поступающую с них в элементы памяти 3, и на основе HHavii-iaa этой информации выбирает для опроса те элементы памяти, в которых записанный результат сравнения десятичных разрядов одинакового порядка позволяет судить о результате сравнения чисел. Узел контроля 5 определяет максимальное время заполнения двоично-десятичных декад регистров 1 и 2 заполняющими импульсами и при переполнении ее через схему управления опросам 4 опрашивает элементы памяти 3 и отключает схему «И 6. Схема «И 6 пропускает или занреи ает постуилеиие заполняюш,их импульсов на входы регистров / и 2 и узел контроля 5. Предложенное устройство сравнения десятичных чисел работает следуюгцнм (образом. Пусть необходимо сравнить между собой число А и число В для выявления их равепства или неравенства между собой, где: /1 - заданная величина, В - фактически измеренная величина. В исходном состоянии эти числа поступают либо последовательно, либо параллельио в регистры 1 и 2. При этом в декаде узла контроля записано число «О, каждый элемепт памяти находится в состоянии «1-О. При сравнении через схе.му «П б па вход регистров 1 и 2 каждого десятичного разряда сравниваемых чисел и иа вход декады узла контроля 5 одновременно подается последовательность заполняюш,их и.мпульсов. Каждая двоично-десятичная декада регистров / и 2 и декада узла контроля 5 заполняется до переполнения, при этом двоичнодесятичная декада с любы.м большим но абсолютной величине десятичным разрядом одного числа переполнится раньше двоично-десятичной декады того же порядка, но с меньшим по абсолютной величине десятичным разрядом другого числн. Папример, если в одной двоично-десятичной декаде записан разряд а/, числа Л, а в другой разряд Ьл числа В, где а и Ь), - любые десятичные разряды одинакового порядка чисел А и В, то в случае, если 1аА| -|6;;|, раньше переполнится двоично-десятичная декада с занисаниым в нее разрядом ал, так как для ее иереполнения на ее вход необходимо иодать меньшее количество заполняюндих импульсов, чем для нереполиения двоично-десятичной декады с разрядо.м 6;,. В случае, если |ал ; Ьл|, то раньпю переиолнится двоично-десятичная декада с разрядом Ь/,. Следовательно, импульс переполнения на выходе двоично-десятичной декады с любым большим по абсолютной величине десятичным разрядом одного из сравниваемых чисел появится раньше, чем импульс переполнения на выходе двоично-десятичной декады того же порядка, но с меньшим по абсолютной величине разрядом другого из сравниваемых чисел. Импульс переполнения с двоичио-десятичnoil декады с любым больши.м по абсолютной величине десятичным разрядом одного числа ПОСТУПИТ па вход перезаписи «1 из первого кольиа во второе в своем элемепте намятп 3 и на вход списывания «1 в первом кольце в соотвстствуюпдем элементе памяти сравниваемого с ним разряда другого числа. Таким образом, во вто)ых кольцах элементов па.мятп двух десятнчпых разрядов одннакового порядка срав1 нваемых чисел в виде «1 переполнения п «О будет записана ииформация о том, какой из сравниваемых между собой разрядов больше. Пмпульс перенолпепия с двоичпо-десятичiu) декады с меплпим по абсолютной величине разрядом, гюявлякпцийся позже импульса Г1ерег1ол 1еп я с двопчпо-десятичпой декады е больп1им по абсолютпой величине разрядом, поетупает па вход пе к записи «1 с первого кольца во второе в своем элементе памяти и на вход списывания «1 в первом ко.чьце в соответствующем элементе намяти сравниваемого с пп.м разряда другого числа. По так как па эти входы уже поступал пмпульс перенолпепня с диоично-десятпчной декады переполнивпшйся раньше, то пмпульс, поступ1П5шнй позже, пе изменит состояние первых Ko.ieH элемептов памяти даппых раз;)ядов. В случае равенства срав 1иваемых десятичных разрядов обе двоично-десятичные декады ретстроБ 1 и 2 даппых разрядов нерепол 1ятся од 1овреме11по, п пмнульсы неренолпеппя перезапип ут «1 згз первых колец своих ЭП 2 во вторые. Таким образом, в обоих вторых кольцах ЭП 2 будут заннсапы «1. Исходя из вьинеприведенных расеуждепий, в случае сравнения чисел А и В при нараллельном заполпснип двоично-десятичных декад регистров / п 2 одновременно поразрядно сравниваются .между собой Ь|-старшие десятичные разряды ера1зппваемых чисел; Ьп - младшие десятичные разряды еравннваемых чисел. При с)апнспп а/; и ,. между собой возможны следуюпще варианты результата сравнения ноеле записп его во вторые кольца э.чементов памяти 3: ) |а;,, ЭП (bk) - «О. то1да Э11 ( - «1, 2) |ал| bi,, ЭП (bk) -«1. тогда ЭП (flft) - «О огда ЭП (Oh) -«1, ЭП (Ьл) -«1, где П (fl/i), ЭП (feft) - элементы памяти с заретом соответствуюпхпх десятичных разряов сравниваемых чисел: ah, b/,-любые есятичные разряды сравниваемых чисел. Пмнульсы перезаписи «1 из первого кольа ЭП 3 во второе одиовременно поступают а адаптивную схему управления опросо.м 4.

Адаптивная схема управления опросом 4 анализирует информациЕО, поступающую во вторые кольца ЭП 3 при сравнении десятичных разрядов одинакового порядка, и па основании этого анализа работает следующим образом.

Если сравниБлемые десятичные разряды равны между с )бой, то импульсы перезаписи «1 на соответствующих входах адаптивной схемы управления опросом 4 ноявляется одновременно, и схема запретит опрос ЭП 3 данных разрядов.

В случае равслства младщпх десятичных разрядов сравниваемых чисел, запрет на опрос ЭП 3 млялших разрядов не выдается, так как в случае равенства всех предыдущих разрядов опрос их ЭП 3 запрещен и если запретить опрос ЭП 3 младших разрядов, то невозможно будет определить результат сравнения.

Если сравниваемые десятичные разрялты одинакового порядка не равны между собой, то при поступлении с ЭП 3 информации об их неравенстве, адаптивная схема управления опросом 4 разрешит опрос ЭП 3 данных разрядов и разрядов, старше данных, и запретит опрос ЭП 3 всех последующих разрядов после сравниваемых, так как по неравенству данных десятичных разрядов, в случае равенства предыдущих, уже можно определить результат сравнения, не обращаясь к последующим десятичным разрядам.

Таким образом, по окончании записи в ЭП 3 результата параллельного сравнения десятичных разрядов одинакового порядка, адаптивная схема управления опросо.м 4 оставит для опроса ЭП 3 только того одного десятичного одинакового порядка, по которому можно определить результат сравнения.

Так как в декаде узла контроля 5 в нсходном состоянии записано число «О, то она определяет максимальное время заполнения двоично-десятичных декад регистров / и 2 до переполнения. Поэтому, если на выходе узла контроля 5 появляется импульс переполнения, идущий на оирос ЭП 3 и на вход схемы «И 6, это значит, что все двоично-десятичные декады регистров 1 и 2 заполнились до переполнения.

Импульс переполнения с узла контроля 5 запрещает прохождение через схему «И 6 заполняющих импульсов и опращивает вторые кольца ЭП 3.

Информация с ЭП 3 поступает на схему формирования результата сравнения 7.

Схема формирования результата сравнения в зависимости от информации, заиисанной с ЭП 3 опрашиваемых разрядов, формирует и выдает на один из трех индикаторов одну из команд «РАВПО, «БОЛЬШЕ, «МЕПЬШЕ и команду «КОНЕЦ СРАВНЕНИЯ на схему индикации 8.

Время сравнения tc в сравнивающем устройстве Складывается из времени /д заполнения двоично-десятичных декад регистров 1

и /, определяемого максимальным временем заполнения деклды узла контроля 5 до переполнения, времени оироса ЭП 3 /о и времени формирования команды в схеме формпрования результата сравнения 7 /к4 Д + 0 + 4,

Время заиолнония декады узла контроля 5 до переполнения не зависит от разрядности сравниваемых чисел и определяется только частотой поступления заполняющих импульсов. При частоте импульсов заполнения, равной - F

/ - 0

д - ;:

Время запроса ЭП 3 to не зависит от разрядности сравниваемых чисел, так как адаптивная схема правления опросом выбирает для опроса ЭП 2 только того одного десятичного разряда одинакового порядка, по которому можно определить результат сравнения чисел, и .мало по сравнению с /д.

Время формирования команды результата сравнения /к в схеме формирования результата сравнения 7 не зависит от разрядности сравниваемых чисел, определяется впутрепней структурой логической схемы и мало по сравнению с . Таким образом.

10

fc-.1,

F

Следовательно, время еравнення г определяется частотой поступлення заполняющих импульсов и не зависит от разрядности сравниваемых чисел.

В предлагаемом устройстве для сравиения десятичных чнсел уменьшение времени сравнения достигается благодаря иараллельному сравнению между собой десятичных разрядов

одинакового порядка сравниваемых чисел при одновременном заиолнении всех двоичнодесятичных декад регистров / и 2 и благодаря введению адаптивной схемы управления опросом 4, которая разрешает опрос только

тех ЭП 3, в которых записаи результат сравиения десятичных разрядов одинакового порядка, позволяющий судить о результате сравнения чисел. Таким образом, адаптивная схема уиравлення опросом 4 обеспечивает независимость времени опроса ЭП 3, а следовательно, и времени сравнения /с от разрядности еравнивасмых чисел.

Кроме того, необходимо учитывать, что

так как время сравнения /с не зависит от разрядности сравниваемых чисел, а определяется частотой поступления заполияющих и.мпульсов , то, изменяя частоту заполняющих импульсов, время сравнения чисел

можно регулировать.

11 р с д м с т п 3 о б р с т с п и я

Устройство для сразиеиия десятичных чисел, содержащее два регистра, связанные входами с выходом схемы «И, а выходами - со входами Схтответствуюии-ьх элементов иамяти, одни выходы которых подключены ко входам схемы формирова:ния результата сравнения, связанной выходами со входами схемы

, огличсиспассся тем, что, с целью y;; ; i;ii)- быстр; ;--. iCTi4«i, в него введены схема управления опросом, входы которой связаны с другими выходами соответствующих элементов памяти, а выходы - со входами онроса элементов памяти, и узел контроля, вход которого связан с выходами схемы «И, а выход - с другим входом схемы управления опросом и со входом схемы «И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения десятичных чисел | 1977 |

|

SU736093A1 |

| Система передачи информации с драг | 1972 |

|

SU481931A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU691843A1 |

| ЗСЕСОИЗЗНАЯ [ | 1973 |

|

SU375641A1 |

| Способ компенсации погрешностей акустических локационных уровнемеров и устройство для его осуществления | 1985 |

|

SU1529047A1 |

| АДАПТИВНЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1991 |

|

RU2043648C1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

| МНОГОКАНАЛЬНОЕ СЧЕТНО-ИНДИКАТОРНОЕ УСТРОЙСТВО | 1972 |

|

SU356638A1 |

| Тренажер оператора автоматизированной системы управления | 1981 |

|

SU983738A1 |

| Устройство для преобразования кодов | 1977 |

|

SU744544A1 |

Число А

оcfofDl vc o 3

1/3

Авторы

Даты

1973-01-01—Публикация