Изобретение относится к автоматике и вычислительной технике и может быть использовано при реализации технических средств вычислительной техники и систем автоматического управления и контроля.

Известно устройство для сравнения десятичных чисел, содержащее счетчики, элементы И, ИЛИ, НЕ и обеспечивающее последовательное поразрядное сравнение чисел между собой 1.

Недостаток этого устройства его малое быстродействие.

Наиболее близким техническим решением к предлагаемому является устройство для сравнения десятичных чисел, содержащее два регистра, входами связанные с выходом элемента И, а выходами - со входами элементов памяти соответствующего числа и Входами соответствующих элементов памяти сравниваемого с ним числа, блок управления -опросом, входами соединенный с выходами эле1 1ентов памяти, другие выходы которых через блок формирования результата сравнения связаны с блоком индикации, выходами со входами опроса элементов памяти, и узел контроля, вход которого подключен ко входу элемента И, выход К другому входу блока управления опросом и ко входу элемента И 2.

Недостатком этого устройства является его сложность.

Цель изобретения - упрощение устройства.

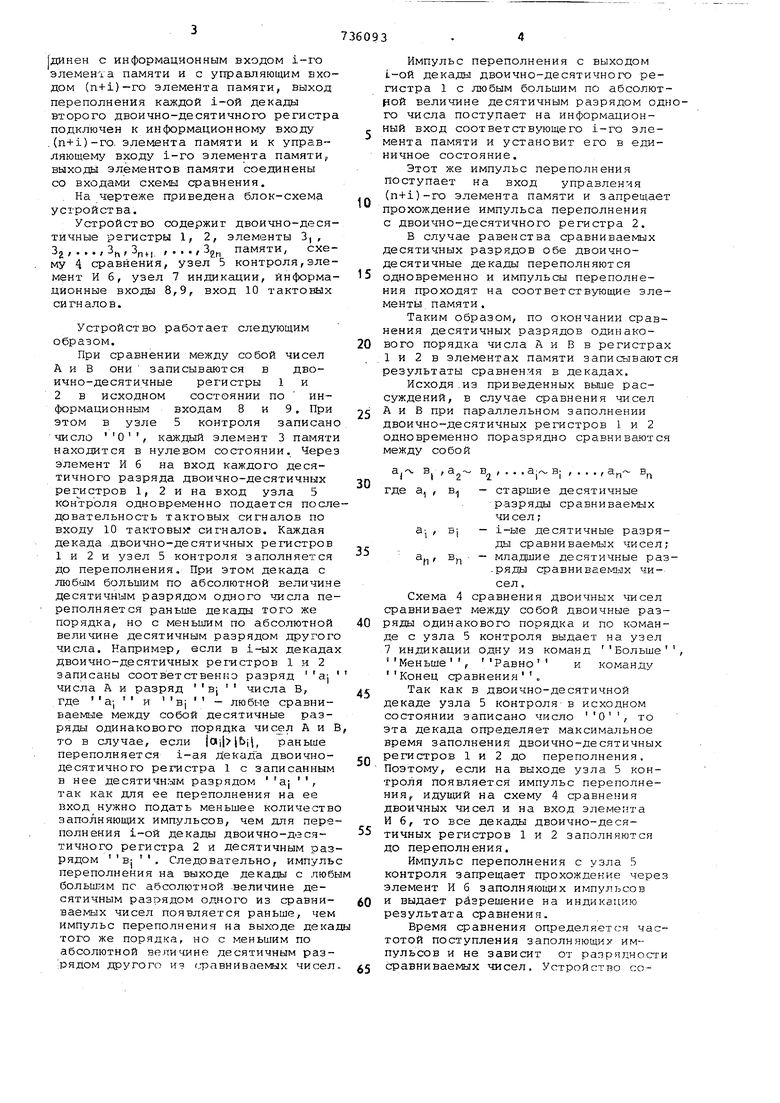

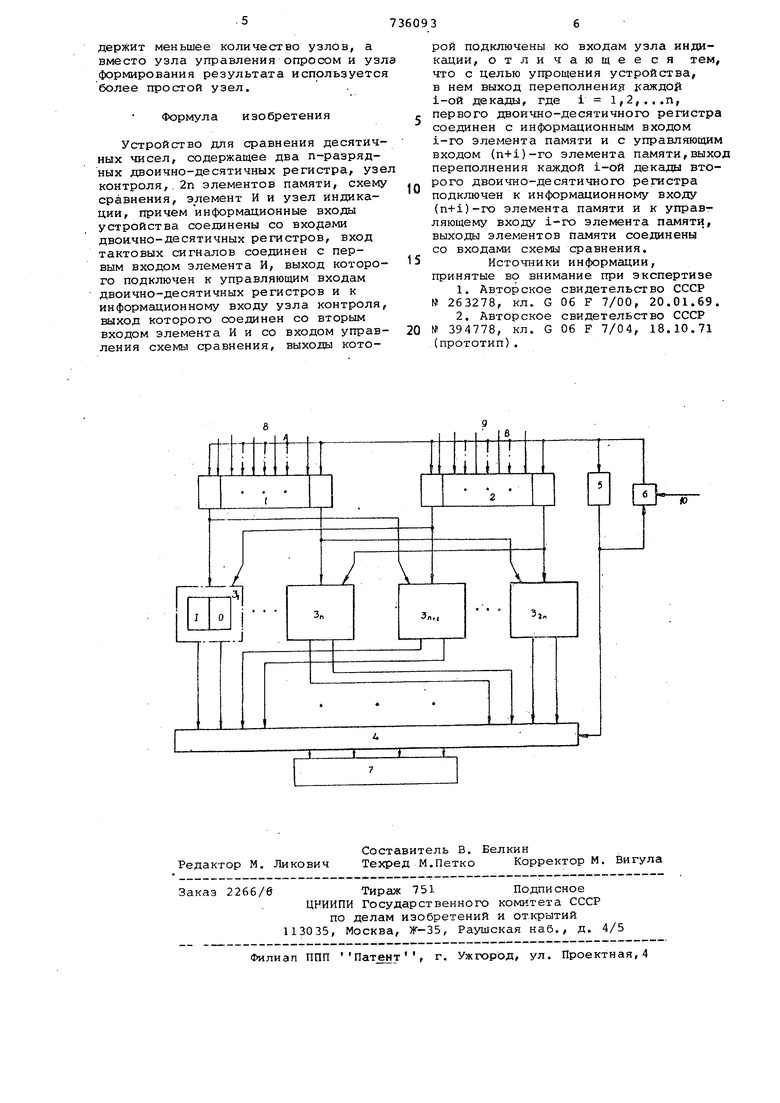

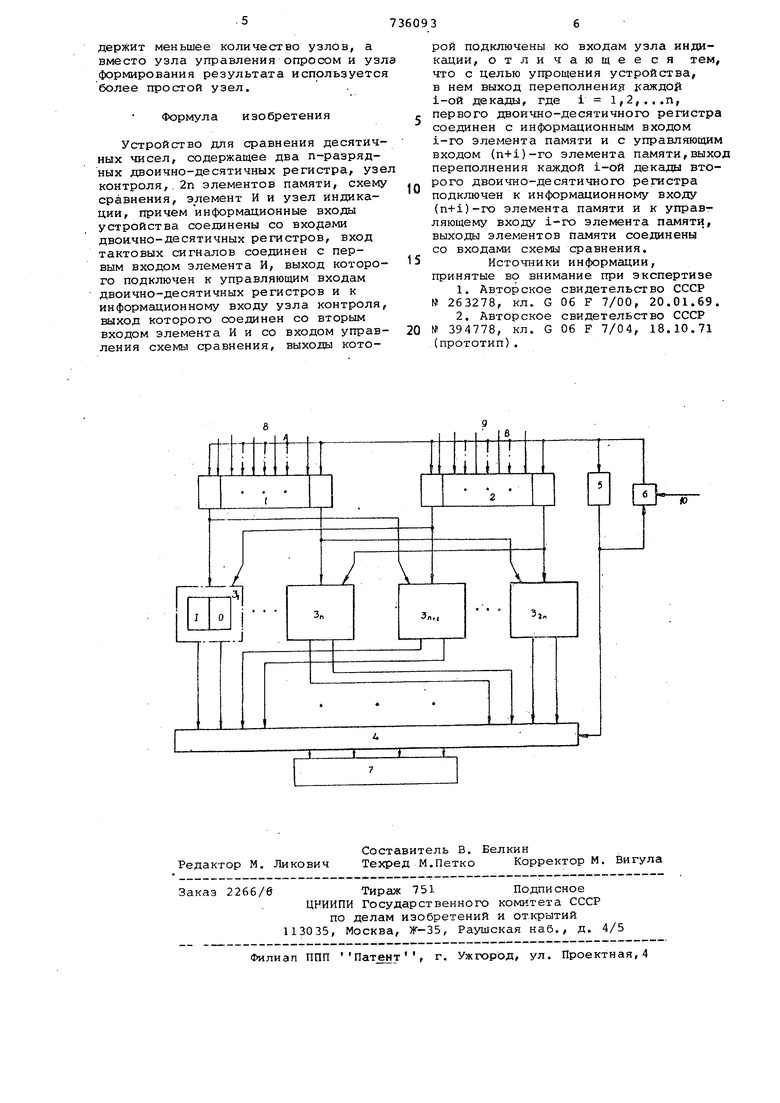

Поставленная це;1Ь достигается тем, что в устройстве Д1ля сравнения десятичных чисел, содержащем два п-разрядных двоично-десятичных регистра, узел контроля, 2п элементов памяти, схему сравнения, элемент И и узел индикации, причем информационные входы устройства соединены со входами двоично-десятичных регистров, вход тактовых сигналов соединен с перщ|з1м входом элемента И, выход которого подключен к управляющим входам двоично-десятичных регистров и к информационному входу узла контроля, выход которого соединен со вторым входом элемента И и со входом управления схемы сравнения, выходы которой подключены ко входам узла индикации,выход переполнения . каждой i-ой декады, где i ,...,п первого двоично-десятичного регистра соединен с информационным входом элемента памяти и с управляющим входом (n+i)ro элемента памяти, выход переполнения каждой i-ой декады второго двоично-десятичного регистра подключен к информационному входу .(n+i)-ro. элемента памяти и к управляющему входу 1-го элемента памяти, выходы элементов памяти соединены со входами схемы сравнения. На чертеже приведена блок-схема устройства. Устройство содержит двоично-десятичные регистры 1, 2, элементы 3,, За , . . ., 3 , 3„„. памяти, схему сравнения, узел 5 контроля,элемент И б, узел 7 индикации, йнфор1мадйонные входы 8,9, вход 10 тактовых си гн ало в. Устройство работает следующим образом. При сравнении между собой чисел А и В они записываются в двоично-десятичные регистры 1 и 2 в исходном состоянии по информационным входам 8 и 9. При этом в узле 5 контроля записан каждьой элемент 3 памяти находится в нулевом состоянии. Чере элемент И 6 на вход каждого десятичного разряда двоично-десятичных резгистров 1, 2 и на вход узла 5 контрЬля одновременно подается посл довательность тактовых сигналов по входу 10 тактовы г сигналов. Каждая декада .двоично-десятичных регистров 1 и 2 и узел 5 контроля заполняется до переполнения. При этом декада с любым большим по абсолютной величин десятичным разрядом одного числа пе реполняется раньше декады того же порядка, но с меньшим по абсолютной величине десятичным разрядом другог числа. Например, если в i-ых декада двоично-десятичных регистров 1 и 2 записаны соответственно разряд aj числа А и разряд в; числа В, где а-| и В| - любые сравниваемые между собой десятичные разряды одинакового порядка чисел А и то в случае, если раньше переполняется i-ая декад а двоичнодесятичного регистра 1 с записанным в нее десятичным разрядом aj , так как для ее переполнения на ее вход нужно подать меньшее количеств заполняющих импульсов, чем для пере полнения декады двоично-десятичного регистра 2 и десятичным раз рядом Bj . Следовательно, импуль переполнения на выходе декады с люб большим ПС абсолютной величине десятичным разрядом одного из сравниваемых чисел появляется раньше, чем импульс переполнения на выходе дека того же порядка, но с меньшим по абсолютной величине десятичным раз:РяДом другого из сравниваемых чисел Импульс переполнения с выходом 1-ой декады двоично-десятичного регистра 1 с любым большим по абсолютной величине десятичным разрядом одного числа поступает на информационный вход соответствующего i-ro элемента памяти и установит его в единичное состояние. Этот же импульс переполнения поступает на вход управлен--5я (n+i)-ro элемента памяти и запрещает прохождение импульса переполнения с двоично-десятичного регистра 2. В случае равенства сравниваемых десятичных разрядов обе двоичнодесятичные декады переполняются одновременно и импульсы переполнения проходят на соответствующие элементы памяти. Таким образом, по окончании сравнения десятичных разрядов одинакового порядка числа А и В в регистрах 1 и 2 в элементах памяти записываются результаты сравнения в декадах. Исходя.из приведенных выше рассуждений, в случае сравнения чисел А и В при параллельном заполнении двоично-десятичных регистров 1 и 2 одновременно поразрядно сравниваются между собой в, , . . . а,. где а, , в - старшие десятичные разряды сравниваемых чисел; i-ые десятичные разряды сравниваемых чисел; младшие десятичные раз.ряды сравниваемых чисел. Схема 4 сравнения двоичных чисел сравнивает между собой двоичные разряды одинакового порядка и по команде с узла 5 контроля выдает на узел 7 индикации одну из команд Больше, Меньше, Равно и команду Конец сравнения„ Так как в двоично-десятичной декаде узла 5 контроля в исходном состоянии записано число О , то эта декада определяет максимальное время заполнения двоично-десятичных регистров 1 и 2 до переполнения. Поэтому, если на выходе узла 5 контроля появляется импульс переполненияр идущий на схему 4 сравнения двоичных чисел и на вход элемента И 6, то все декады двоично-десятичных регистров 1 и 2 заполняются до переполнения. Импульс переполнения с узла 5 контроля запрещает прохождение через элемент И б заполняющих импульсов и выдает разрешение на индикацию результата сравнения. Время сравнения определяется частотой поступления заполняющих импульсов и не зависит от разрядности сравниваемых чисел. Устройство содержит меньшее количество узлов, а вместо узла управления опросом и узл формирования результата используется более простой узел.

Формула изобретения

Устройство для сравнения десятичных чисел, содержащее два п-разрядных двоично-десятичных регистра, узел контроля,. 2п элементов памяти, схему сравнения, элемент И и узел индикации, причем информационные входы устройства соединены со BxoftaMH двоично-десятичных регистров, вход тактовых сигналов соединен с первым входом элемента И, выход которого подключен к управляющим входам двоично-десятичных регистров и к информационному входу узла контроля, выход которого соединен со вторым входом элемента И и со входом управления схемы сравнения, выходы которой подключены ко входам узла индикации, отличающееся тем, что с целью упрощения устройства, в нем выход переполнения каждой 1-ой декады, где i l,2,...n, первого двоично-десятичного регистра соединен с информационным входом i-ro элемента памяти и с управляющим входом (п+1)-го элемента памяти,выход переполнения каждой ±-ой декады второго двоично-десятичного регистра

0 подключен к информационному входу (п+1)-го элемента памяти и к управляющему входу i-ro элемента памяти, выходы элементов памяти соединены со входами схемы сравнения.

5

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР

№ 263278, кл. G 06 F 7/00, 20.01.69.

2.Авторское свидетельство СССР

0 № 394778, кл. G 06 F 7/04, 18.10.71 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для СРАВНЕНИЯ ДЕСЯТИЧНЫХ ЧИСЕЛ | 1973 |

|

SU394778A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU993244A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

| Компаратор | 1981 |

|

SU1010614A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU691843A1 |

| Способ компенсации погрешностей акустических локационных уровнемеров и устройство для его осуществления | 1985 |

|

SU1529047A1 |

| Устройство для поиска чисел в заданном диапазоне | 1982 |

|

SU1116426A1 |

| Устройство для психологических исследований | 1989 |

|

SU1644908A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Тренажер оператора автоматизированной системы управления | 1981 |

|

SU983738A1 |

Авторы

Даты

1980-05-25—Публикация

1977-08-31—Подача