Изобретение относится к области автоматики и вычислительной техники и, в частности, может использоваться лри построении регистров Сдвига и устройств .памяти в многофазных системах на полевых МДП-структуpax.

Известны регистры сдвига на МДП-транзисторах, содержащие в .каждом разряде входной транзистор, инверторы «а переключательном и нагрузочном транзисторах, транзисторы обратной связи, овяза-нные с шина1ми им.пульсного питания.

Предлагаемый регистр сдвига отличается тем, что iB нем затвор транзистора обратной СВЯЗИ соединен с дополнительной ши«ой источника импульсного шитания, исток - со стоIKOM переключательного транзистора, а сток- с затвором переключательного транзистора.

Это .позволяет упростить устройство и уменьшить потребляемую .мощность.

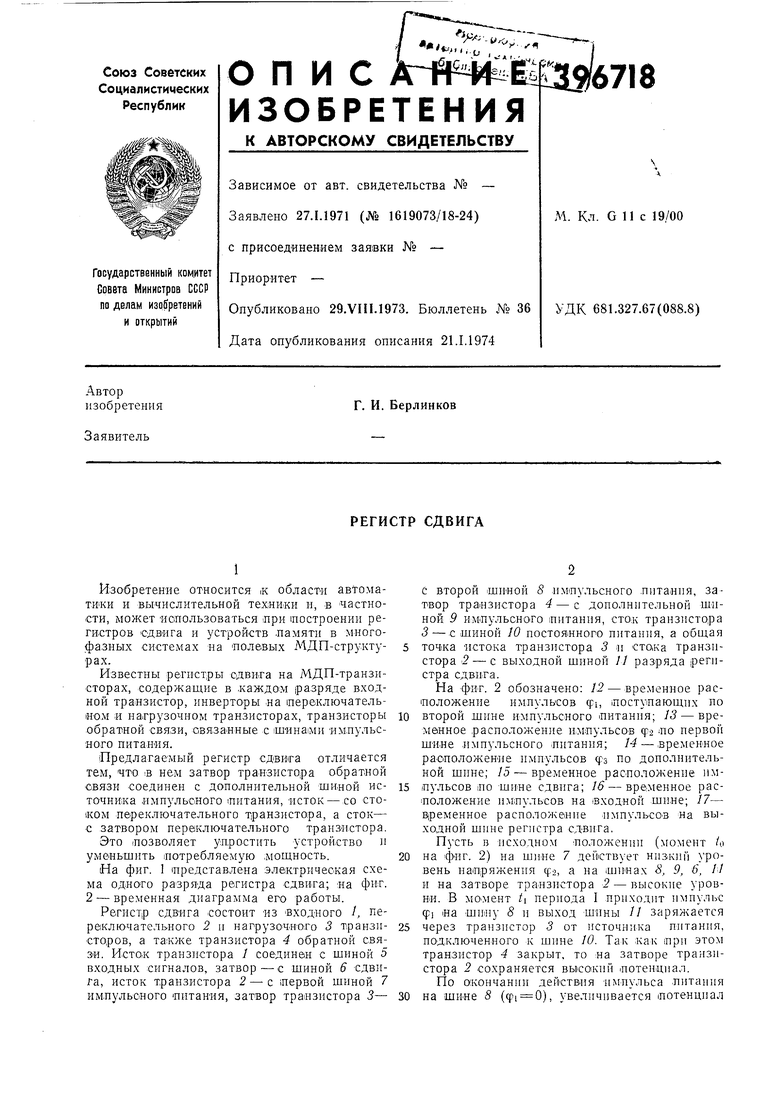

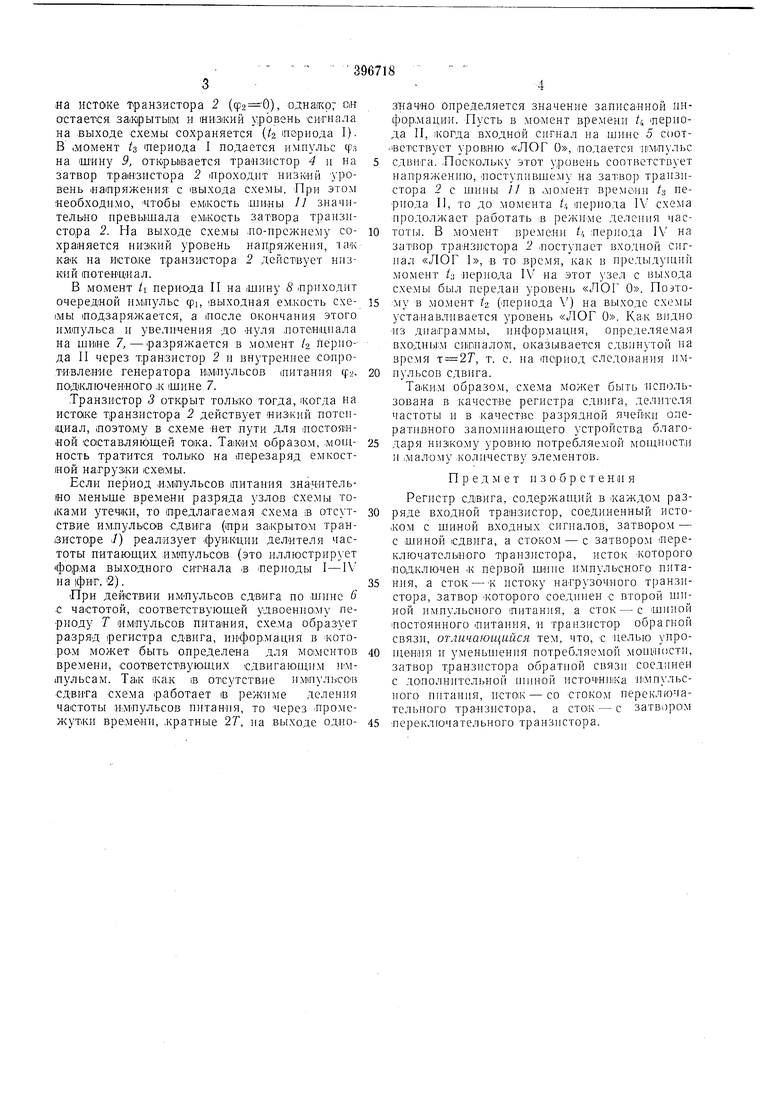

(На фиг. 1 представлена электрическая схема одного разряда регистра сдвига; яа фиг. 2 - временная диаграмма его работы.

PerncTip сдвига состоит из Входного /, переключательного 2 II нагрузоч.ного 3 транзисторов, а также транзистора 4 обратной свяЗИ. Исток транзи.стора / соединен с шиной 5 входных сигналов, затвор-с шиной 6 сдвига, исток транзистора 2-с первой шиной 7 импульсного питания, затвор транзистора 3-

с второй ШИНОЙ 8 импульсного питания, затвор транзистора 4-с дополнительной шиной 9 импульсного питания, сток транзистора 3 - с шиной 10 постоянного п тания, а обш,ая точка истока транзистора 3 и стока транзистора 3 - с выходной шиной 11 разряда ipeniстра сдвига.

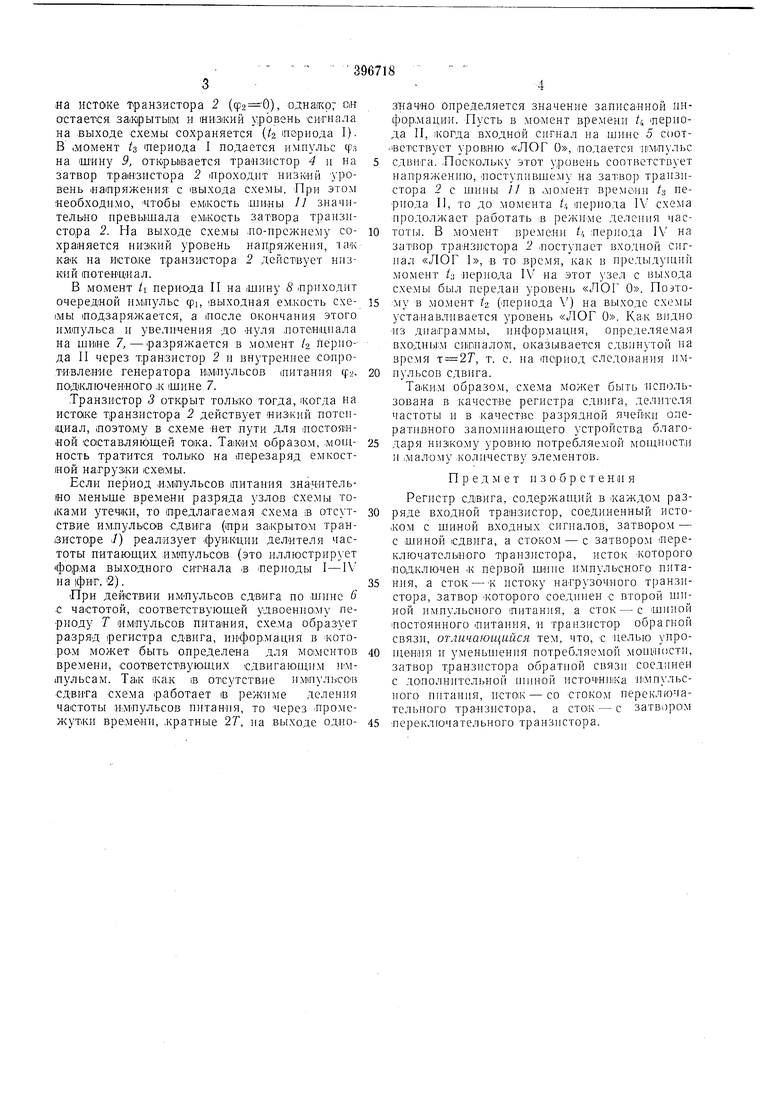

На фиг. 2 обозначено; 12 - временное расположение импульсов ф1, поступающих по второй шине импульсного питанпя; 13 - временное расположение импульсов ф2 по иервой шине импульсного питания; 14 - .временное раополол ение импульсов фз по дополнительной шине; /5 - временное расположение импульсов по шине сдвига; 16 - временное расположение импульсов на входной ши.не; 17- В|ременное расположение пмпульсо.в на выходной шине регистра сдвига.

Пусть в исходном положении (момент /о на фиг. 2) на шине 7 действует низкий уровень напряжения фа, а на пщнах 8, 9, 6, 11 и на затворе тра.нзистора 2 - высокие уровни. В мОмент /1 периода I приходит имиульс ф1 «а ши.иу 8 и выход шины // заряжается через транзистор 3 от источника питания, подключенного к шине 10. Так как при этом транзистор 4 закрыт, то на затворе транзистора 2 сохраняется потеИЦиал.

По окончании дейстВИЯ импульса .питания на шИНе 8 (ф1 0), увеличивается потенциал

на истоке транзистора 2 (), однако; ои О€тает1ся, замрытым и 1НИ:3 Кий у;рЬвень сигнала на выходе схемы сохраняется (t-i иериода I). В (Момент /3 периода I подается имлульс Фз на шину 9, открывается транзистор 4 на затвор тратзлстора 2 1проходнт низкий лровень иапряжения с выхода схемы. При этом

:шн«ы // значинеобходимо, чтобы емкость затвора траизнтельно превышала еМ|КОСть стора 2. На выходе схемы ло-прсжнему сохраняется низкий уровень наП|ряження, так 2 действует низкаК на HicTOiKe транзистора кий оотенциал.

В момент /I периода II на шину & .нриходит очередной имнульс фь 1выходная ем,кость схемы лодзаряжается, а 1после окончания этого имнульса и увеличения до нуля лотенниала на шине 7,-разряжается в момент /а периода II через транзистор 2 и внутреннее сопротивление генератора вмнульсов (нитания фаподключенного .к шине 7.

Транзистор 3 от1фыт только тогда, когда на истоке транзистора 2 действует низкий иотсн|циал, поэтоиму в схеме нет пути для ностоян«ой составляющей тока. TaiKHM образолт, мощность тратится только на лерезаряд емкостной нагрузки схамы.

Если период и.мпульсов литания значительно меньше времени разряда узлов схемы то|ками утечки, то предлагаемая схема IB отсутствие имлульсов сдвига (три закрытОМ транзисторе I/) реализует функции делителя частоты питающих имтульсав (это иллюстрирует фор:ма выходного ситнала IB периоды I-IV на фиг. 2).

При действии иМПульсов сдвига по шине 6 с частотой, соответствующей удвоенному периоду Т «мшульсов питания, схема образует разряд регистра сдвига, информация в которо м может быть определена для М01ментов времени, соответствующих сдвигающим иадлульсам. Так 1как IB отсутствие имиульсоа сдвига схема работает IB режиме деления частотЕз :И;Мнульсов питания, то Через .промежутки времени, кратные 2Г, на выходе однозначно определяется значение записанной инфор.мации. Пусть в момент времени 4 периода II, когда входной сигнал на шине 5 соот 1вет1ствует уровню «ЛОГ О, подается И1млульс сдвНга. Поскольку этот уровень соответствует нанря,, поступившему на затвор транзистора 2 с шины // в .момент времени /з периода II, то до момента ii, периода IV схема продолжает работать в режиме деления частоты. В момент времени /4 периода IV на затвор транзистора 2 поступает входной сигиал «ЛОГ 1, в то .время, как в предыдущий момент t--, периода IV на этот узел с выхода схемы был передан уровень «ЛОГ О. Позто му в момент t-i (периода V) на выходе схемы устанавливается уровень «ЛОГ О. Как видно из диаграммы, информация, оиределяемая входны;м еигналои, оказывается сдвинутой на время т 2Г, т. е. )ia период следования импульсов сдвига.

Таким образом, схема может быть использована в качестве регистра сдвига, делителя частоты и в качестве разрядной ячей-ки оперативного запомннающего устройства благодаря низ1кому уровню потребляемой мощ ности II |МаЛОму количеству элементов.

Предмет изобретения

Регистр сдвига, содержащий в .каждом разряде входной транзистор, соединенный истоком с шиной входных сигналов, затвором - с Шиной сдвига, а стоком - с затвором нереключателыного транзистора, исток которого подключен к первой шине имнульсного питания, а сток-к истоку нагрузочного транзистора, затвор которого соединен с второй И1Иной импульсного питания, а сток-с шшюи постоянного питания, и транзистор обра гной связн, отличающийся тем, что, с целью упроИ1ения и уменьшения потребляемой моииюсти, затвор транзистора обратной связи соединен с дополннтельной ищнОЙ источншка И1мпульспого питания, исток - со стоком переключательного транзистора, а CTOIK - с затворО М

переключательного транзистора.

/)П//////Г(/////ГУ////Х ////П/////Г ///// //.

TKfM

I I I h

К

// /////h

7 ///////////////// - /////

////ША

1//////////

j f 2 2 ifj 2 3 if / г з Ч г з I ЛШ IF ТГ

У VA Ш

I Г I J j II .,

I I I I

j/xfT-hy/////////////

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

| СДВИГОВЫЙ РЕГИСТР И ДИСПЛЕЙНОЕ УСТРОЙСТВО | 2010 |

|

RU2493621C2 |

| Динамический регистр сдвига | 1977 |

|

SU739655A1 |

| Усилитель считывания | 1981 |

|

SU1015435A1 |

| Адресный формирователь | 1979 |

|

SU955192A1 |

| Элемент памяти для динамического регистра сдвига | 1977 |

|

SU684617A1 |

| Стробоскопический преобразователь однократных импульсных сигналов с электрической регулировкой шага считывания | 1980 |

|

SU938160A1 |

| Динамический триггер на моптранзисторах | 1976 |

|

SU657594A1 |

| Цифровой сдвиговый регистр с зарядовой связью | 1976 |

|

SU600615A1 |

| Усилитель считывания на КМДП транзисторах | 1984 |

|

SU1241285A1 |

Авторы

Даты

1973-01-01—Публикация