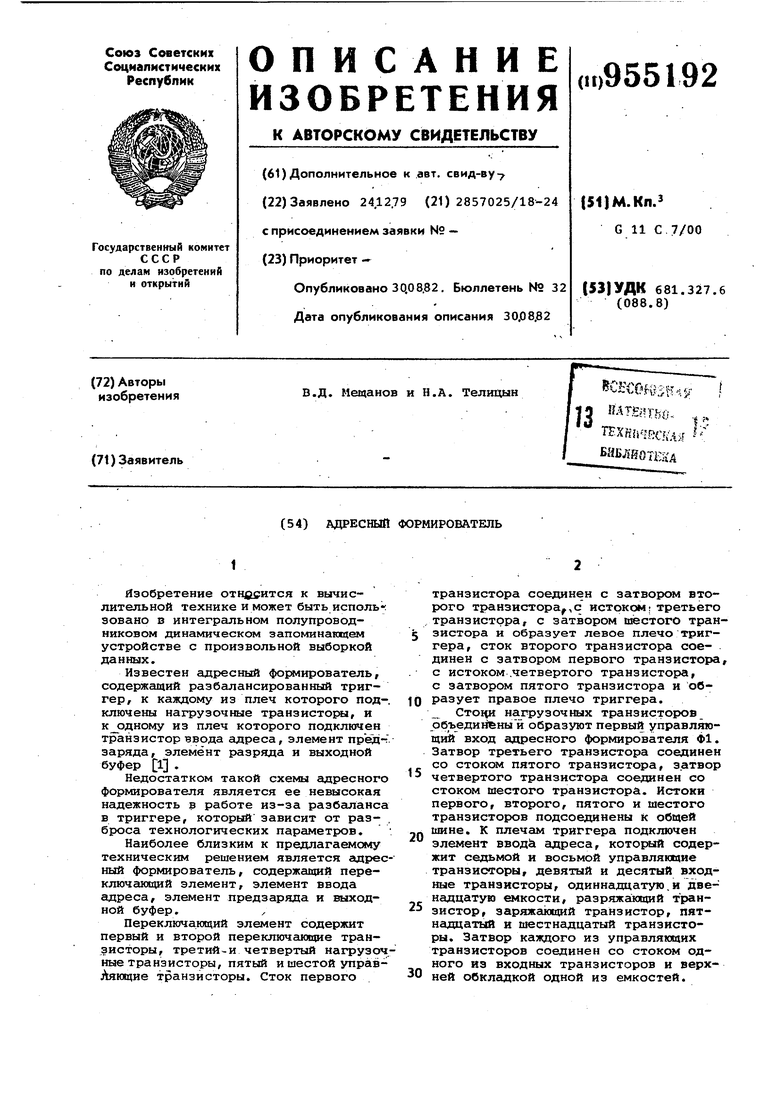

Изобретение отнасится к вычислительной технике и может быть исполь-; зовано в интегральном полупроводниковом динамическом запоминакжцем устройстве с произвольной выборкой данных.

Известен адресный фО 1ирователь, содержащий разбалансированный триггер, к каждому из плеч которого под-, ключены нагрузочные транзисторы, и к рдному из плеч которого подключен транзистор ввода адреса, элемент пред-Г заряда, элемент разряда и выходной буфер 1 .

Недостатком такой схемы адресного формирователя является ее невысокая надежность в работе из-за разбаланса в триггере, который зависит от разброса технологических параметров.

Наиболее близким к предлагаемому техническим решением является гщресшли формирователь, содержащий переключаилций элемент, элемент ввода адреса, элемент предзаряда и выходной буфер.

Переключающий элемент содержит первый и второй переключаюпще транзисторы, третий-и четвертый нагрузочные транзисторы, пятый и шестой управляющие транзисторы. Сток первого

транзистора соединен с затвором второго транзистора,с истоком; третьего транзистора, с затвором шестого транзистора и образует левое плечо триггера, сток второго транзистора сое- . динен с затвором первого транзистора, с истоком .четвертого транзистора, с затвором пятого транзистора и образует правое плечо триггера.

10

Стони нагрузочных транзисторов рбъедийеный образуют первый управляющ-яК вход адресного формирователя Ф1. Затвор третьего транзистора соединен со стоком пятого транзистора, з.атвор

15 четвертого транзистора соединен со стоком шестого транзистора. Истоки первого, второго, пятого и шестого транзисторов подсоединены к общей шине. К плечам триггера подключен

20 элемент вводе1 адреса, который содержит седьмой и восьмой управлякщие транзисторы, девятый и десятый входные транзисторы, одиннадцатую,и двенадцатую емкости, разряжалощий тран25зистор, заряжа1а1ций транзистор, пятнадцатый и шестнадцатый транзисторы. Затвор каждого из управляющих транзисторов соединен со стоком одного из входных транзисторов и верх30ней обкладкой одной из емкостей.

Стоки управляющих транзисторов подключены к плечам триггера. Исток одного из входных транзисторов образует вход адресного, а исток другого - вход опорного сигнала. Затвор четырнадцатого транзистора соединен с ИСТОКОМ пятнадцатого.и стоком шестнадцатого транзисторов, исток четырнадцатого транзистора соединен с затворами тринадцатого и шестнадцатого транзисторов и с первым управляющим входом адресного формирователя. Стоки тринадцатого и четырнадцатого транзисторов соединены с нижними обкладками одиннадцатой и двенадцатой емкостей. Сток пятнадцатого транзистора соединен с источником питания. Затворы девятого и десятого транзисторов соединены с входом элемента предзаряда и образуют второй управляющий вход адресного формирователя Ф 2. Истоки транзисторов седьмого, восьмого, тринадцатого и шестнадцатого соединены с общей шиной.

Стоки пятого и шестого транзисторов соединены с соответствующими входами элемента предзаряда и входами вцходного буфера, который имеет два выхода - прямой и инверсный и управляющий вход сигнала Ф 3 2 .

Недостатком такой схемы адресного формирователя является чувствительность задержки прохождения .сигнала зерез адресный формирователь н входному адресному сигналу из-за протекани сквозного тока через третий и седьмой транзисторы в момент подачи первого управляющего сигнала Ф1 йри входном адресном сигйале на стоке девятого транзистора равном 1 и отсутствия этого сквозного тока О сигнале на входе.

Этот недостаток понижает надежность работы адресного формирователи и усложняет условия синхронизации запоминающего устройства, в котором он может быть применен.

Цель изобретения - повышение надежности путем обеспечения нечувствительности задержки прохожде.ния сигна ла через адресный формирователь к вkoднoмy сигналу адреса, а также повышение быстродействия.

Поставленная цель достигается тем что в адресный формирователь, содержащий пере ключ акаций элемент, элемент ввода адреса, элемент предзаряда и выходной буфер, введены два разделит тельных транзистора, включенных между нагрузочными и управляющими транзисторами переключакядего элемента-, введен элемент разряда, содержащий . транзисторы заряда, разряда, включения и сброса, у которых затвор транзистора разряда соединен с истоком транзистора.включения и стоком транзистора сброса, истоки транзисторов разряда и сброса соединены с.общей

шиной, сток транзистора разряда соединен с истоком транзистора заряда и соединен с истоками ключевых и управляющих транзисторов переключающего элемента. Стоки транзисторов заряда и включения соединены с.шиной питания. Затвор транзистора включения соединен с первым управляющим входом адресного формирователя, затворы транзисторов заряда и сброса соединены с вторым управляющим входом адресного фор иройателя. А также элемент ввода адреса содержит два транзистора, соединенных по схеме триггера, плечи которого образуют выходы элемента ввода адреса, два входн ых транзистора, транзисторы управляющий, включения и сброса, у которых оток транзистора включения соединен с затвором одного из входных транзисторов и образует вход опорного сигнала, затвор второго входного транзистора образует вход адресного. сигнала. Сток каждого из входных транзисторов подключен к одному из истоков транзисторов, образующих триггер, истоки входных транзисторов соединены со стоком управляющего транзистора, затвор которого соединен с истоком транзистора включения и со стоком транзистора сброса. Затвор транзистора включения соединен с первым управляющим входом адресного формирователя, затвор транзистора сброса соединен с вторым управляющим входом .адресного формирователя. Истоки транзисторов управлякнцего и сброса соединены с общей шиной.

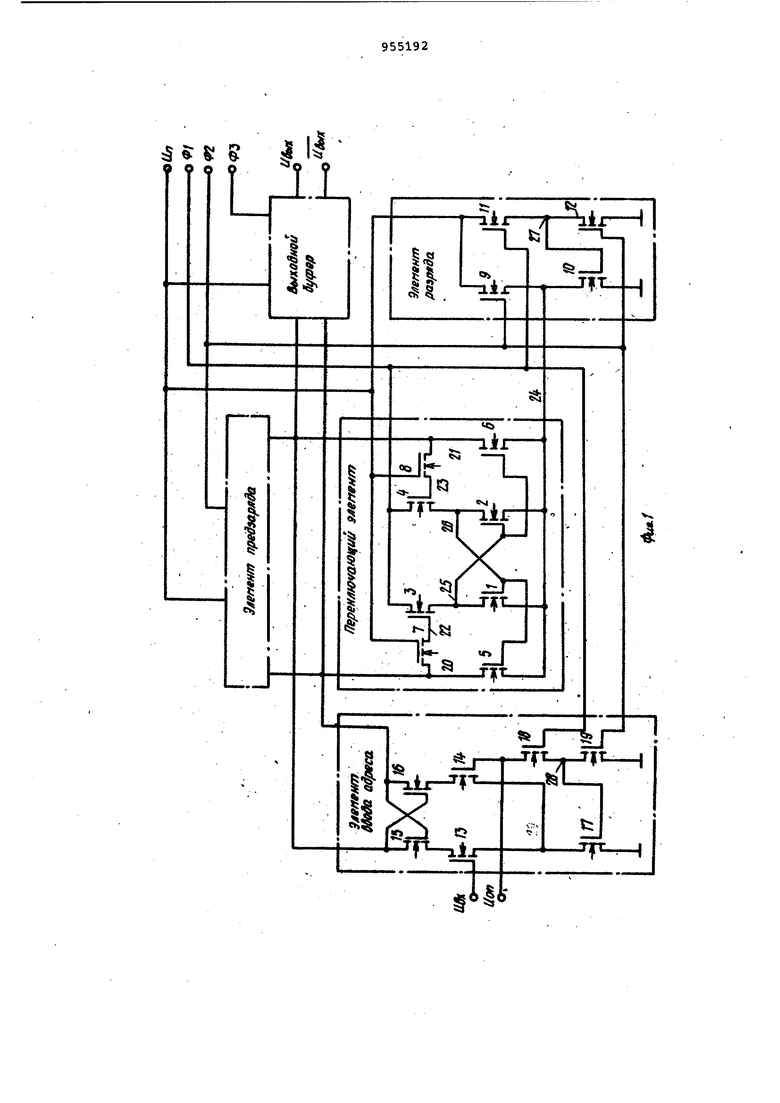

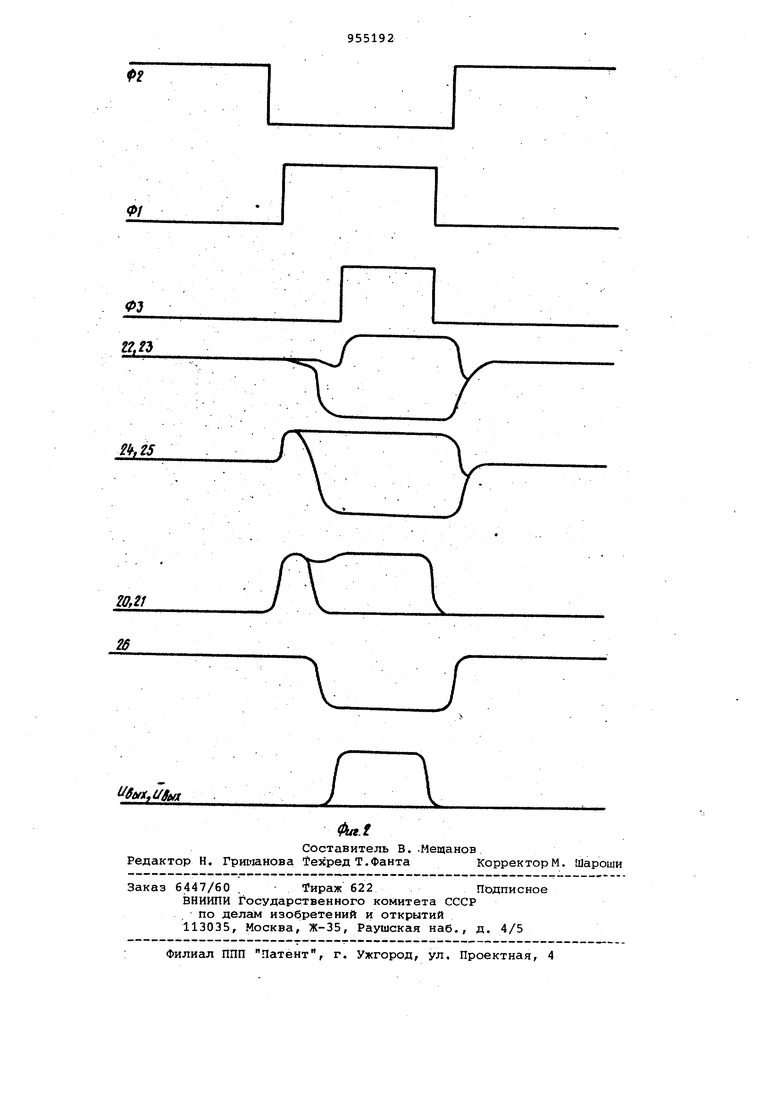

На фиг.1 изображена схема адресного формирователя на фиг.2 - временные диаграммы работы адресного формирователя.

Адресный формирователь содержит переключающий элемент, элемент разряда, элемент ввода адреса, элемент предзаряда и выходной буфер. Переключающий элемент содержит первый i и второй 2 переключаклцие транзисторы, третий 3 и четвертый 4 нагрузочные транзисто1ХЛг пятый 5 и шестой 6 управляющие транзисторы, седьмой 7 и восьмой 8 разделительные транзисторы. Сток первого транзистора соединен с затворами второго и шестого и с истоком третьего транзистора. .Сток второго транзистора соединен с затворами первого и пятого и с истоком четвертого транзисторов. Исток седьмого транзистора соединен с затвором третьего транзистора, исток восьмого транзистора соединен с затвором четвертого.транзистора. Стоки пятого и седьмого транзисторов соединены с первым выходом элемента предзаряда, стоки шестого и восьмого транзисторов соединены с вторым выходом элемента предзаряда. Затворы седьмого и восьмого транзисторов соединены с источником питания. Стоки третьего и четвертого транзисторов объединены и образуют первый управляющий вход адресного формирователя Ф 1. Элемент разряда содержит транзисторы заряда 9, разряда 10, включения 11 и сброса 12, у которых затвор транзистора разряда соединен с истоком транзистора включения и стоком транзистора сброса. Сток - транзистора раз ряда соединен с истоком транзистора заряда и s истоками переключающих и управляющих транзисторов переключакядего элемента. Стоки транзисторов включения и заряда соединены с источником питания. Истоки транзисторов разряда и сброса соединены с общей шиной. Затвор транзистора включения соединен с первым уп, равляющим входом адресного формиро.вателя. Затворы транзисторов заряда и сброса соединены с входом элемента предзаряда и образуют второй управляющий вход адресного формирователя Ф 2. Элемент ввода адреса содер жит отри надцатый 13 и четырнадцатый 14входные транзисторы, пятнадцатый 15и шестнадцатый 16 транзисторы, со диненные в виде триггера, плечи которого образуют выходы элемента ввода .адреса, транзисторы управляющий 17, включения 18 и сброса 19. Сток транзистора включения соединен с зат вором четырнадцатого входного транзистора и образует вход опорного сигнала, сток каждого из входных транзисторов соединен с истоком одного из транзисторов, образующих триггер. Истоки входных транзисторов соединены со стоком управляющего . транзистора, затвор которого соединен с истоком транзистора включения и со стоком транзистора сброса. Затвор транзистора включения соединен с первым управляющим входом, затвор транзистора сброса - с управляющим входом адресного формирователя. Истоки транзисторов сброса и управляющего соединены с общей пшной Затвор тринадцатого входного транзистора образует адресный вход форми рователя. Выходы элемента ввода адае са соединены с выходами эяемента предзаряда и с входами выходного буфера именадезх) два выхода - прямой U.gyji и инверсный tfgy и третий управляю1чий вход сигнала ФЗ. В исходном состоянии на первом и третьем управляющих входах установл низкий уровень напряжения сигналов Ф1 и ФЗ, на втором управляющем вход высокий уровень напряжения сигнгша Ф2. Транзисторы 9,12 и 19 - находят ся в открытом состоянии, на выходах элемента предзаряда установлен высо кий уровень напряжения. Узлы 20-24 заряжены .до высокого уровня напряжения,, в узлах 25-28 установлен нулевой уровень напряжения. На адресный вход подан адресный сигнал и ex.. На вход опорного сигнала nqдан опорный сигнал U , величина которого равна где ITg , Ug - соответственно максимальное значение уровня О, и минимальное значение уровня 1 входного адресного сигнала.: При входном адресном сигнале равном единице, т.е. 2,4 вг , узел :28 заряжается до напряжения V2g Ue)c -V-r Uon-Vf где VT- пороговое напряжение транзистора, поэтому транзистор 14 закрыт rid цепи истока. В начале рабочего интервала высокий уровень сигнала Ф2 снимается, транзисторы .9, 12 и 19 переходят в закрытое состояние, выключается элемент предзаряда и подается высокий уровень сигнала, Ф1. Транзистор 18 открывается и на затворе транзистора 17 устанавливается напряжение опорного источника, транзистор 17 переходит в проводящее состояние и начинает разряжать узел 28. Размеры транзисторов 15,16 13, 14 и 17 выбраны таким образом, чтобы транзистор 14 продолжал оставаться в закрытом состоянии. Одновременно через открытые транзисторы 3 и 4 начинается заряд узлов 20 к 21., При этом за счет бутстрапчуго действия емкостей затвор канал транзисторов 3 и 4 напряжение в узлах 24 и 25 повышается и транзисторы 7и 8 оказываются закрытыми по цепи i истока. Через открытые транзисторы 15,13 и 17 начинается разряд узла 23, Суммарная етлкость в узле 23, к которому подключены стоки транзйс торов 6,8 и 15, выход элемента предзарйда. Вход выходного буфера и затвор транзистора 16 во много;-.раз больше емкости в узле 25, к которому подключен исток транзистора 8 и затвор транзистора 4. . Поэтому небольшое уменьшение потенциала в узле 23 приводит к резкому уменьшению потенциала в узле 25, Транзистор 14 продолжает .оставаться в закрытом состоянии, поэтому узел 22 .не разряжается и потенциал в узле 23 остается высоким. К этому м(1енту времени через открытый транзистор 11 на затворе разряжающего транзистора 10 устанавливается высокий уровень напряжения, транзистор 10 переходит в открытое состояние и начи.нает разряжать общий узел 26. 8следствие понижения потенциала в узле 25, проводимость нагрузочного транзистора 4 оказывается меньше, чем проводимость нагрузочного транзистора 3, узел 21 разряжается а узел 2& остается заряженньлм до высокого уровня напряжения, происходит ускоренный разряд узлов 23 Ч 25, через открытые транзисторы б и. 10, а в узлах 22 и 24 сохраняются высокие уровни напряжения. После разряда узла 23 транзистор 14 выходит из закрытого состояния, поскольку н его истоке в узле 28, устанавливается нулевой уровень напряжения. Однако разряд узла 22 через транзисторал 16,14 и 17 не происходит благодаря закрытому состоянию тра.нзистора 16, на затворе которого устанавливается чулевой уровень напряжения.

В результате на входах выходного буфера,, подключенных кузлам 22 и 23, устанавливается разностный сигнал, соответствующий входному адресному сигналу Ugx. После этого подается высокий уровень сигнала Ф 3 и на выходах выходного буфера устанавливаются соответствующие выходные сигналы я Овых . По истечении необходимого времени вьщержкн адреса высокие уровня сигналов Ф1 и ФЗ снимаются и подается высокий уровень сигнала Ф2, адресный формирователь переходит в исходное состояние.

Работа адресного формирователя при нулевом адресном сигнале на ег9 входе аналогична работе при единичном входном сигнале.

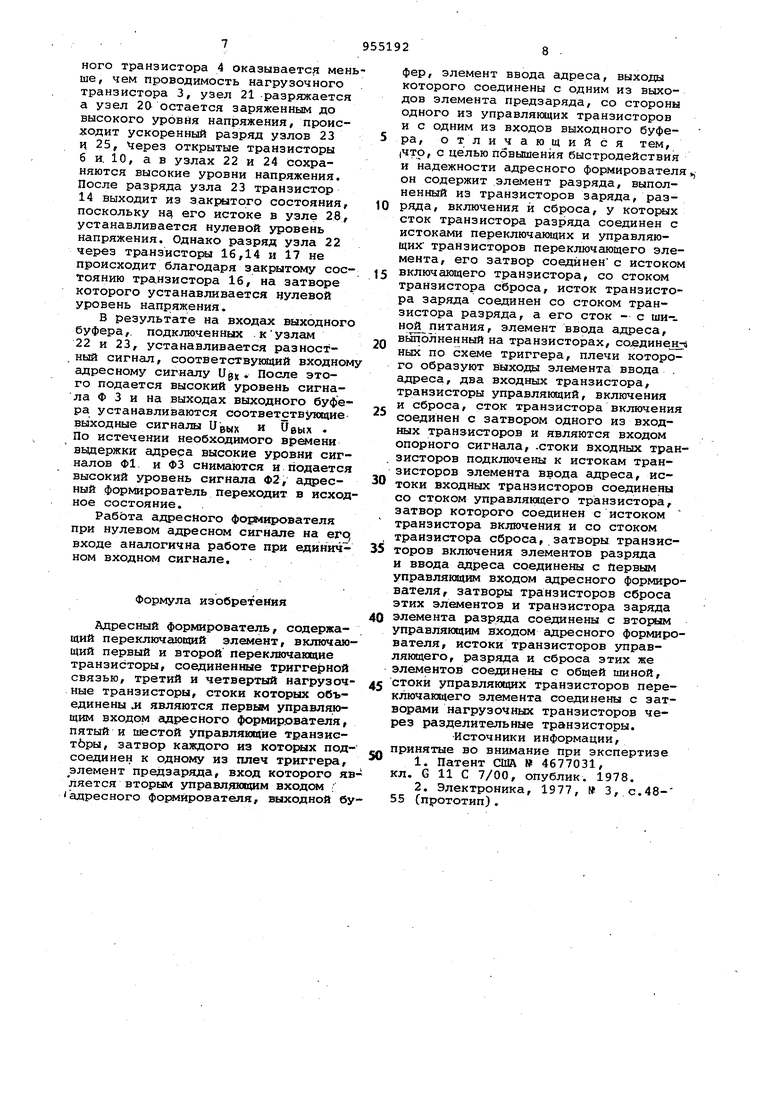

Формула изобретения

Адресный формирователь, содержащий переключающий элемент, включающий первый и второй переклю14аю1цие транзисторы, соединенные триггерной связью, третий и четвертый нагрузочные транзисторы, стоки которых объединены м являются первым управляющим входом адресного формиррвателя, пятый и шестой управляющие транзистбры, затвор каждого из которых подсоединен к одному из плеч триггера, элемент предзаряда, вход которого является вторым 5шравлдющим входом адресного формирователя, выходной буфер, элемент ввода адреса, выходы которого соединены с одним из выходов элемента предзаряда/ со стороны одного из управляющих транзисторов и с одним из входов выходного буфера, отличающийся тем, (ЧТО, с целью повышения быстродействия и надежности адресного формирователя он содержит элемент разряда, выполненный из транзисторов заряда, разряда, включения и сброса, у которых сток транзистора разряда соединен с истоками переключающих и управляющих транзисторов переключающего элемента, его затвор соединен с истоком включающего транзистора, со стоком транзистора сброса, исток транзистора заряда соединен со стоком транзистора разряда, а его сток - с ши-нрй питания, элемент ввода адреса, ВЕшолненный на транзисторах, co динej ных по схеме триггера, плечи которого образуют выходы элемента ввода . адреса, два входных транзистора, транзисторы управляющий, включения и сброса, сток транзистора включения соединен с затвором одного из входных транзисторов и являются входом опорного сигнала, -стоки входных транзисторов подключены к истокам транзисторов элемента ввода адреса, истоки входных транзисторов соединены со стоком управлякнцего транзистора, затвор которого соединен с истоком транзистора включения и со стоком транзистора сброса, затворы транзисторов включения элементов разряда и ввода адреса соединены с Первым управлякадим входом адресного формирователя, затворы транзисторов сброса этих элементов и транзистора заряда элемента разряда соединены с управляющим входом адресного формирователя, истоки транзисторов управляющего, разряда и сброса этих же элементов соединены с общей шиной, стоки управляющих транзисторов переключаклцего элемента соединены с затворами нагрузочных транзисторов через разделительные транзисторы.

Источники информации, принятые во внимание при экспертизе

1.Патент США 4677031,

кл. G 11 С 7/00, опублик. 1978.

2.Электроника, 1977, № 3, с.4855 (прототип).

J ij

Г

:§§: 5

« 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Адресный формирователь | 1988 |

|

SU1624521A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Формирователь импульсов | 1982 |

|

SU1091327A1 |

| Адресный формирователь | 1981 |

|

SU1014027A1 |

| Адресный формирователь | 1981 |

|

SU970460A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Формирователь импульсов | 1985 |

|

SU1374416A1 |

| Усилитель считывания | 1981 |

|

SU1015435A1 |

Авторы

Даты

1982-08-30—Публикация

1979-12-24—Подача