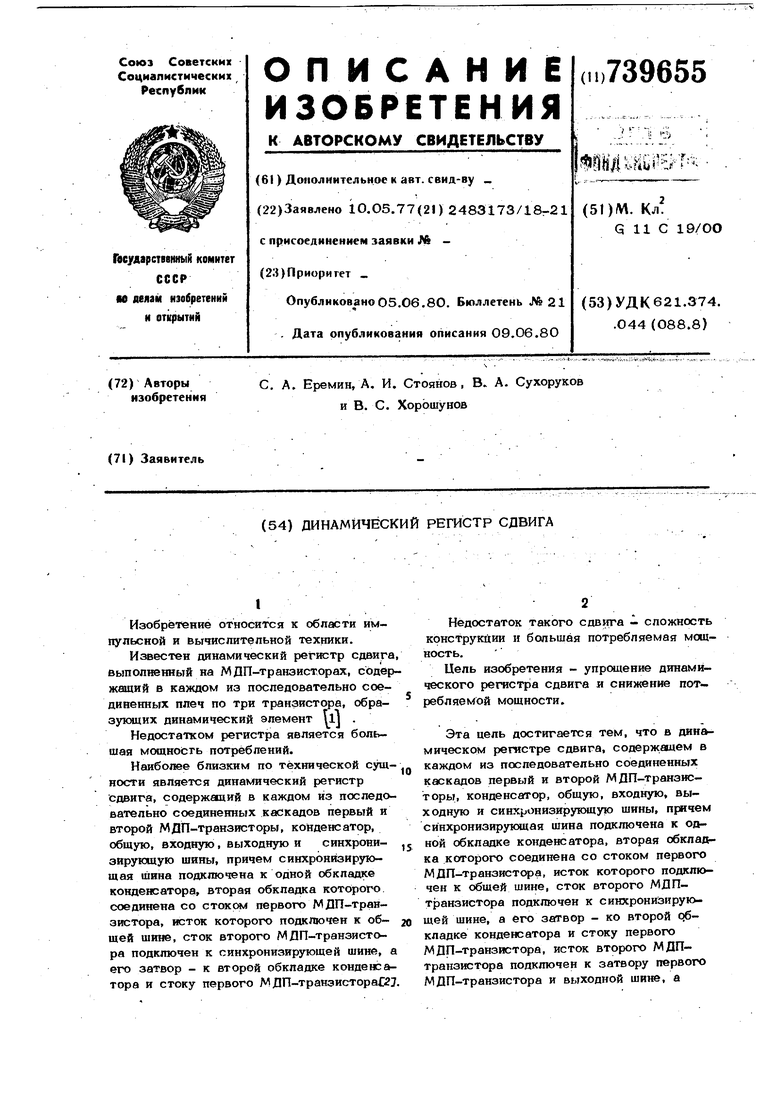

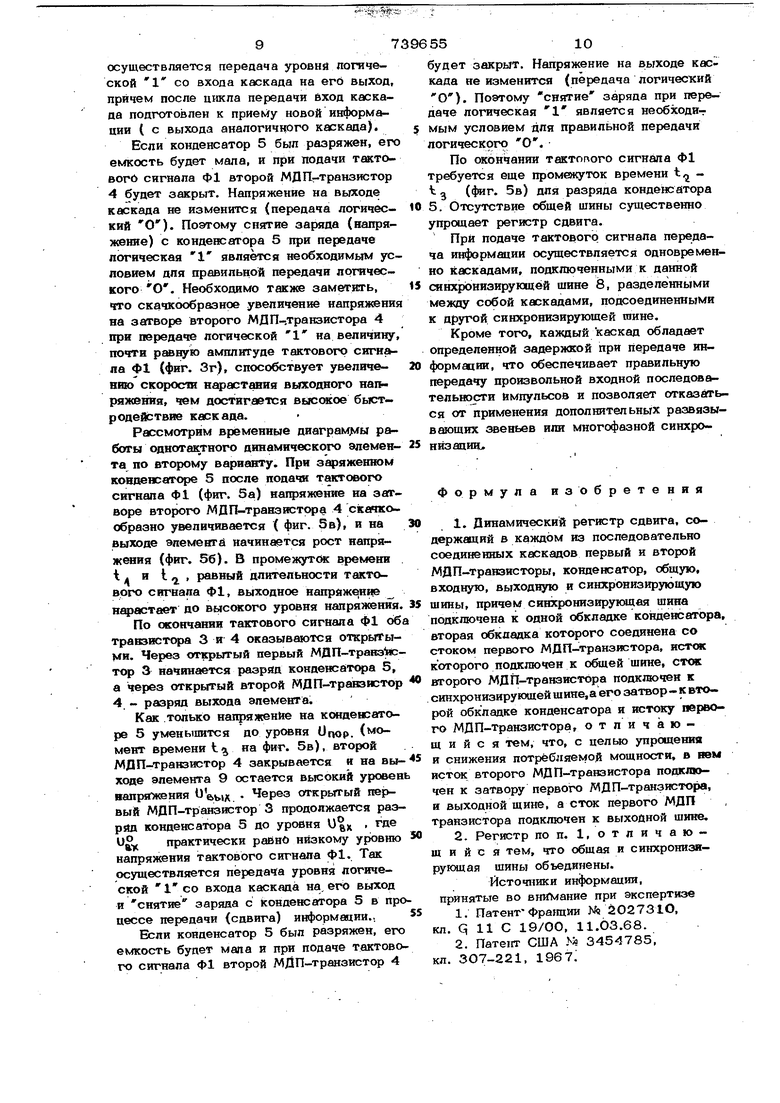

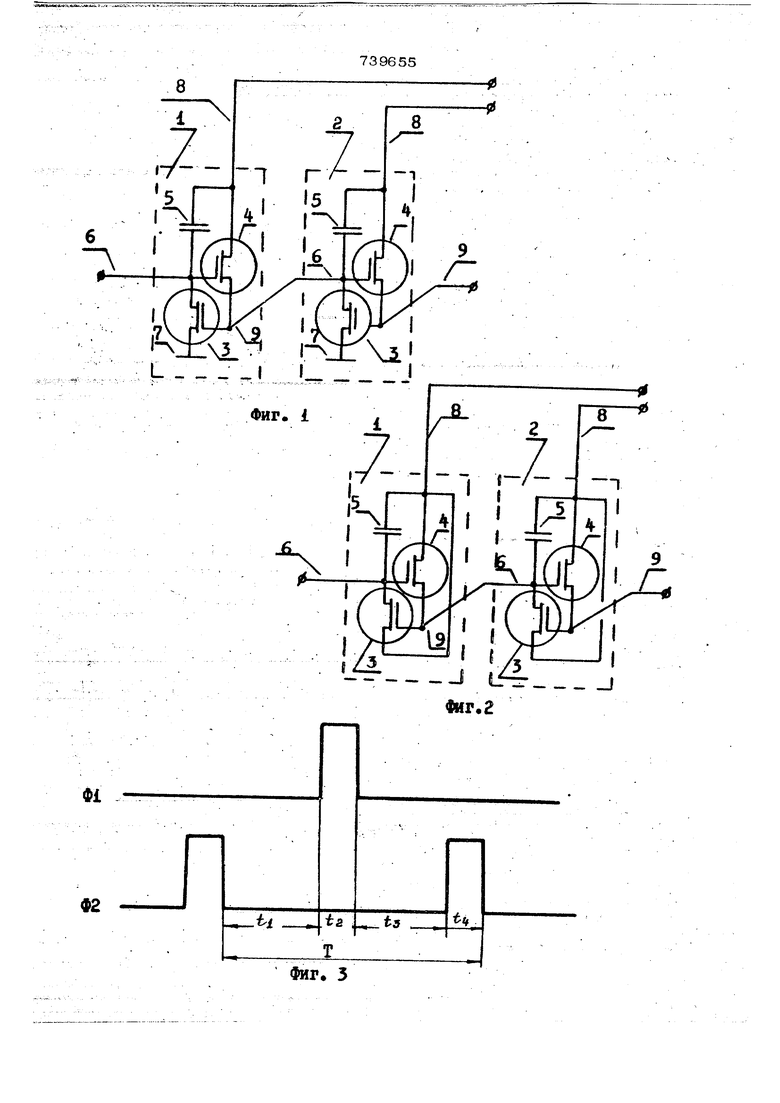

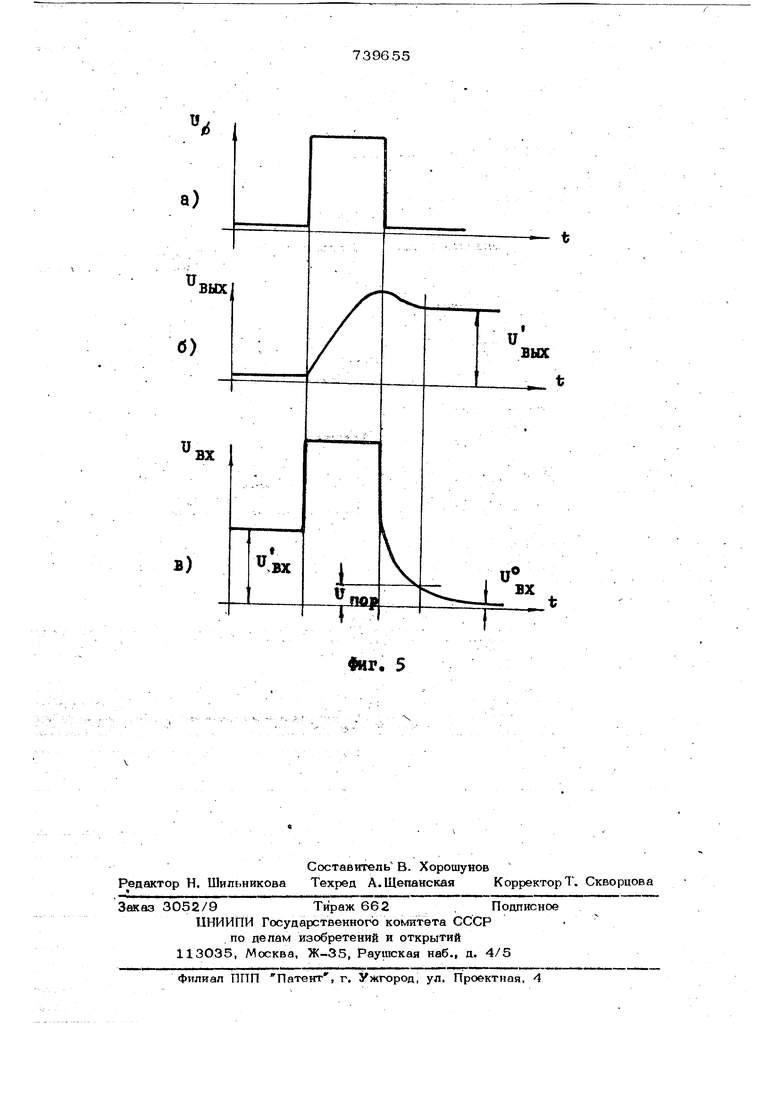

Изобретение относится к области импульсной и Вычислительной техники. Известен динамический pefHCTp сдвига выполненный на МДП-транзисторах, содер жащий В каждом из последовательно соединенных плеч по три транзистора, образующих динамический элемент Ш . Недостатком регистра является большая мощность потреблений. Наиболее близким по технической сущ ности является динамический регистр сдвига, содержащий в каждом из последо вательно соединенных каскадов первый и второй МДП-транзисторы, конденсатор, общую, входную, выходную и синхронизирующую шины, причем синхронизирующая шина подключена к одной обкладке конденсатора, вторая обкладка которого соединена со стоком первого /ИДП-транзистора, исток которого подключен к общей шине, сток второго МДП-транзистора подключен к синхронизирующей шине, его затвор - к второй обкладке конденса тора и стоку первого W ДП-транзистораСг Недостаток такого сдвига - сложность конструкции и большая потребляемая мощность. Цель изобретения - упрощение динамического регистра сдвига и снижение потребляемой мощности. Эта цель достигается тем, что в динамическом регистре сдвига, содержацем в каждом из последовательно соединенных каскадов первый и второй МДП-транзисторы, конденсатор, общую, входную, выходную и синхр1)низирующу10 шины, причем синхронизирующая шина подключена к одной обкладке конденсатора, вторая обкладка которого соединена со стоком первого МДП-транзистора, исток которого подключен к общей шине, сток второго МДПтранзистора подключен к синхронизирующей шине, а его зеггвор - ко второй рбкладке конденсатора и стоку первого МДП-транзистора, исток второго МДПтранзистора подключен к затвору первого МДП-транзистора и выходной шине, а сток первбго МДП-транзистбра подключен к входной шине, кроме того, общая и стгахронизирующая шины объелинены. На фиг. 1 представлена схема динамического регистра сдвига по первому варианту; на фиг. 2 - то же.по второму вйрканту; на фиг. 3 - период слейования тактовых сигналов; на фиг. 4 - вре|угенные диаграммы дли элемента по первому рарианту; на фиг . 5 - то же,по второму вариВ регистре сдвига, содержащем в каждом из последовательно соединенных каскадов 1 и 2 первый МДП-транзистор 3., второй МДП-транзистор 4, конденсатор 5, входную шину 6, общую шину 7 и синхро, низирующую шину 8 и вы :однуюшину 9. Синхронизирующая шина 8 подключена к одной обкладке конденсатора 5 и стоку второго МДП-транзистора 4, вторая обкладка конденсатора 5 соединена со стоко первого МДП-транзистора 3, затвором вто рого МДП-транзистора 4 и входной шиной 6, исток второго МДП-транзистора 4 объе динён с выходной шиной 9 и с затвором первого МДП-транзистора 3, исток которого связан с общей шиной 7. По второму варианту общая шина 7 в каждом из последовательно соединенных каскадов 1 и 2 объединена с синхронизирующей щиной 8 (фиг. 2) . Динамический регистр сдвига работает следующим образом. Каждый разряд регистра сдвига содержнт два последовательно соединенных кас када 1 я 2, на синхронизирующие шины ко торых подаются неперекрывающиеся во времени тактовые сигналы Ф1 и Ф2. Рассмотрим работу двухразрядного дин |М11ческого регистра сдвига. Подача входной информации ocyniiectвпяётся в промежуток временив предыдущего и ty, данного цикла, а вывой информации - в промежуток времени t- . ,. ного цикла и i . последующего. В таблице приведена циклограмм) прохождения информация за 8 циклов тактовых сигнале. /: Под циклом тактовых си напбё пони мается период следования тактовых сигна лов (фиг. 3). В цтслограмме рассмсйгрен процесс передачи последовательности 1-1-0-О-1-О-1, где символами 1 и О обозначены соответственно высокий и низкий уровни напряжений (уровень логическая 1 и логический О ). Пусть в исходном состоянии конденсаторы 5 каскадов 1 и 2 разряжены. В промежуток t первого цикла в соответстёии с передаваемой последовательностью на вход регистра 6 подается высокий уровень напряжения. На Ф2 первого цикла (промежуток времени t) одновременно осуществляется передача информации первым и третьим каскадами, на выходную шину 9 первого каскада передается высокий уровень напряжения, входная шина 6 первого каскада обнуляется, на выходной шине 9 третьего каскада остается низкий уровень напряже гая, так как его конденсатор 5 был разряжен. В промежуток времени 1 состояние элементов регистра сдвига не меняется. При подаче тактового сигнала Ф2 (пр&межуток времени Ц ) одновременно осуществляется передача информ.ации вторым и четвертым каскадами. На вход регистра 6 информация подается с выхода аналогичного каскада и, следовательно, поступает с задержкой относительно переднего фронта тактового сигнала Ф2. Поэтому при Воздействии тактового сигнала Ф2 высокий уровень напряжения передается на выход 9 второго каскада прежде, чем открывшийся второй МДП-транзистор первого каскада успеет разрядить конденсатор 5 и закрыть второй МДП-транзистор второго каскада, Затем входная шина 6 второго каскада обнуляется, на выходе регистра сдвига остается йизкий уровень напряжения, так как конденсатор 5 i eTBepTbro каскада был разряжен. В промежуток времени t второго цикла состояние элементов регистра cziBHra не меняется. При воз хействии тактового сигнйэла ф1 второго цикла снова осущест.«. вляется передача информации каскадами nepBbiM и третьим и т .д. Поданный в первом цикле входной высокий уровень напряжения появляется йа выходе регист,,а при воздействии тактового сигнала Ф2 второго цикла. .Дальней шее прохождение информации иллюстрируется таблицей.

1 2 3 4

1 О О 1

1

1 О О О

2 3 4

о о о

о о о о

о о о о

1

о 1 1 о

о о о 1

1

о о

1

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2542913C1 |

| Устройство согласования на мпд-транзисторах | 1973 |

|

SU661797A1 |

| СДВИГОВЫЙ РЕГИСТР (ВАРИАНТЫ) | 2013 |

|

RU2530271C1 |

| Регистр сдвига | 1975 |

|

SU550678A1 |

| Ячейка памяти для регистра сдвига | 1977 |

|

SU680055A2 |

| Ячейка памяти для регистра сдвига | 1980 |

|

SU902075A1 |

| Запоминающая ячейка для регистра сдвига | 1974 |

|

SU519763A1 |

| Динамическая ячейка памяти | 1974 |

|

SU523454A1 |

| Ячейка памяти на мдп-транзисторах | 1975 |

|

SU533988A1 |

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

1

О

О

О

О

1

о о о

2 3 4

р о о о

1

о о о 1

о о о

б 1 1 о

о о о 1

1 о о о

о о о о 77 Функция Хранения цифровой ин(})ормации реализуется конденсатором 5, величина емкости которого определяется величиной. хранимого на нем заряда. Когда на входе каскада была информация, со6тветствук шая логической 1, конденсатор 5 будет заряжен, а его емкость велика. Второй МДП-транзистор 4 будет открыт, первый МДП-гранзисТор 3 закрыт, а выход эле-мента 9 обнулен (разряжен), С приходом на синхронизирующую шину 8 тактового сигнала Ф1 второй МДПтранзистор 4 будет открыт (конденсатор 5 в данном случае играет роль ускоряющей , по входу элемента подключен выкод аналогичного каскада), напряжение на з&творе второго МДП-транзисто ро 4 относительно общей- шины 7 будет ра-зно сумме амплитуды тактового сигнала Ф1 и величины напряжения на конденсаторе 5. На выходе каскада формируется выспкий уровень напряжения, близкий к амплитуде тактового сигнала Ф1, При этом открывается первый МДПтранзистор 3 и снимает заряд с конденса тора 5, а второй М ДП-транзистор 4 закрывается. Выход элемента 9 остается заряженным до высокого уровня напряжения. Соотношения размеров транзисторов 3 и 4 (или пороговое напряжение первого МДП транзистора 3) выбираются такими, чтобы выход элемента 9 успел зарядиться до напряже(гая, близкого к амплитуде тактового сигнала прежде, чем произойдет полный разряд койденсатора 5. По окончании действия тактового сигнала вто рой М ДП-транзистор 4 будет закрыт, выход эпёМентга остается заряженным, первы М ДП-транзистор 3 открыт, конденсатор 5 разряжен. Таким образом, за время дейст вия одного тактового сигнала Ф1 вляется сдвиг (передача) логической 1 со входа каскада на его вьгход. Выход каскада 9 в цифровых устройст вах нагружен на вход аналогичнотЧ) каскада, конденсатор 5 которого принимает на хранение переданную информадию. После использования (сдвига) этой информации выход рассматриваемого элемента обнуляется (разряжается) и каскад oтoв к новому циклу пер)едачи информации. Так как энергия от источника такто0ЫХ сигналов Ф1 потребляется только во время переходного процесса, то статическое потребление мощности отсутствует, Если на входе каскада была информация, соответствующая Логическому О, конденсатор 5 будет разряжен, а его емкость- мала. Поэтому с приходом тактового сигнала Ф1 второй МДП-транзистор 4 будет закрыт, связи вы,ходной шины 9 с синхронизйрукадей шиной 8 не будет, по окончании действия .тактового сипнала выходная шина 9 элемента останется разряженной, и каскад готов к новому циклу передачи информации. Таким образом, осуществляется передача (сдвиг) логического О со входа каскада на его выход. По второму варианту каскад работает аналогично рассмотренному за исключением того, что разряд конденсатора 5 после передачи логической 1 осуществляется по окончании действия тактового сигнала Ф1 через первый М ДП-транзистор 3, Поэтому для исключения разряда выхода элемента через второй МДП-транзистор 4 соотношения размеров транзисторов 3 и 4 дсхпжны быть такими, чтобы конденсатор 5 успел разрядиться до напряжения, меньшего пороговой величины прежде, чем напряжение на выходе элемента смозиет заметно снизиться. Рассмотрим временные диаграммы работы каскада динамического регистра сдвига по первому варианту. При заряженном конденсаторе 5 (фиг. 46) после подачи тактового сигнала Ф1 (фиг. 4 а) напряжение на затворе второго МДП-транаистора 4 скачкообразно увеличивается (так как конденсатор -5 заряжен), (фиг. 4г), и йа вьпсоде элемента начинается рост напряжения (фиг. 4в). В промежутке времени tд - I напряжение на выходе каскада нарастает до уровня Опор где УПОР пороговое напряжение транзисторов. Транзистор 3 в этот период закрыт, а транзистор 4 - открыт. При достижении уровня напряжения Unop.P 43iiтор 3 открывается и начинается разрящ конденсатора 5, выходное напряжение элемента продолжает нарастать. Когда в момент времени 1 напряжение на обкладгках кондеьюатора 5 уменьшится до урЬвня ипор,,ьторой МДП-транзистор 4 закрывается, и на выходе элемента остается вььсокий уровень .шпряжения иаых, Первый МДП-транзистор 3 открыт, и разряд конденсатора 5 продолжается (промежуток времени 4 на фиг. 4 б,г). По окончании действия тактового сигнала Ф1 (i на фиг. 4 а) напряжение на входе каскада также изменяется, и через открытый транзистор 3 конденсатор 5 разряжается практически до уровня О. Таким образом. осуществляется передача уровни логической 1 со входа каскада на его выход, причем после цикла передачи вход каскада подготовлен к приему новой информации ( с выхода аналогичного каскада). Если конденсатор 5 был разряжен, его емкость будет мала, и при подачи тестового сигнала Ф1 второй МДП-транзистор 4 будет закрыт. Напряжение на выходе каскада не изменится (передача логический О). Поэтому снятие заряда (напряжение) с конденсатора 5 при передаче логическая I является необходимым условием для правильной передачи лршческого О. Необходимо также заметить, что скачкообразное увеличение напряжения на затворе второго МДП-.транзистора 4 при передаче логической на величину, почти равную амплитуде тактового сигнала Ф1 (фиг. Зг), способствует увеличению скорости нарастания выходного напряжения, чем достигается высокое быстродействие каскада. Рассмотрим временные диаграммы работы однотактного динамического элемента по второму варианту. При заряженном ковдепсаггсфе 5 после подачи тактового сигнала Ф1 (фиг. 5а) напряжение на запгворе второго МДП-транзистора 4 сквякообразно увеличивается ( фиг. 5в), и на выходе элемент и начинается рост напряжения (фиг. 56). В промежутсйк времени t д и I j , равный длительности тактового сигнала Ф1, выходное напряжен11е н астает до высокого уровня напряжения. По окончании тактового сигнала Ф1 oi6 транзистора 3 и 4 оказываются открытыми. Через открытый первый МДП-транз1истор 3 начинается разрйд конденса1тора 5, а через открытый второй МДП-травоистор 4 - разр$ш выхода элемента. Как .только напряжение на конденсаторе 5 уменьшится до уровня ОПОР, (момент времени t на фиг. 5в), второй МДП-транзистор 4 закрывается и на выходе элемента 9 остается высокий уровен напряжения J ЬЫА Через открытый первый МДП-транзистор 3 продолжается разряд конденсатора 5 до уровня VJ , где практически равно низкому уровню напряжения тактового сигнала Ф1. Так осуществляется передача уровня логической 1 со входа каскада на, его выход и снятие заряда с конденсатора 5 в про цессе передачи (сдвига) информации... Бели конденсатор 5 был разряжен, его емкость будет мала и при подаче тактового сигнала Ф1 второй МДП-транзистор 4 7 5510 будет закрыт. Напряжение на выходе каскада не изменится (передача логический О). Поэтому снятие заряда при передаче логическая является необходит мым условием для правильной передачи логического О. По окончании тактового сигнала Ф1 требуется еще промвкуток времени t t (фиг. 5в) для разряда конденсатора 5. Отсутствие общей шины существенно упрощает регистр сдвига. При подаче тактового сигнала передача информации осуществляется одновременно Каскадами, подключенными к данной синхронизирующей шине 8, разделенными между собой каскадами, подсоединенными к другой синхронизирующей шине. Кроме того, каждый каскад обладает определенной задержкой при передаче информации, что обеспечивает правильную передачу произвольной входной последовательнсхгги импульсов и позволяет отказсггься от применения дополнительных развязывающих звеньев или многофазной синхронйзацшьФормула изобретения 1. Динамический регистр сдвига, содержащий в каждом из последовательно соединенных каскадов первый и второй МДП-транзисторы, конденсатор, общую, входную, выходную и синхронизирующую щины, причем синхронизирующая шина подключена к одной обкладке конденсатора, вторая обкладка которого соединена со стоком первого МДП-транзнстора, исток которого подключен к общей шине, сток второго МДП-транзистора подключен к синхронизирующей щ ине, а его затвор - к второй обкладке конденсатора и истоку первого МДП-транзистора, отличающийся тем, что, с целью упрощения и снижения потребляемой мощности, в нем исток второго МДП-транзистора подал - чен к затвору первого МДП-транзистора, и выходной щ ине, а сток первого МДП транзистора подключен к выходной шине. 2. Регистр по п. 1, отличающий с я тем, что общая и синхронизирующая шины объединены. Источники информации, принятые во внимание при экспертизе 1.ПатентФрашии №2027310, кл. q 11 С 19/00, 11.63.68. 2.Патент США М« 3454785, кл. ЗО7-221.

Ф2

U-i7

.ia

Фиг. 3

t

tl t2 t5 t4

Фиг. 4

а)

«иг. 5

Авторы

Даты

1980-06-05—Публикация

1977-05-10—Подача