Р1з обретении с относится к Бычислитель;1ой тех1ннке. Известно устройство для суммирования в юистеме счисления с основанием (-2), содержащее блоки поразрядного сложенИя, триггеры .регистров слагаемых и логические схемы ценен Heipeiioca.

С целью унрощення в нредлагаемом устройстве нервый блок норазрядного сложения соедииен с едишг иыыи выходами иерво:го и второго триггеров И с ши;ной переноса из предыдущего .разряда, нулевые выходы иврвого и BTOpOiiO триггеров иодключаны к иервым схемам «PI и «ИЛИ, выход нервой схемы «II лодключеи iX од}юмуИЗ входОВ BTOipoii cxeNu i «ИЛИ, второй вход которой соединен с выходом второй схемы «И, связанной одним входо;М с выходом первой схемы «ИЛР, а вторым входом - с шиной -пербноса из иредыдущего разряда, выход второй схемы «ИЛИ. соедииен со входом второго блока норазряд11ого сложения, сБяза1Ь ного с нулевым и единичным выходами соответственно третьего и четвертого триггеров, единичные выходы которых иодключены к третьим схемам «И и «ИЛИ, иричем выход третьей схемы «И соединен с одним НЗ входов четвертой схемы «ИЛИ, второй вход которой соединен с выходом четзе; той схемы «И, соединенной первым входом с выходом третьей схемы «ИЛИ, а вторым входом - с выходом второй схемы «ИЛИ, БЫ2

ход четвертоГ| схемы «ИЛИ соединен с HUMioii иереноса в следующий разряд.

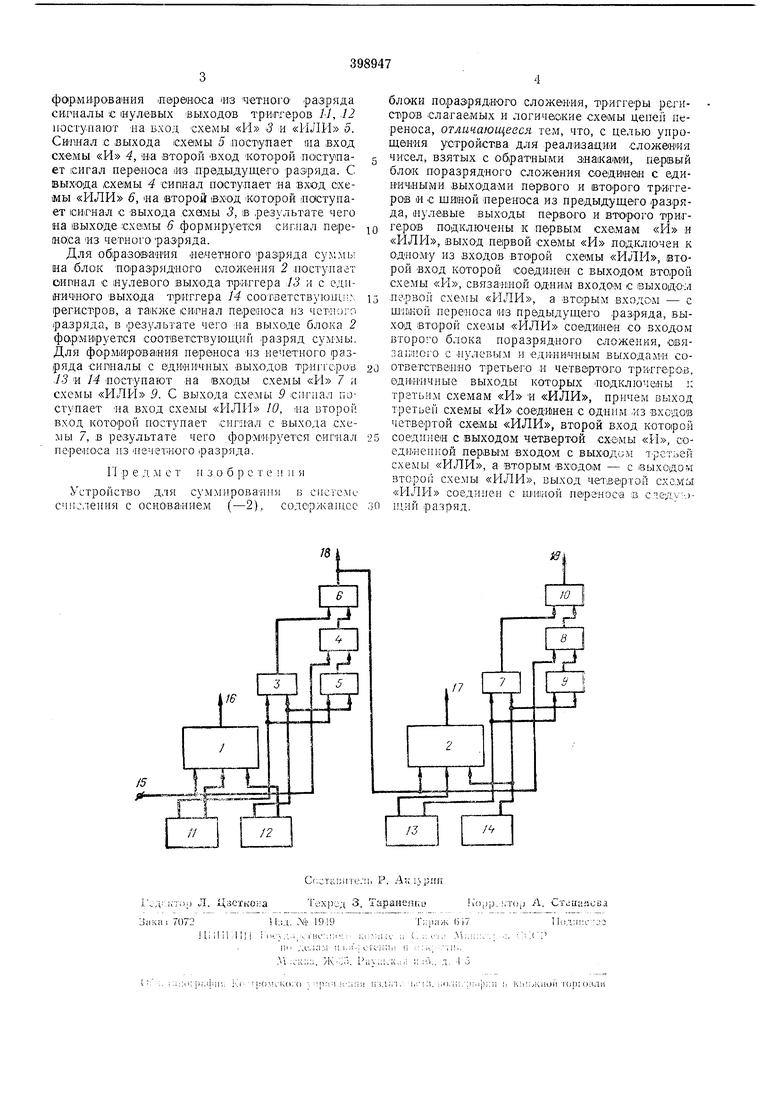

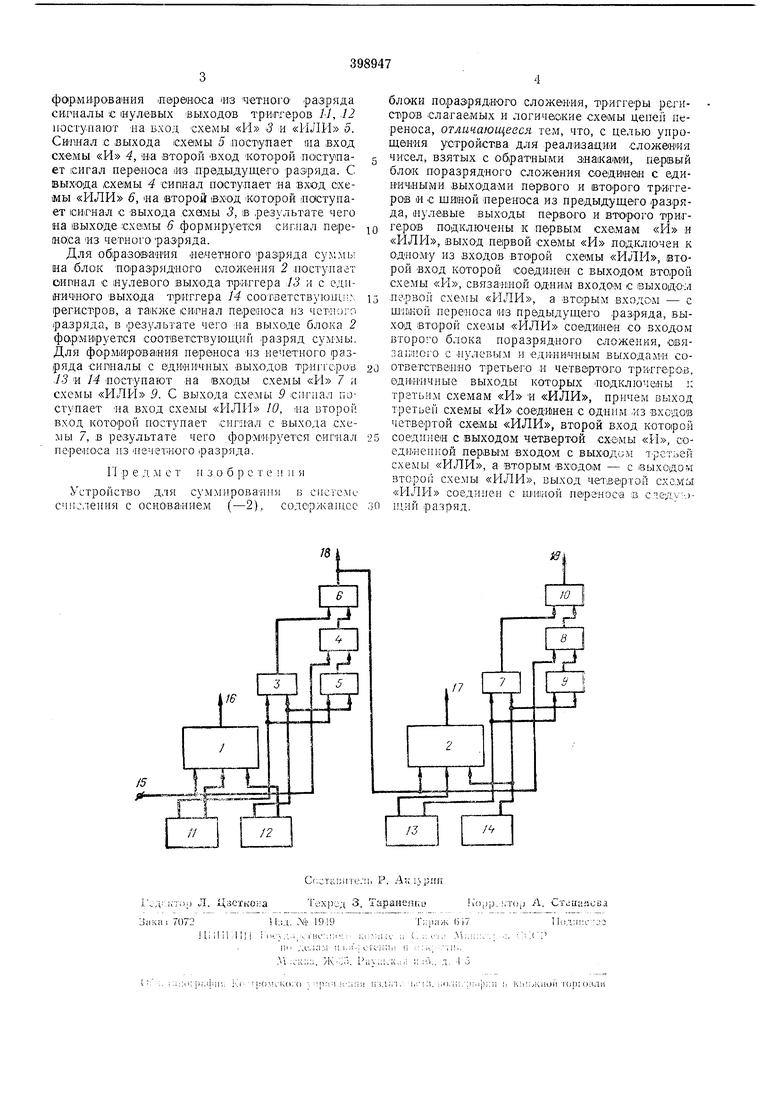

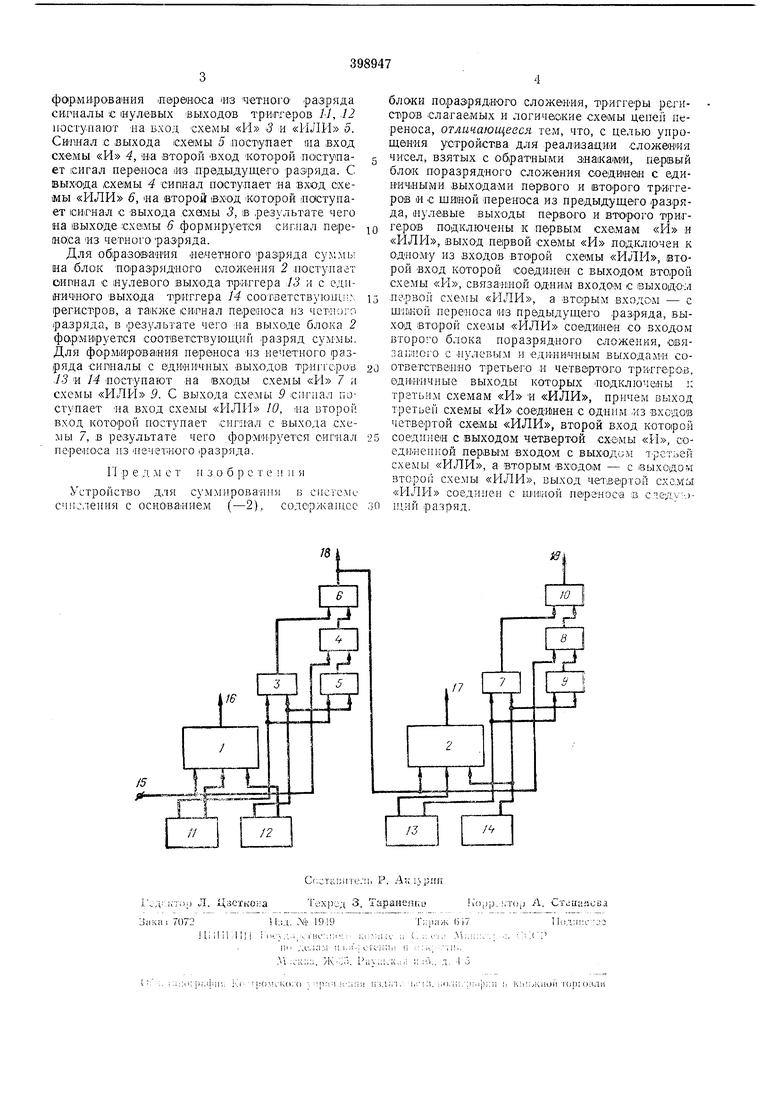

Схема предлагаемого :устройства для .суммирования в системе счисления с основани ем (-2) представлена на чертеже.

Схемы четно1-о и нечетного разрядов состоят из блоков поразрядного сложения 1 и 2 соответственно и ценей переноса, состоящих из логических схеМ «И 3 к 4 п схем «ИЛИ 5 и

6для четного разряда, и логических схем «И

7и S и схем «ИЛИ 9 и 10 для нечетного разряда. Триггеры П и 12 четного разряда пр инадлежат соответственно регистрам первого и второго слагаемых, триггеры 13 и 14 нечетного разряда - регистрам первого и второго слагаемых; 15 - Hj;nia сигнала переноса нз предыдушгго разряда; 16 и 17 - выходы норазряд1ых сумм соотзстственно четного и нечетного разрядов; 13 и 19 - выходы переносов соответствеппо чет-юго и нечетного разрядов.

Устройство работает следующим образом. Для образования четного разряда суммы, 1взятой с обратным знаком, на вход поразрядного сложения / поступают соответствующие разряды слагаемых с единичных выходов iipHrreров // и 12 регистров первого н второго слагаемых, а также сигнал переноса из предыдущего разряда. Выходной сигнал блока / представляет собой значенне соответствующего разряда суммы, взятой с обратным знаком. Дл-:

| название | год | авторы | номер документа |

|---|---|---|---|

| КОМБИНАЦИОННЫЙ СУММАТОР | 1969 |

|

SU236858A1 |

| СУММАТОР В КОДЕ ГРЕЯ | 1965 |

|

SU172131A1 |

| ДВОИЧНЫЙ ПАРАЛЛЕЛЬНЫЙ СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 1973 |

|

SU378844A1 |

| Последовательный сумматор | 1989 |

|

SU1709298A2 |

| ДВОИЧНО-ДЕСЯТИЧНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР | 1971 |

|

SU293241A1 |

| Сумматор последовательного действия | 1989 |

|

SU1689945A2 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| Последовательный сумматор | 1988 |

|

SU1571573A1 |

| Арифметико-логическое устройство | 1987 |

|

SU1495782A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ В ТРОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ НА НЕЙРОНАХ | 2010 |

|

RU2453900C2 |

Авторы

Даты

1973-01-01—Публикация