(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Параллельный накапливающий сумматор | 1988 |

|

SU1578710A2 |

| Параллельный накапливающий сумматор | 1986 |

|

SU1399726A1 |

| Сумматор последовательного действия | 1989 |

|

SU1689945A2 |

| Последовательный сумматор | 1987 |

|

SU1411734A1 |

| Последовательный сумматор | 1989 |

|

SU1709298A2 |

| Преобразователь кодов | 1988 |

|

SU1501279A1 |

| Устройство для умножения по модулю 2 @ -1 @ | 1985 |

|

SU1304018A1 |

| Преобразователь напряжение-код | 1988 |

|

SU1508343A1 |

| Устройство для умножения | 1988 |

|

SU1571574A1 |

Изобретение относится к вычислительной технике и может использоваться для построения устройств арифметической и логической обработки двоичных чисел и чисел с иррациональным основанием, а также в устройствах обработки графической информации. Цель изобретения - расширение функциональных возможностей за счет выполнения операций в кодах с иррациональным основанием √2. Арифметико-логическое устройство содержит в каждом разряде мультиплексоры 1 - 3, элемент И 4, элементы ИЛИ 5 и 6 и триггер 7 с соответствующими связями. 1 ил. 5 табл.

;о ел

м

00

to

Изобретение относится к вычислительной технике и может использоваться для построения устройств арифметической и логической обработки дво- ичных чисел и чисел с иррациональным основанием v2, а также в устройства обработки графической информации.

Цеотью изобретения является расширение функциональных возможностей за счет выполнения операций в кодах с иррациональным основанием.

На чертеже представлена схема арифметико-логического устройства (для трех разрядов).

Устройство содержит в каждом i-м разряде с первого по третий мульти

плексоры

1,--.

соответственно, эле

Мент И , первый и второй элемент ИЛИ 5,6 соответственно, триггер 7., вход 8 задания вида операции устройства, вход 9 начальной установки устройства, информационные входы 10j первого мультиплексора l , информационные входы 11. второго мультиплек- сора 2 J, информационный вход 12 устройства, стробирующий вход 13 , мультиплексоров lj,2., выход 14 результата устройства, выход 15, переноса разряда устройства, первый и второй информационные входы 16- и 17j третьего мультиплексора 3, соответственно, стробирующий вход 18. третьего мультиплексора 3, управляющий вход 19 третьего мультиплексора 3;, вход 20 задания режима работы устройства,- вход 21 разрешения работы устройства В системе счисления с основанием /2 числа D и Е изображаются следующий образом

., (1)- -+d, (V2)4d/V2);(l )

,(V2) ++e,(V2)+eo(T) .(2)

Веса разрядов кода с основанием 12

составляют последовательность

.....4V2, 4,.2 V2, 2, V2, 1. (3) Из выражения (3) следует, что четные степени являются весами разрядов gg двоичного кода, а нечетные - весами двоичного кода, умноженными на V2. С учетом этого числа (1) и (2) можно

n-i

d,-2 (-0

(4)

- n-г

I. - f T-e;2%

-« 1 0

(5)

г

10

15

20

, 2535- .

l )

2)

ggо

4957824

где d . ,d ,p. .,, и являются цифрами двоично-кодированной системы счисления с основанием -/2, а i,j для п-разрядных чисел принимают значения

j ,3,5,...п-13, ,2,4,6,... . .. .п-2 }.

Первые члены формул (4) и (5) составляют суммы нечетных разрядов кода, а вторые члены - суммь четных разрядов кода с основанием т2. Несмотря на то, что члены выражений (4) ,и (5) объединены общим основанием, они независимы друг от друга, а это позволяет осуществить одновременную независимую параллельную реализацию операции сложения четных и нечетных разрядов операндов, представленных в кодах с основанием ,

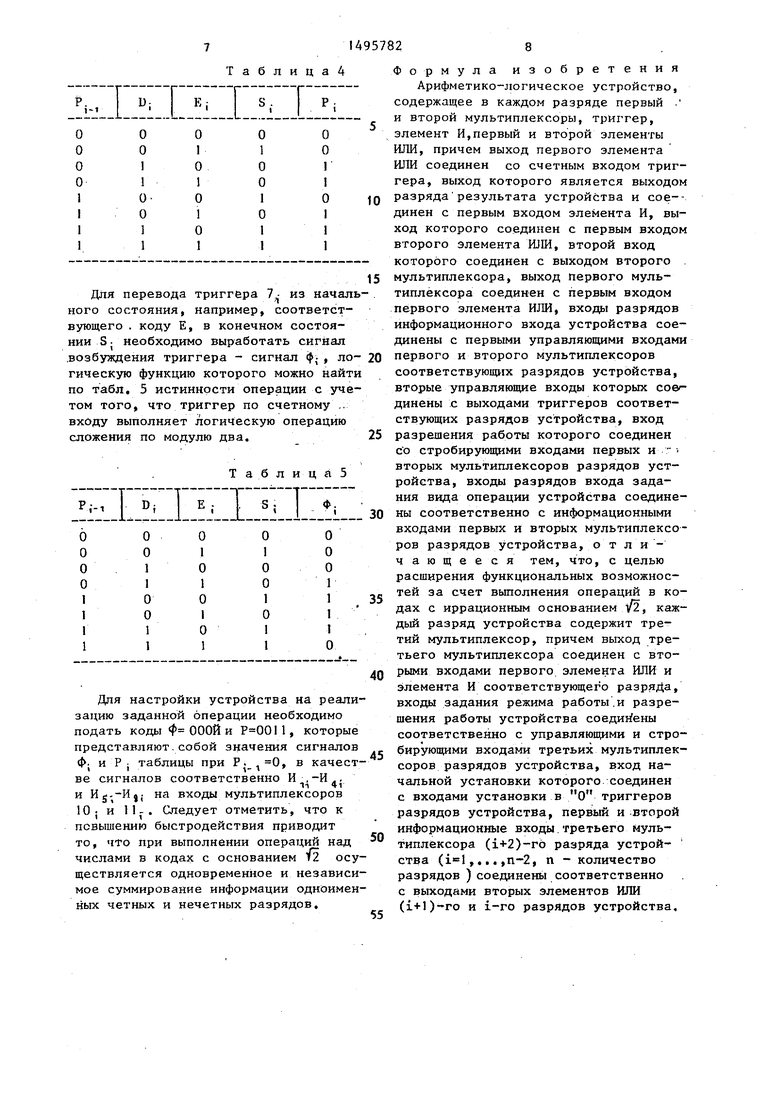

Сложение двух одноименных разрядов в двоичной системе .счисления с иррациональным основанием V2 вы- полняется согласно табл.1.

Таблица 1

0+ 0 0 0+1 1

1+ 1 100

Если в i-x разрядах (четных или од нечетных) слагаемых имеются единицы, то как это следует из табл.1, единица переноса поступит в (1+2)-й раз,- ряд кода, в отличие от традиционной двоичной системы счисления, где единица поступает в (1+)-й разряд.

По сигналам на входе 8 реализуются различные логические функции переменных D и Е, благодаря которым возможно выполнение 256 различных математических операций.

Арифметико-логическое устройство может работать в двух режимах: в режиме выполнения математических,операций над операндами, представленными в коде с основанием V2; в. режиме выполнения математических операций при двоичном представлении операндов.

Первый режим обеспечивается подачей единичного сигнала на вход 20, второй - подачей нулевого сигнала на вход 20 устройства.

Рассмотрим работу устройства в режиме сложения чисел в коде с иррациональным основанием на примере i-ro разряда.

Перед началом выполнения любой ма40

55

тематической операции на вход 22 подается команда Сброс, которая устанавливает триггер 7, в состояние О.

В триггер 7- заносится i-й разряд кода одного из двух чисел D и Е, участвующих в операции, например числа D, для чего этот разряд подается на информационный вход 12 i. На вход 20 по ступает единичный сигнал. Мультиплексор 1J настраивае тся с помощью сигналов с входа 8 , подаваемых на группу входов 10, на реализацию логической функции возбуждения триггера DqvqD -сигнал с триггера 1, . Под действием импульсного сигнала, поступившего в вход 21, подается на вход 13; Сигнал разрешения выполнени операции, на выходе мультиплексора 1 вырабатывается сигнал возбуждения триггера 7; .и происходит запись в триггер 7,- i-ro разряда кода числа D через первый элемент ИЛИ 5-, После записи в триггер 7. разряда нечетных весов кода числа D на информационный вход 12 { поступает i-й разряд кода второго числа Е. Сигнал переноса Р« - поступает из (-2)-го разряда на вторые входы первого злемента ИЛИ 5. и элемента И 4 , через мультиплексор 3«, Настройка на выполнение требуемой математической операции осуществляется с помощью сигналов И.-И. . с входа 8. Причем, если реализуемая операция является только логической, то сигналы H,j,-H.., поступающие на мультиплексор 2,- равны нулю. В этом случае выходной сигнал переноса Р. не формируется. Для выполнения произвольной математической операции из набора реализуемых код настройки устройства- находится по табл.2 истин- ности этой операции.

Табл.2 истинности операции имеет вид.

Для перевода триггера 7,. из состояния начального, соответствующего коду Е, в состояттие конечное S- необходимо выработать си1 нал возбуждения

триггера - сигнал (., логическая функция которого находится по табл.3 истинности операции с учетом того, что триггер по счетному входу реализует операцию сложения по модулю два.

Т а б л и ц а 3

Q g 2п 25

30

35

0

5

0

6

Для настройки устройство на выполнение операции необходимо подать коды и , которые являются значениями сигналов и Р табл,3 при Р i., в качестве сигналов управления соответственно И,-И.

11 Т1

и Hsi-Hji на входы 10,. и И мультиплексоров 1 ; и 2 ;,

После подачи на вход 13 разрешения выполнения операции импульсного сигнала мультиплексором 2 , вырабатывается сигнал переноса Р | , который поступает на вход третьего мульти г

плексора 3 , (i+2)-ro разряда сумматора, а мультиплексором j вырабатывается сигнал возбуждения триггера.

Отличительной особенностью выполнения математических операций в данном режиме является то, что перенос Р, расп)остраняется в (1+2)-й разряд сумматора, а поразрядные операции над D и Е выполняются в четных и нечетных разрядах одновременно и независимо друг от друга,

При выполнении математических операций с двоичным представлением операндов перенос единиц из i-ro разряда происходит в разряд i+1, т.е. в слева стоящий. Дпя обеспечения вы- полнения операций на вход 20 поступает нулевой сигнал, который включает в работу первый вход мультиплексора 3,

В остальном проце сс выполнения операций во втором режиме ничем не отличается от ранее рассмотренного.

Рассмотрим пример выполнения операции (EVU), т.зблица истинное-- ти которой имеет шщ (с:м. табл.4).

Таблица4

....L.:

Для перевода триггера из началь ного состояния, например, соответствующего . коду Е, в конечном состоянии S- необход11мо выработать сигнал .возбуждения триггера - сигнал ф , ло- гическую функцию которого можно найти по табл. 5 истинности операции с учетом того, что триггер по счетному .. входу выполняет логическую операцию сложения по модулю два.

Т а б л и ц а 5

.

Для настройки устройства на реализацию заданной операции необходимо подать коды ф ОООЙ и , которые представляют.собой значения сигналов ф; и PJ таблицы при Р.,0, в качестве сигналов соответственно И ,-И..

1л 4i и Hg--Iij. на входы мультиплексоров

10- и 11-. Следует отметить, что к повышению быстродействия приводит то, что при выполнении операций над числами в кодах с основанием 12 осуществляется одновременное и независимое суммирование информации одноименных четных и нечетных разрядов.

. 0 5

0

5

0

5

0

5

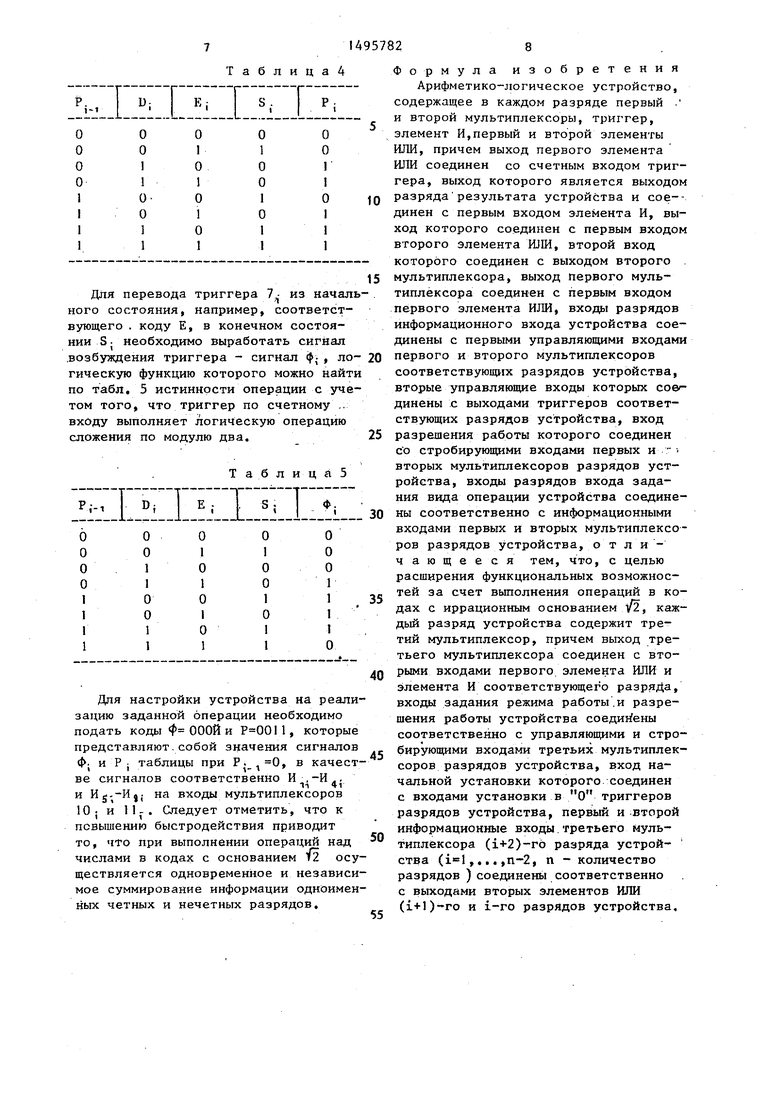

Формула изобретения Арифметико-логическое устройство, содержащее в каждом разряде первый . и второй мультиплексоры, триггер, элемент И,первый и второй элементы ИЛИ, причем выход первого элемента ИЛИ соединен со счетным входом триггера, выход которого является выходом разряда результата устройства и сое-- динен с первым входом элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом второго мультиплексора, выход первого мультиплексора соединен с первым входом первого элемента ИЛИ, входы разрядов информационного входа устройства соединены с первыми управляющими входами первого и второго мультиплексоров соответствующих разрядов устройства, вторые управляющие входы которых со&- динеиы с выходами триггеров соответствующих разрядов устройства, вход разрешения работы которого соединен со стробирующими входами первых и - вторых мультиплексоров разрядов устройства, входы разрядов входа задания вида операции устройства соединены соответственно с информационными входами первых и вторых мультиплексоров разрядов устройства, о т л и - чающееся тем, что, с целью расширения функциональных возможностей за счет выполнения операций в кодах с иррационным основанием 2, каждый разряд устройства содержит третий мультиплексор, причем выход третьего мультиплексора соединен с вторыми входами первого элемента ИЛИ и элемента И соответствующего разряда, входы задания режима работы.и разрешения работы устройства соединены соответственно с управляющими и стробирующими входами третьих мультиплексоров разрядов устройства, вход начальной установки которого соединен с входами установки в о триггеров разрядов устройства, первый и второй информационные входы третьего мультиплексора (i+2)-rO разряда устрой- ства (,...,п-2, п -количество разрядов ) соединены соответственно с выходами вторых элементов ИЛИ (i+l)-ro и i-ro разрядов устройства.

| Управляемый арифметический модуль | 1985 |

|

SU1309017A1 |

| Накапливающий сумматор | 1979 |

|

SU920708A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| Способ получения на волокне оливково-зеленой окраски путем образования никелевого лака азокрасителя | 1920 |

|

SU57A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-07-23—Публикация

1987-12-17—Подача