Изобретение относится к вычислительной технике и может быть использовано в процессорах вы,числительных машин с повышенной достоверностью обработки информации. 3 также при создании специализированных векторных вычислительных машин.

Цель изобретения - повышение достоверности суммирования за счет обеспечения контроля входных и выходных кодов с иррациональным основанием К2 и двоичных кодов.

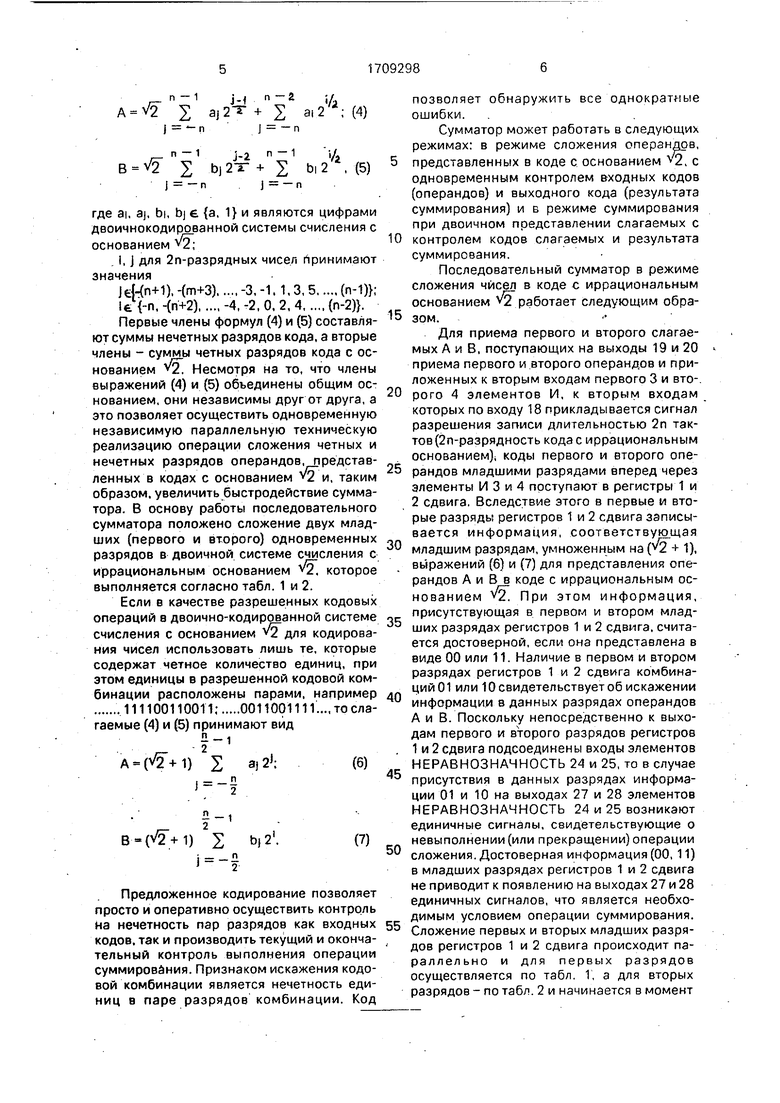

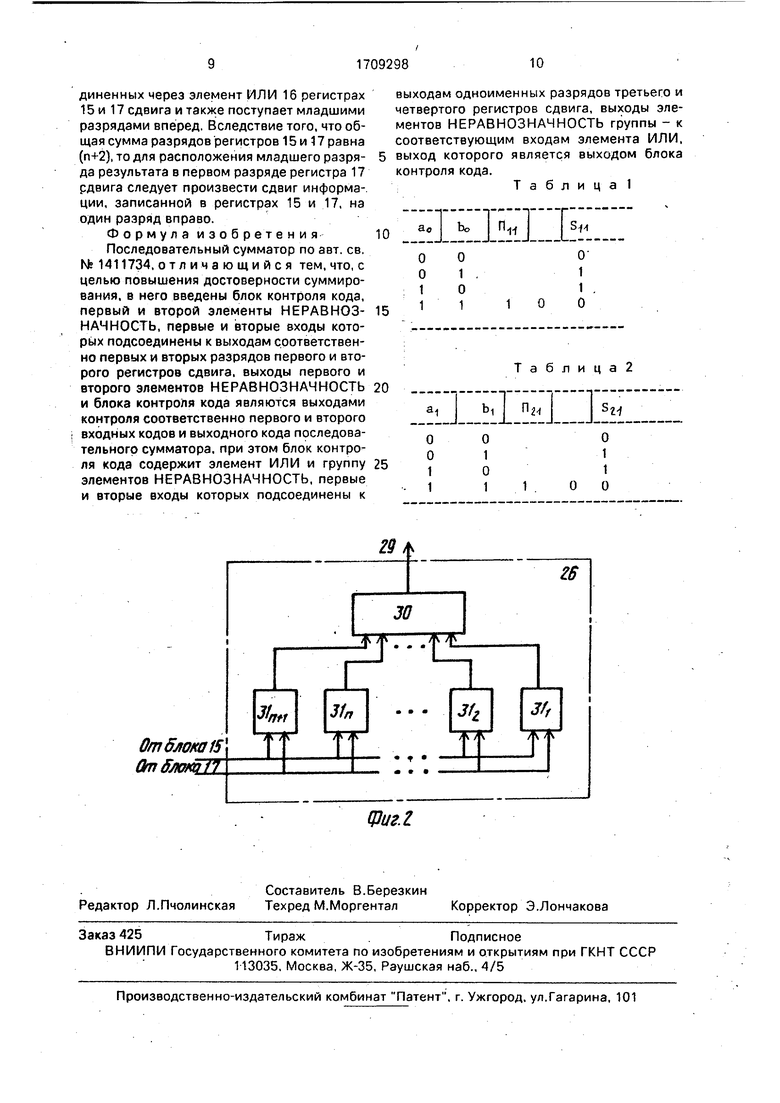

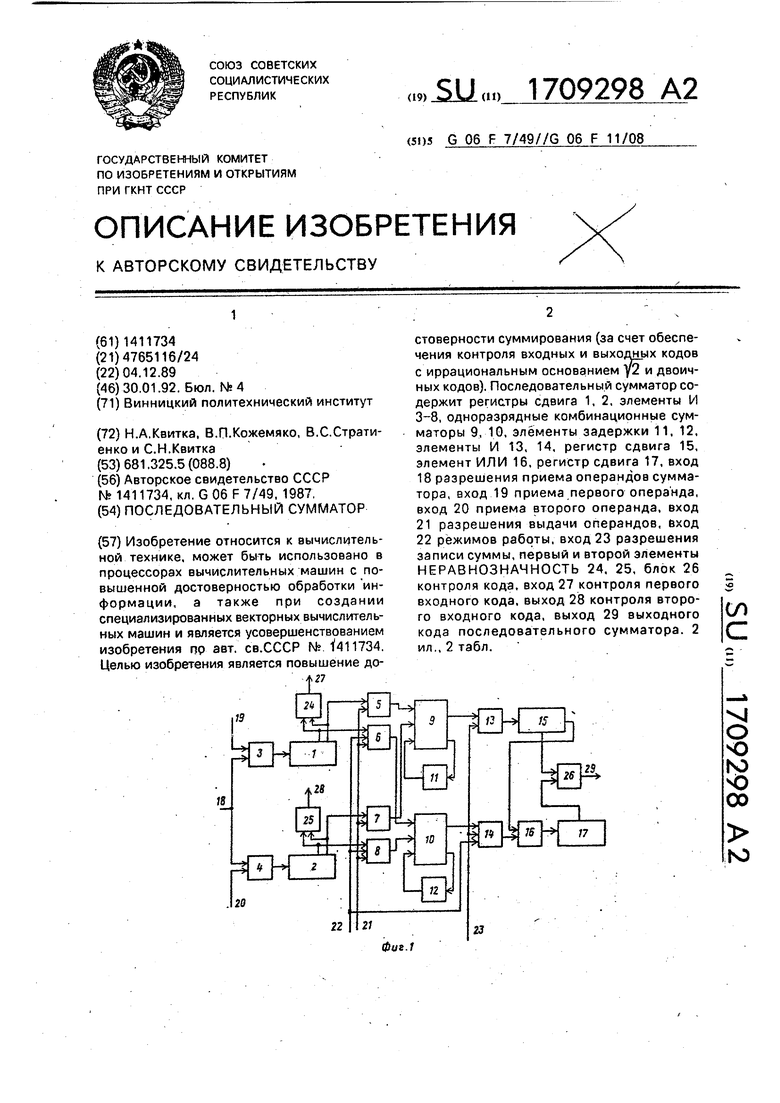

На фиг, 1 изображена структурная схема последовательного сумматора; на фиг, 2 функциональная схема блока контроля кода.

Последовательный сумматор содержит регистры 1 и 2 сдвига, элементы И 3-8, одноразрядные комбинационные суматоры 9 и 10,элементы 11 и 12 задержки, элементы И 13 и 14, регистр 15 сдвига, элемент ИЛИ 16, регистр 17 сдвига, вход 18 разрешения приема операндов сумматора, вход 19 при.ема первого операнда, вход 20 приема второго операнда, вход 21 разрешения выдачи операндов, вход 22 режимов работы, вход 23 разрешения записи суммы, первый 24 и второй 25 элементы НЕРАВНОЗНАЧНОСТЬ, блок 26 контроля кода, выход 27 контроля первого входного кода, выход 28 контроля второго входного кода и выхбд 29 выходного последовательного сумматора.

Блок 26 контроля кода содержит многовходовый элемент ИЛИ 30 и (п+1) элементов НЕРАВНОЗНАЧНОСТЬ 311..... 31п-и.

Входы первого 1 и второго 2 регистров сдвига соединены с выходами первого 3 и второго 4 элементов И, первые входы которых объединены м подсоединены к входу 18 разрешения приема операндов сумматора, а их вторые входы соединены соответственно с входами 19 и 20 приема первого и второго операндов. К первым выходам регистров 1 и 2 сдвига подключены первые входы третьего 5 и четвертого 7 элементов И, вторые входы которых соединены с входом 21 разрешения выдачи операндов. Вторые выходы регистров 1 и 2 сдвига соединены с первыми входами элементов И 6 и 8, их вторые входы связаны с входом 2 разрешения выдачи операндов, а третьи - подсоединены к входу 22 режимов работы. Выходы элементов И 5-8 подключены к первым и вторым входам соответственно первого 9 и второго 10 одноразрядных сумматоров, а их третьи входы через элементы 11 и 12 задержки подсоединены к вторым входам одноразрядных сумматоров 9 и 10, первые

выходы которых соединены с первыми входами элементов И 13 и 14, вторые входы которых связаны с входом 23 разрешения записи суммы. Третий вход элемента И 14

подсоединен к входу 22 режимов работы. Выход элемента И 13 соединен с входом регистра 15 сдвига, выход которого совместно с выходом элемента И 14 подсоединены через элемент ИЛИ 16 к входу регистра

17 сдвига. Первые и вторые входы элементов НЕРАВНОЗНАЧНОСТЬ 24 и25соединеHU с первыми и вторыми выходами регистров 1 и 2 сдвига, а выходы третьего 15 и четвертого 17 регистров подсоединены к

первому и второму входам блока 26 контроля кода, к которым подсоединены первые и вторые входы (n+l) элементов НЕРАВНОЗНАЧНОСТЬ 31131п+1, к выходам которых

подключен многовходовой элемент ИЛИ 30,

Регистры 1 и 2 сдвига являются 2п-разрядными и предназначены для записи и хранения операндов, поступающих из запоминающего устройства поочередно на входы 19 и 20 младшими разрядами вперед.

Разрядность регистров 15 и 17 сдвига равна (nf 1), причем в случае суммирования чисел кода с основанием /2 регистр 15 сдвига применяется для хранения четных разрядов суммы в коде 2, а регистр 17 - для хранеимя нечетных разрядов суммы, В режиме сложения двоичных 2п-разрядных кодов результат суммирования хранится в последовательно включенных регистрах 15 и 17 сдвига, общая разрядность которых равна

2г, + 2,

В системе счисления с иррациональным основанием 2 в общем случае сдвигаемые числа А и В изображаются следующим образом:

+ ап-7(г-1+... +

+ ai(y2lUao()° + aj(v2)

+ a-2(y2f + ... + 3-n(W:(1)

В b,JfV2Г- + Ьп-2(Г - .,. +

+ Ь1(У2} + Ьо()° + b-i(r +

+ b-2(V2)- + ,,, + Ь-п(Г ,(2)

Веса разрядов кода с основанием 2 составляют последовательность степеней основания

,., 16 4 , 4: 2 2, 2 v,

1 : 1 : 1 1,0-,

22- 4 4 В 8Из выражения (3) следует, что четные

степени являются весами разрядов двоичного кода, а нечетные - весами двоичного кода, умноженными на 2. С учетом этого выражения (1) и (2) можно записать A V2 2 aj2-5- + 2 312 ; (4) j -П j -n n -1j.2 n -1 B v X b)2T-+ 2 b|2 (5) j -n. где ai, aj, bi, bj e {a. 1} и являются цифрами двоичнокодированной системы счисления с основанием 2; . I, J для 2п-разрядных чисел принимают значения Je{-(n+1).-()-3.-1.1,3,5(п-1)}; 1е {-п. -(п+2)-4, -2. 0. 2, 4(п-2)}. Первые члены формул (4) и (5) составляют суммы нечетных разрядов кода, а вторые члены - суммы четных разрядов кода с основанием v2. Несмотря на то, что члены выражений (4) и (5) объединены общим основанием, они независимы друг от друга, а это позволяет осуществить одновременную независимую параллельную техническую реализацию операции сложения четных и нечетных разрядов операндов, представленных в кодах с основанием 2 и, таким образом, увеличить быстродействие сумматора. В основу работы последовательного сумматора положено сложение двух младших (первого и второго) одновременных разрядов в двоичной системе счисления с иррациональным основанием . которое выполняется согласно табл. 1 и 2. Если в качестве разрешенных кодовых операций в двоично-кодированной системе счисления с основанием 2 для кодирования чисел использовать лишь те, которые содержат четное количество единиц, при этом единицы в разрешенной кодовой комбинации расположены парами, например 111100110011:0011001111.„, то слагаемые (4) и (5) принимают вид А (-И) S ) 2 Ь)2 Предложенное кодирование позволяет просто и оперативно осуществить контроль на нечетность пар разрядов как входных кодов, так и производить текущий и окончательный контроль выполнения операции суммирования. Признаком искажения кодовой комбинации является нечетность единиц в паре разрядов комбинации. Код позволяет обнаружить все однократные ошибки. Сумматор может работать в следующих режимах: в режиме сложения операндов, представленных в коде с основанием 2, с одновременным контролем входных кодов (операндов) и выходного кода (результата суммирования) и в режиме суммирования при двоичном представлении слагаемых с контролем кодов слагаемых и результата суммирования. Последовательный сумматор в режиме сложения чисел в коде с иррациональным основанием 2 работает следующим образом. Для приема первого и второго слагаемых А и В, поступающих на выходы 19 и 20 приема первого и второго операндов и приложенных к вторым входам первого 3 и вто-. рого 4 элементов И, к вторым входам которых по входу 18 прикладывается сигнал разрешения записи длительностью 2п тактов (2п-разрядность кода с иррациональным основанием); коды первого и второго операндов младшими разрядами вперед через элементы И 3 и 4 прступают в регистры 1 и 2 сдвига. Вследствие этого в первые и вторые разряды регистров 1 и 2 сдвига записывается информация, соответствующая младшим разрядам, умноженным на (2 + 1), выражений (6) и (7) для представления операндов А и В в коде с иррациональным основанием v2. При этом информация, присутствующая в первом и втором младших разрядах регистров 1 и 2 сдвига, считается достоверной, если она представлена в виде 00 или 11. Наличие в первом и втором разрядах регистров 1 и 2 сдвига комбинаций 01 или 10 свидетельствует об искажении информации в данных разрядах операндов А и В. Поскольку непосредственно к выходам первого и второго разрядов регистров 1 и 2 сдвига подсоединены входы элементов НЕРАВНОЗНАЧНОСТЬ 24 и 25, то в случае присутствия в данных разрядах информации 01 и 10 на выходах 27 и 28 элементов НЕРАВНОЗНАЧНОСТЬ 24 и 25 возникают единичные сигналы, сеидетельствующие о невыполнении (или прекращении) операции сложения. Достоверная информация (00, 11) в младших разрядах регистров 1 и 2 сдвига не приводит к появлению на выходах 27 и 28 единичных сигналов, что является необходимым условием операции суммирования. Сложение первых и вторых младших разрядов регистров 1 и 2 сдвига происходит параллельно и для первых разрядов осуществляется по табл. 1, а для вторых разрядов - по табл. 2 и начинается в момент

появления сигналов на входах 21 и 22. вследствие чего информация первых и вторых разрядов операндов А и В, пройдя через элементы И 5 и 7, а также элементы И б и 8. поступает на первый и второй входы однорвзрядных сумматоров 9 и 10. Если на первом и втором входах сумматоров 9 и 10 присутствуют О, 1 или 1, О, на первых выходах (суммы) сумматоров появляются единичные сигналы, которые при наличии разрешающего сигнала на входе 23 проходят через элементы И 13,14 и записываются 8 регистры 15 и 17 сдвига для хранения результата суммирования. На вторых выходах переноса сумматоров 9 и 10 при этом имеются нулевые сигналы. Если на первом и втором входах сумматоров 9 и 10 имеется 1, 1. то на вторых выходах переноса появляются единичные сигналы, которые задерживаются элементами 11 и 12 задержки на время поступления в первый и второй р1Э30яды регистров 1 и 2 сдвига информации третьего и четвертого разрядов операндов А и В, Смена содержимого первого и второго разрядов регистров 1 и 2 сдвига осуществляется путем сдвига на два разряда вправо операндов А и В вследствие приложения тактовых импульсов. При втором такте суммированияосуществляется сложение одновременных (третьего и четвертого) разрядов А и В.информация о которых поступает на первый и второй входы одноразрядных сумматоров 9 и 10 при наличии сигналов на входах 21 и 22 соответственно выдачи операндов и режимов работы. Однако в отличие от первого такта в данном случае на третьих входах сумматоров 9 и 10 могут присутствовать единичные сигналы переноса, в этом случае присутствие единичных сигналов на трех входах сумматоров 9 и 10 вызывает появление единичных сигналов как на первых выходах (суммы), так и на вторых выходах(переноса). При этом выходные сигналы первых выходов как вторые разряды результатов суммы четных и нечетных разрядов записываются в регистры 15 и 17 сдвига при наличии разрешающего сигнала на входе 23, а сигналы переноса задерживаются элементами 11 и 12 задержки и принимают участие в работе одноразрядных сумматоров 9 и 10 в третьем такте суммирования, когда в первом и втором разрядах регистров 1 и 2 сдвига находится информация о пятом и шестом разрядах операндов А и В. Процесс суммирования в последующих тактах аналогичен рассмотренному. Исключение составляет последний такт, в котором единичный сигнал присутствует только на третьем входе сумматоров 9 и 10. обусловленный сигналом переноса. В процессе потактиого сложения операндов А и В систематически осуществляется контроль входного кода с помощью элементов НЕРАВНОЗНАЧНОСТЬ 24 и 25 и, наряду с

этим потактно выполняется контроль правильной работы сумматоров 9 и 10. Если сумматоры 9 и 10 работают без сбоев, то при любом такте на выходах сумматоров 9 и 10 всегда должны присутствовать сигналы 11

или 00. в то время как появление сигналов

01или 10 свидетельствует о нарушении работы сумматоров. Поскольку текущие значения суммы последовательно поразрядно записываются в регистры 15 и 17 сдвига, к

выходам одноименных разрядов которых подсоединены соответствующие входы элементов НЕРАВНОЗНАЧНОСТЬ 31131п-и

блока 26 контроля кода, то при появлении в одноименных разрядах кодов 01 или 10 на

выходе 29 появляется единичный сигнал. Дальнейшее суммирование при этом прекращается. Для сложения двух 2п-разрядных кодов (п - четное) с иррациональным основанием 2 необходимо произвести п

сдвигов чисел А и В и выполнить.(п+1) тактов суммирования, а также осуществить п контролей входных кодов и (п+1) контроль выходного кода результата суммирования. В режиме суммирования при двоичном представлении п-разрядных операндов А и В с контролем кодов слагаемых и результата суммирования необходимо до ввода п-разрядных операндов в регистры 1 и 2 сдвига единицу кода операндов А и В представить

в, виде 11.3 нуль - 00. затем полученные 2п-разрядные слагаемые нужно записать младшими разрядами вперед в регистры 1 и

2сдвига и осуществить операцию сложения одновременным контролем входных и выходных кодов аналогично ранее рассмотренному случаю. Окончательно полученные (п+1)-разрядные коды в регистрах 15 и 17 сдвига должны полностью совпадать, а единичный сигнал на выходе 29 последовательного сумматора отсутствовать. В противном случае результат суммирования является недостоверным. При сложении п-разрядных операндов А и В, представленных двоичным кодом без контроля кодов, в работе участвуют элементы И 3, 4. 5. 7 и 13, регистры 1.2. 15 и 17 сдвига, одноразрядный сумматор 9. элементы задержки 11 и ИЛИ 16. В данном режиме сигнал на входе 22 отсутствует. Суммирование осуществляется, как и в ранее

рассмотренном случае, по тактам.

Операнды А и В записываются последовательно младшими разрядами вперед в регистры 1 и 2 сдвига, а результат сложения чисел фиксируется в последовательно соединенных через элемент ИЛИ 16 регистрах 15 и 17 сдвига и также поступает младшими разрядами вперед. Вследствие того, что общая сумма разрядов регистров 15 и 17 равна (п+2), то для расположения младшего разряда результата в первом разряде регистра 17 рдвига следует произвести сдвиг информации, записанной в регистрах 15 и 17, на один разряд вправо.

Формула изобретения Последовательный сумматор по авт. св. Мг 1411734, о т л им а ю щи и с я тем, что, с целью повышения достоверности суммирования, в него введены блок контроля кода, первый и второй элементы НЕРАВНОЗНАЧНОСТЬ, первые и вторые входы которых подсоединены к выходам соответственно первых и вторых разрядов первого и второго регистров сдвига, выходы первого и второго элементов НЕРАВНОЗНАЧНОСТЬ и блока контроля кода являются выходами контроля соответственно первого и второго входных кодов и выходного кода последовательного сумматора, при этом блок контроля кода содержит элемент ИЛИ и группу элементов НЕРАВНОЗНАЧНОСТЬ, первые и вторые входы которых подсоединены к

выходам одноименных разрядов третьего и четвертого регистров сдвига, выходы элементов НЕРАВНОЗНАЧНОСТЬ группы - к соответствующим входам элемента ИЛИ, выход которого является выходом блока контроля кода.

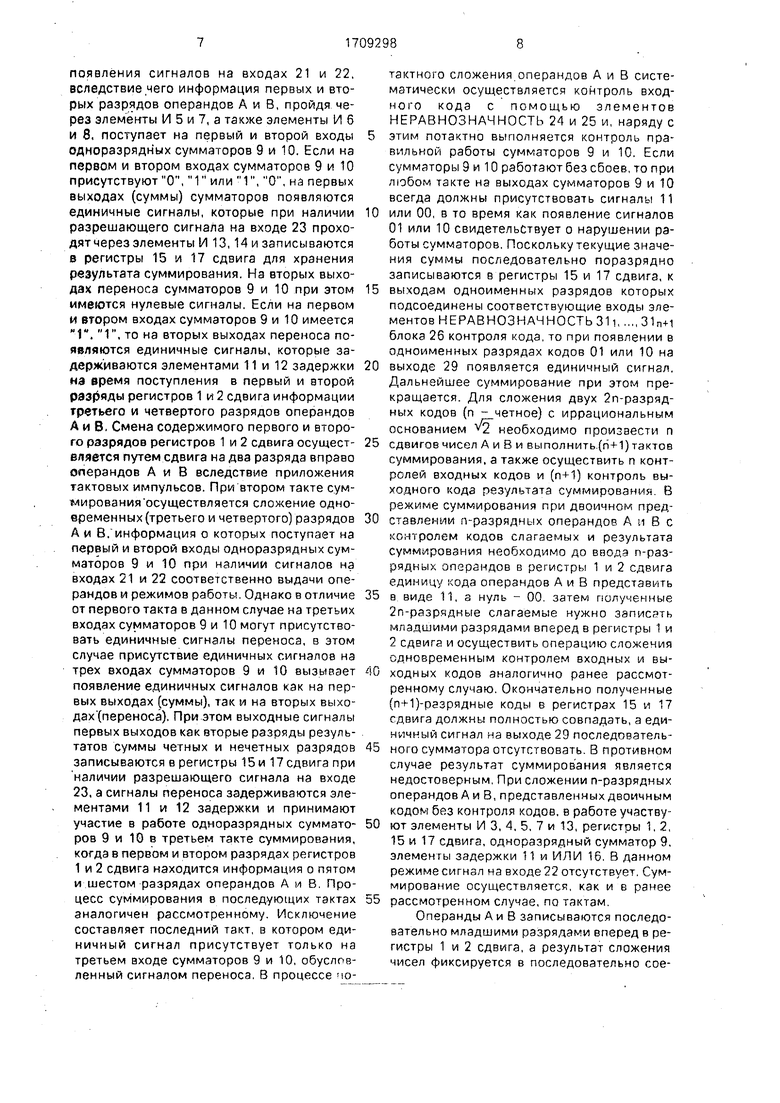

Т а б л и ц а 1

be П,, s,

Эо

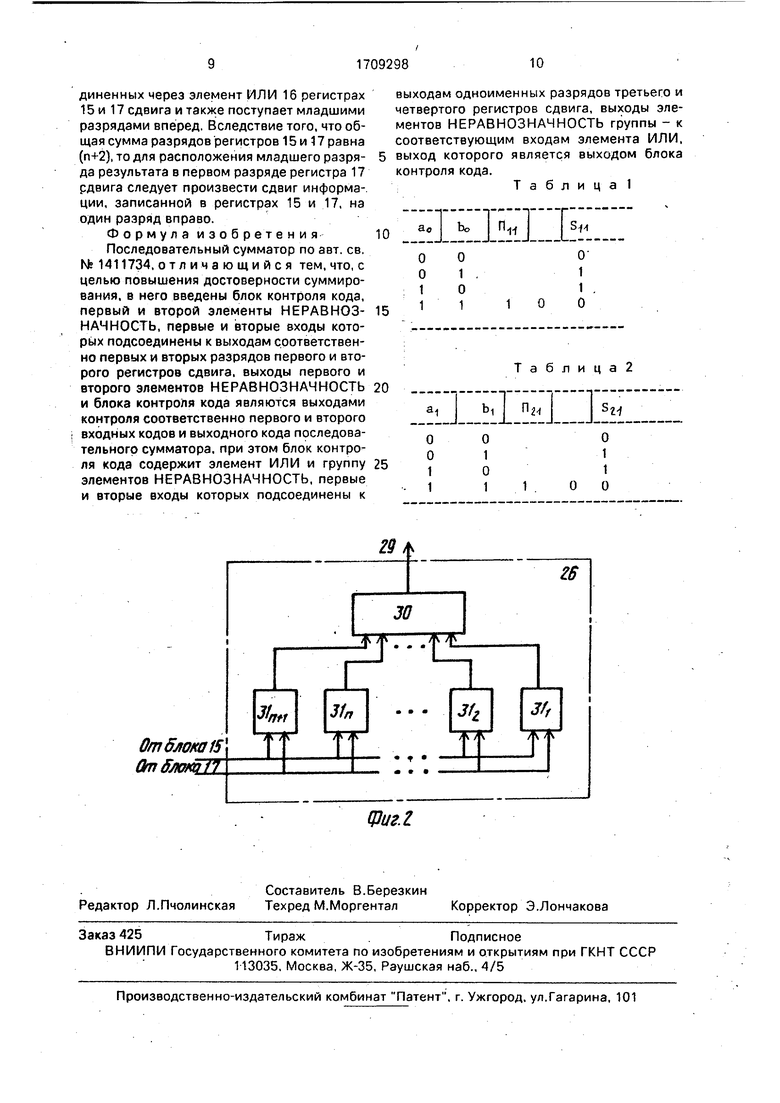

Таблица2

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательный сумматор | 1987 |

|

SU1411734A1 |

| Параллельный накапливающий сумматор | 1988 |

|

SU1578710A2 |

| Параллельный накапливающий сумматор | 1988 |

|

SU1564614A1 |

| Сумматор последовательного действия | 1989 |

|

SU1689945A2 |

| Устройство для суммирования двоичных чисел | 1988 |

|

SU1578709A2 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Параллельный накапливающий сумматор | 1986 |

|

SU1399726A1 |

| Счетное устройство с иррациональным основанием @ 2 | 1989 |

|

SU1677868A1 |

| Сумматор п-разрядных комплексныхчиСЕл | 1979 |

|

SU817699A1 |

| Преобразователь кодов | 1988 |

|

SU1529458A1 |

Изобретение относится к вычислительной технике, может быть использовано в процессорах вычислительных машин с повышенной достоверностью обработки 'информации, а также при создании специализированных векторных вычислительных машин и является усовершенствованием изобретения пр зет. св.СССР № ^411734. Целью изобретения является повышение до-*г7стоверности суммирования (за счет обеспечения контроля входных и выход

| Последовательный сумматор | 1987 |

|

SU1411734A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-01-30—Публикация

1989-12-04—Подача