1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при реализации технических средств дискретной автоматики и цифровых вычислительных машин.

Известны устройства для вычисления функции вида

z K + У,

содержащие два регистра, связанные входами с шинами переменных, а выходами через две группы схем «И, другие входы которых связаны с выходами двух схем задержки, со входами третьего .регистра, причем вход первой схемы задержки связан с первой шиной приращений, а вход второй схемы задержки через третью схему «И, другой вход которой подключен к выходу третьего регистра, - со второй шиной приращений, схему сравнения, логические схемы..

Недостатками в известных устройствах является отсутствие контроля результатов вычислений и, следовательно, недостаточная надежность работы, а также наличие многоразрядного сумматора, в котором хранится величина (), или наличие выходного регистра.

Предлагаемое устройство, с целью упрощения и повышения надежности его работы, содержит четвертый регистр, выходы первого и

второго регистров связаны со входами схемы сравнения, выход которой связан со входами четвертой грунны схем «И, другими входами связанных с выходами второго регистра, а выходами- с выходными шинами устройства; другие выходы обеих схем задержки связаны со входами третьего регистра; входы четвертого регистра связаны с двумя шинами переменных, первой шиной приращений и выходом третьей схемы «И.

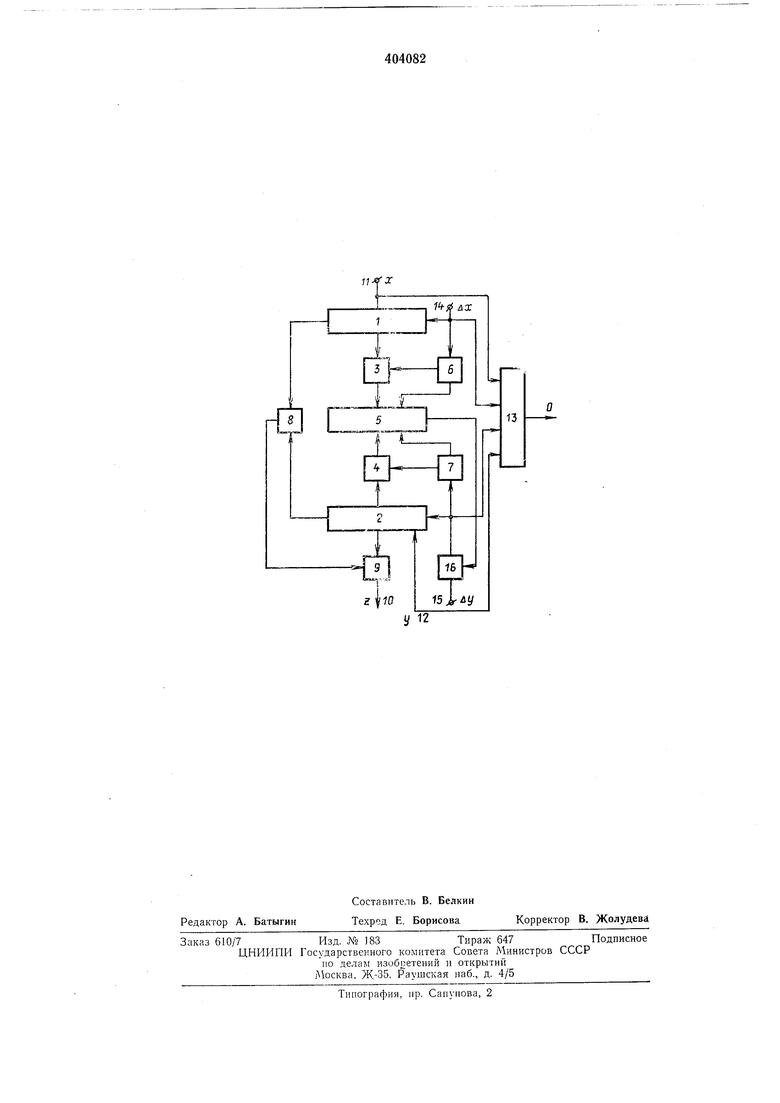

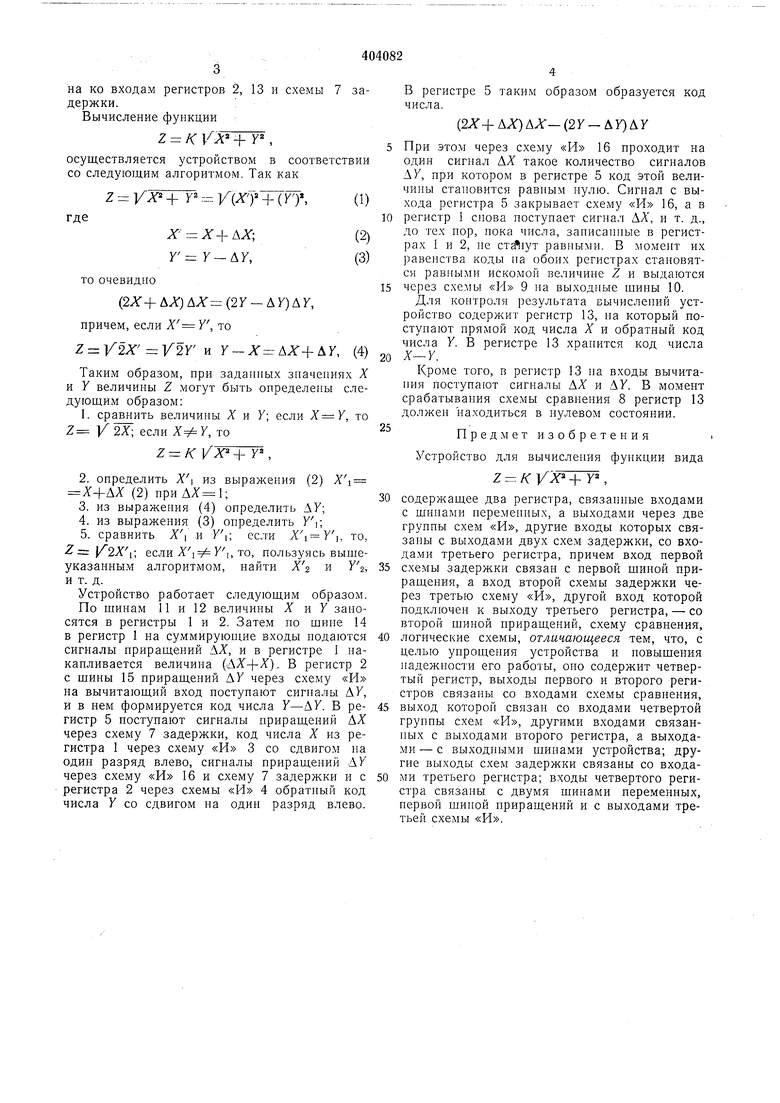

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит регистры 1 и 2, выходы которых через схемы «И 3 и 4 связаны со входами регистра 5. Два других входа регистра 5 связаны с выходами схем 6 и 7 задержки, а другие входы схем «И 3 и 4 - с другими выходами схем 6 и 7 задержки соответственно. Другие выходы регистров 1 и 2 через схему 8 совнадения связаны с одним из входов схемы «И 9, другие входы которой нодключены к выходам регистра 2, а выходы- к выходным шинам 10. Шины 11 и 12

неременных А и У связаны со входами регистров 1, 2 и регистра 13. Шина 14 приращений &.Х подключена ко входам регистров 1 и 13 и схемы 6 задержки. Шина 15 приращений ДУ через схему «И 6, другим выходом

связанную с выходом регистра 5, подключена ко входам регистров 2, 13 и схемы 7 задержки. Вычисление функции

Z - /С 1/А -f Г ,

осуществляется устройством в соответствии со следующим алгоритмом. Так как

Z УХ + У . Y(XJ +().(1)

где

.(2)

,(3)

то очевидно(2ЛГ+ Л) Д (27 - Д У) Д У, причем, если X Y, то

Z и У- Д;Г+АУ, (4)

Таким образом, нри заданных значениях X и У величины Z могут быть определены следующим образом:

1.сравнить величины X vi Y; если , то

если Х У, то

Z /С |/Ж+Т ,

2.определить ySfi из выражения (2) Х

(2) при

3.из выражения (4) определить А У;

4.из выражения (3) определить

5.сравнить Jl и Уь , то, Z: :y2Xi если yl, то, пользуясь вышеуказанным алгоритмом, найти Х и У2, и т. д.

Устройство работает следующим образом.

По шинам 11 и 12 величины J и У заносятся в регистры 1 и 2. Затем по шине 14 в регистр 1 на суммируюище входы нодаются сигналы приращений Д.Х , и в регистре 1 накапливается величина (. В регистр 2 с шины 15 приращений ДУ через схему «И на вычитающий вход поступают сигналы ДУ, и в нем формируется код числа У-ДУ. В регистр 5 поступают сигналы приращений ДХ через схему 7 задержки, код числа X из регистра 1 через схему «И 3 со сдвигом на один разряд влево, сигналы приращений ДУ через схему «И 16 и схему 7 задержки и с регистра 2 через схемы «И 4 обратный код числа У со сдвигом на один разряд влево.

В регистре 5 таким образом образуется код числа.

() (2У - ДУ) ДУ

При этом через схему «И 16 проходит на один сигнал ДХ такое количество сигналов ДУ, при котором в регистре 5 код этой величины становится равным нулю. Сигнал с выхода регистра 5 закрывает схему «И 16, а в регистр I снова ностунает сигнал ДА , и т. д., до тех нор, пока числа, записанные в регистрах 1 и 2, не равными. В момент их равенства коды на обоих регистрах становятся равными искомой величине Z и выдаются через схемы «И 9 на выходные шины 10.

Для контроля результата вычислений устройство содержит регистр 13, на который поступают прямой код числа X и обратный код числа У. В регистре 13 хранится код числа /Y-У.

Кроме того, в регистр 13 на входы вычитания поступают сигналы Д и ДУ. В момент срабатывания схемы сравнения 8 регистр 13 должен находиться в нулевом состоянии.

Предмет изобретения Устройство для вычисления функции вида

Z д- Ух + У ,

содержащее два регистра, связанные входами с шинами переменных, а выходами через две грунны схем «И, другие входы которых связаны с выходами двух схем задержки, со входами третьего регистра, причем вход первой схемы задержки связан с первой щиной приращения, а вход второй схемы задержки через третью схему «И, другой вход которой подключен к выходу третьего регистра, - со второй шиной приращений, схему сравнения, логические схемы, отличающееся тем, что, с целью упрощения устройства и новышения надежности его работы, оно содержит четвертый регистр, выходы нервого и второго регистров связаны со входами схемы сравнения, выход которой связан со входами четвертой группы схем «И, другими входами связанных с выходами второго регистра, а выходами - с выходными щинами устройства; другие выходы схем задержки связаны со входами третьего регистра; входы четвертого регистра связаны с двумя шинами переменных, нервой шиной приращений и с выходами третьей схемы «И.

-Г

п-Чз: Г

13

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный цифровой коррелятор | 1984 |

|

SU1290352A1 |

| Многоканальный интерполятор для программного управления многокоординатным станком | 1978 |

|

SU746429A1 |

| Генератор векторов | 1985 |

|

SU1278926A1 |

| Устройство для извлечения квадратного корня | 1986 |

|

SU1399732A1 |

| Многоканальный цифровой коррелятор | 1983 |

|

SU1211753A1 |

| Устройство для определения оптимальных траекторий | 1983 |

|

SU1223240A1 |

| Устройство для считывания графической информации | 1973 |

|

SU667976A1 |

| Генератор векторов | 1981 |

|

SU1010646A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1980 |

|

SU911504A1 |

| Интерполятор | 1987 |

|

SU1413602A1 |

1В

«т

лу

Даты

1973-01-01—Публикация